FPGA很少出现在消息当中,但英特尔在2015年的Altera收购将技术牢牢地推向头条。英特尔购买Altera的主要原因是提供一种加速其至强处理器性能的方法,广泛应用于数据中心。但英特尔并没有成为唯一一家将注意力转移到FPGA中使用FPGA的公司;早在2015年,微软表示,Project Catapult使用Altera的Arria 10 FPGA来提升数据中心的功率/性能。

微软研究员道格·伯格(Doug Burger)当时说道:“我可以想象,十年以后,将应用程序编译成可编程硬件和可编程软件的结合是很常见的。这是一个彻底的转变,将提供持续的业绩改善。“

FPGA开发商Achronix的销售总监Steve Mensor表示:“所有公司都在加速器技术,因为数据中心基础设施由于数据和安全问题的增长而陷入僵局。 FPGA将在诸如非结构化搜索等应用中占主导地位,英特尔预计其至强处理器的30%将在FPGA中集成FPGA加速,或者在不久的将来将会成为芯片。“

有几个原因,为什么FPGA被证明是有吸引力的硬件加速器。 Mensor指出:“它们将功能分成较小的部分,并且在添加CPU时,性能不会线性缩放。

相比之下,硬件加速器是并行的。它们可以在单个时钟周期内完成整个功能,并在添加加速器时执行性能指标。“

目前,微软在Project Catapult中采用的并且目前正在被英特尔应用的方法是使用FPGA技术作为协处理器;独立或集成在一个包中。 Achronix建议将FPGA技术集成到其他设备中。在Mensor的观点中:“嵌入其他设备的FPGA技术的概念已经讨论了二十年,但从未被交付过。 2000年,IBM利用Virtex-2 FPGA尝试了这些方面的事情; LSI Logic在此之前做了一些事情,但没有发现。嵌入式FPGA的概念非常有吸引力,但为什么没有发生?

Mensor的答案是,为了成功嵌入FPGA技术,开发人员需要FPGA设计专长以及IP集成专长。 “为了成为FPGA专家,”他继续说,“你需要很多客户,因为每次都是一个学习经历。同时,IP整合需要零风险。“

Achronix认为它在两个元素中都有必要的专业知识,并推出了Speedcore;嵌入式FPGA(eFPGA)技术。基于Speedster 22i FPGA中部署的相同架构,Speedcore IP可以集成到客户的SoC中。

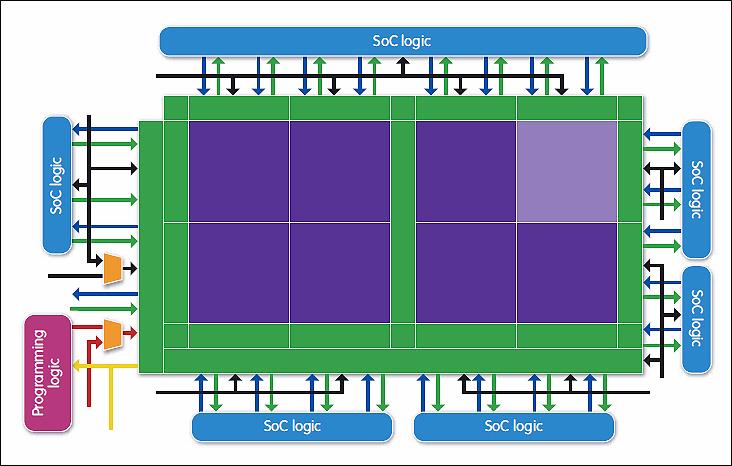

Achronix eFPGA的示例实例化

Mensor指出:“这是Achronix宣布的最大的事情。该技术已经向客户运送,我们获得了良好的反馈。“

Speedcore据说通过提供与SoC的直接连接以及通过将FPGA元件调整到客户的特定要求来提供更低的功耗。更高的接口性能可以降低延迟,并且由于Speedcore元件小于单独的FPGA,所以可以减少电路板尺寸和层数。其他优点被认为包括隔离抗噪声和ESD保护。

该公司声称Speedcore可以将数据带宽提高10倍,同时将延迟降低到相似的数量。 Mensor补充说,功耗可以降低50%,同时显着降低产品成本。

Achronix声称指挥FPGA设计和IP集成的一个原因是因为该方法用于开发其Speedster 22i FPGA。 “当我们构建22i时,”Mensor解释说,“FPGA逻辑设计是在Santa Clara进行的,而班加罗尔的一个团队设计了I / O环。班加罗尔团队随后整合了逻辑核心。“

据Achronix介绍,Speedster 22i需要从五家供应商集成SERDES,以太网,PCI Express,DDR3,Interlaken和PLL IP。 “你需要做到这一点,”Mensor继续说。 “而且Achronix已经完成了自己的SoC整合。”

FPGA很少出现在消息当中,但英特尔在2015年的Altera收购将技术牢牢地推向头条。英特尔购买Altera的主要原因是提供一种加速其至强处理器性能的方法,广泛应用于数据中心。但英特尔并没有成为唯一一家将注意力转移到FPGA中使用FPGA的公司;早在2015年,微软表示,Project Catapult使用Altera的Arria 10 FPGA来提升数据中心的功率/性能。

FPGA开发商Achronix的销售总监Steve Mensor表示:“所有公司都在加速器技术,因为数据中心基础设施由于数据和安全问题的增长而陷入僵局。 FPGA将在诸如非结构化搜索等应用中占主导地位,英特尔预计其至强处理器的30%将在FPGA中集成FPGA加速,或者在不久的将来将会成为芯片。“

有几个原因,为什么FPGA被证明是有吸引力的硬件加速器。 Mensor指出:“它们将功能分成较小的部分,并且在添加CPU时,性能不会线性缩放。

相比之下,硬件加速器是并行的。它们可以在单个时钟周期内完成整个功能,并在添加加速器时执行性能指标。“

目前,微软在Project Catapult中采用的并且目前正在被英特尔应用的方法是使用FPGA技术作为协处理器;独立或集成在一个包中。 Achronix建议将FPGA技术集成到其他设备中。在Mensor的观点中:“嵌入其他设备的FPGA技术的概念已经讨论了二十年,但从未被交付过。 2000年,IBM利用Virtex-2 FPGA尝试了这些方面的事情; LSI Logic在此之前做了一些事情,但没有发现。嵌入式FPGA的概念非常有吸引力,但为什么没有发生?

Mensor的答案是,为了成功嵌入FPGA技术,开发人员需要FPGA设计专长以及IP集成专长。 “为了成为FPGA专家,”他继续说,“你需要很多客户,因为每次都是一个学习经历。同时,IP整合需要零风险。“

Achronix认为它在两个元素中都有必要的专业知识,并推出了Speedcore;嵌入式FPGA(eFPGA)技术。基于Speedster 22i FPGA中部署的相同架构,Speedcore IP可以集成到客户的SoC中。

Achronix eFPGA的示例实例化

Mensor指出:“这是Achronix宣布的最大的事情。该技术已经向客户运送,我们获得了良好的反馈。“

Speedcore据说通过提供与SoC的直接连接以及通过将FPGA元件调整到客户的特定要求来提供更低的功耗。更高的接口性能可以降低延迟,并且由于Speedcore元件小于单独的FPGA,所以可以减少电路板尺寸和层数。其他优点被认为包括隔离抗噪声和ESD保护。

该公司声称Speedcore可以将数据带宽提高10倍,同时将延迟降低到相似的数量。 Mensor补充说,功耗可以降低50%,同时显着降低产品成本。

Achronix声称指挥FPGA设计和IP集成的一个原因是因为该方法用于开发其Speedster 22i FPGA。 “当我们构建22i时,”Mensor解释说,“FPGA逻辑设计是在Santa Clara进行的,而班加罗尔的一个团队设计了I / O环。班加罗尔团队随后整合了逻辑核心。“

据Achronix介绍,Speedster 22i需要从五家供应商集成SERDES,以太网,PCI Express,DDR3,Interlaken和PLL IP。 “你需要做到这一点,”Mensor继续说。 “而且Achronix已经完成了自己的SoC整合。”

据说还有一个好处是减少所需的空间。 “高端FPGA很大,”Mensor观察到,“但FPGA逻辑仅占芯片尺寸的50%。将FPGA逻辑插入SoC意味着您可以构建更小的器件。“他补充说,与此同时,较小的器件可能会减少PCB层的数量。他建议说:“FPGA可能需要16层以上的路由,信号完整性也将得到改善。”

Mensor指出,FPGA逻辑元件可以是任何尺寸的。 “尽管有最小尺寸的8000查询表(LUT),我们有Speedcore的客户设计的核心范围从50,000到150,000 LUTs。而这些延迟为2ns,而FPGA中的延迟为30至50ns。“

因为Speedcore eFPGA是嵌入式IP,它不包括可编程I / O;相反,它的目的是被最终用户的ASIC完全包围。

面对FPGA设计过程中的挑战,Achronix开发了Speedcore eFPGA编译器,旨在支持客户特定IP的快速开发,以及允许创建不同大小的FPGA内核的模块化架构。

“有一些设计规则规定了每个可用资源的最小和最大相对数量,”Mensor说,“但是我们的模块化架构允许将块以”lego“的方式放在一起。”可用的块有:块RAM,每个块最多20kbyte;逻辑RAM,每块最多4kbyte,一个具有18×27乘法器的64位DSP,一个64位累加器和一个27位预加器;和四个输入LUT。此外,客户可以定义Speedcore宽高比和I / O端口连接。

“施工规则在Speedcore Builder工具中进行管理,”Mensor说。

虽然Achronix与英特尔公司签署了代工协议,但是它能够使其Speedster 22i FPGA采用14nm FinFet流程,而且还将以TSMC 16FFT +工艺制造的格式提供Speedcore。而且,由于FinFET晶体管寿命长,所以包括了技术,以确保其均匀。 “我们目前有客户为TSMC流程设计,”Mensor指出,“但客户可以选择他们制造SoC的地方。”

Speedcore IP以GDSII格式提供,以便客户将其集成到其ASIC中。 Achronix还提供ACE设计工具,将设计编译成Speedcore eFPGA。

全球销售副总裁Steve Dodsworth总结说:“显然需要更多的FPGA集成,这就是Speedcore所关心的。任何不在英特尔世界的人都会对这项技术感兴趣。“