本文为明德扬原创文章,转载请注明出处!

一、SDRAM数据总线属性

下图为SDRAM的某一接口时序图,我们可以看到,读和写占用的都是DQ这个数据总线,对于SDRAM来说,只有一根数据总线,那么当我们需要用这根线读取数据的时候,读出来的数据占用了总线,这个时候是必然无法写入数据的,同样的在写数据的时候也无法进行读数据的操作。

二、SDRAM同时读写需求

虽然SDRAM具有不可同时读写的属性,但是在一些项目中需要写入的数据和读出的数据都是连续的。比如在边缘检测的工程中,摄像头一直在传出数据,并且送到VGA的图像数据也不能断,这时我们既要将摄像头传出的数据写到SDRAM,又要从SDRAM读出数据并在VGA显示。因此实际工程中时需要SDRAM同时实现读数据和写数据功能的。

前面我们也分析过SDRAM的接口时序图,明确DQ总线只能进行读数据或者写数据,不能同时进行读写数据,那么如果遇到上述情况,就需要我们在SDRAM固有属性的基础上来解决问题。

三、“伪同时读写”的原理

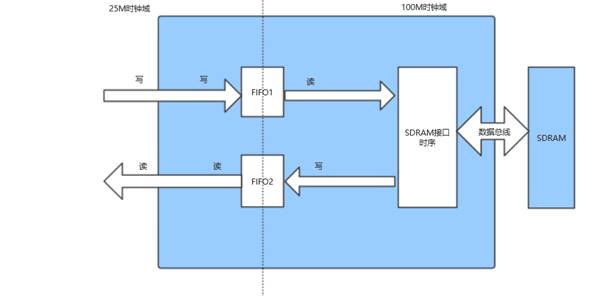

既然SDRAM的属性不变,那么我们可以在SDRAM时序前面加两个FIFO,SDRAM接口时序和SDRAM硬件之间由一根数据总线DQ相连,如下图所示。

FIFO是在FPGA中比较常用的存储器,FIFO写入和读出都由时钟控制,而且可以用不同的时钟,那么当读出的时钟大于写入时钟的时候,我可以一直往里面写,但是由于读出的速率要快,那就不必要一直读,FIFO的深度越深,我就可以等待越多的时间。

上图结构中,设置FIFO左边时钟是25M,右边时钟为100M。写命令和写数据先保存到FIFO1中,读命令保存到FIFO2中,在SDRAM接口时序里面,会判断FIFO1和FIFO2中谁有数据,谁有数据就执行哪个命令;如果都同时有数据,那工程师可以决定一个优先级,选择其中一个命令执行。而没有选中的命令,则保留到FIFO中缓存,等候被选中执行。

简单来讲就是数据都暂时的存在FIFO中,FIFO左边和右边的工作时钟不同,同样一组数据,如果左边读写数据都需要一个时钟,那么右边读写数据就需要四倍时钟即四个时钟。这样一来,看FIFO右侧的接口,永远都是要不就是写,要不就是读,DQ不会被读写同时使用(也就是读写不同时)。而在左侧的接口看来,写命令和读命令是可以同时有效的(也就是读写同时)。

有的朋友会讲,这种方法并不是真正的同时读写呀。其实,能不能同时读写,是在不同的时间精度来看待的。例如右侧的接口,在某一个时钟沿看来,其状态不是读就是写,无法实现读写同时;但如果把时间拉长,例如在1秒的时间内来看,在这一秒钟内既有读数据状态,又有写数据,就会令我们感觉到它是可以同时读和写的。将这样一个结构当作一个整体来看,可以认为实现了SDRAM的同时读写,我们将其称之为“伪同时读写”。

其实这种“伪同时读写”我们还是经常会遇到的。例如电脑CPU,众所周知,它是串行执行指令的,一次只能处理一个指令。但我们在使用电脑时,可以感觉到QQ、浏览器和电影是同时工作的,这也就是时间精度的问题。

四、现实案例

学会了利用FIFO的存储特点来实现“伪同时读写”,我们也就解决了最开始提到的SDRAM在边缘检测中实现同时读写的问题。我们在写侧接收的像素数据在25M时钟域的,在FIFO1的读侧是100M的时钟域,读写速率相差4倍,当FIFO缓存一定量的数据之后,就读出来写到SDRAM中,写完之后,就可以利用FIFO1读写的时间差,来将SDRAM中的数据读出,然后再放到一个写侧时钟100M,读侧时钟25M的FIFO2中,就可以保证FIFO2一直有数据读出,而FIFO1又一直有数据写入。这样以来就实现了摄像头一直采集数据并且一直有数据传输到VGA。

以上就是通过FIFO实现SDEAM同时读写的解决方案,更多关于FPGA的欢迎加Q:1817866119(N老师)进行交流讨论!