DDR SDRAM的发展背景:

DDR SDRAM是Double Data Rate SDRAM的缩写,即双倍速率同步动态随机存储器,大家习惯称为DDR。最早是由三星公司于1996年提出,后由日本电气、三菱、富士通、东芝、日立、德州仪器、三星及现代等八家公司协议订立内存规格,并得到AMD、VIA与SiS等主要芯片厂商的支持。

图1:DDR内存

但DDR不同于SDRAM,而是在SDRAM的基础上发展而来的,仍然沿用了SDRAM生产体系,但是SDRAM是在一个时钟周期内只传输一次数据(仅上升沿传输),但是DDR内存则是一个时钟周期内传输两次数据(上升沿和下降沿各传输一次数据),因此称为双倍速率同步动态随机存储器,可见,可以在相同的总线速率下达到更高的数据传输率。现在DDR运行频率主要有100MHz,133MHz,166MHz三种,且以及从DDR2,DDR3发展到DDR4,频率也由DDR3的1600MHz上升到DDR4的2133MHz,而且凭借新的电路架构最高可以达到3200MHz。现在处于DDR3主流时期,许多平板电脑内部都采用DDR3,使得电脑的运行速度也因此大大提高。

FPGA+HBM:

上周四上午,xilinx发布了四款高性能的Virtex UltraScale系列FPGAs,此FPGA采用16nm工艺,同时内嵌32位或64位的HBM(high-bandwidth memory)DRAM,使得此FPGA的传输效率相对于DDR SDRAM提高了20倍 ---完全可以与400G的以太网匹配,此外还有多个8K数据视频通道,或服务于云服务器的高性能硬件加速器。

这些新的Virtex UltraScale+HBM设备都属于Xilinx 3D FPGAs系列第三代产品,此Xilinx 3D FPGA系列开始于2011年,最先发布的是Virtex-7 2000T(详见Generation-jumping 2.5D Xilinx Virtex-7 2000T FPGA delivers 1,954,560 logic cells using 6.8 BILLION transistors (PREVIEW))。同时,Xilinx也将TSMC与3D IC技术结合在一起共同发展。现在,Virtex UltraScale+HBM设备代表了当前成果的艺术状态。

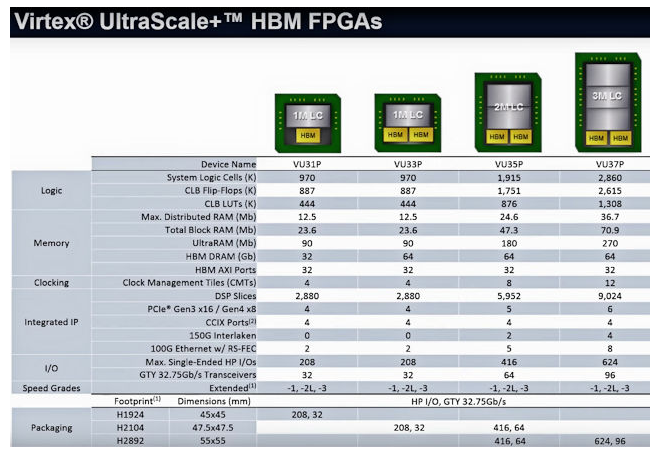

下表显示了这四款Virtex UltraScale+HBM设备的突出特点:

图2 Virtex UltraScale HBM FPGA

以上这四款设备内部都内嵌了32/64位HBM SDRAM,通过多于1000根I/O线将HBM堆直连到逻辑设备,在硅部分中包括一个硬件HBM存储控制器,管理一个或两个HBM设备。这些控制器有32个高性能的AXI通道,允许高带宽连接到Virtex UltraScale+设备的可编程逻辑部分,而且在FPGA结构中有许多选择途经的通道,任意一个AXI端口都可以寻址到HBM设备的物理存储地址中。

此外,在这些Virtex UltraScale+HBM FPGAs中,xilinx 第一次提供了新的高性能CCIX cache一致性接口(上个月发布,详见CCIX Consortium develops Release1 of its fully cache-coherent interconnect specification, grows to 22 members),这里CCIX通过提供low-lattency、高带宽、完全一致性存储服务接口来简化超大规模数据中心卸载加速器的设计,同时采用一个完全一致性协议和ISA-agnostic子集,使得协议独立于附加处理器架构和指令集。而且CCIX对与HBM和新的xilinx UltraScale+HBMFPGAs采用一套封装。

为什么是Xilinx UtraScale 系列呢?

小编认为就xilinx的FPGAs系列中,UltraScale系列采用全新 的16nm及20nm工艺,首款ASCI-Class全可编程架构,不仅覆盖从平面到FinFET技术乃至更高技术的多个节点,同时还可从单片IC扩展至3D IC,不仅支持数百Gb级的系统性能,在全线路速度下还支持智能处理,同时将全新存储器、3D-on-3D和多处理SoC技术完美结合,实现了领先一代的价值。

总结:

在xilinx Virtex UltraScale+HBM FPGAs设备中,具有可编程的系统集成,更高的系统性能,较低的BOM消耗,较低的整体功耗,加速器设计能力,以及上文中重点介绍的高速存储带宽,所有这些性能的提高都预示Xilinx FPGA将会走的更远,用的更广。

原文出处:http://xilinx.eetrend.com/news/10684