本文为明德扬原创文章,转载请注明出处!

FPGA,现场可编程门阵列。最近几年,FPGA可以说是热门行业,人工智能,NFV/SDN,数据分析,媒体处理,5G,ADAS等概念兴起,FPGA在这些兴起火爆的领域的运用越来越广。市场上对于FPGA的从业人员需求大大增加,很多在校学生与企业的工程师们,都想进入此领域学习以及从业。对于刚刚入坑FPGA的朋友们,如何快速入门,提起兴趣,是迫切需要的事情。FPGA开发本质上也是硬件开发,运用HDL描述出自己所需要的功能,由综合工具综合出电路后在FPGA内部布局布线,最终生成可运行的比特率文件,所以拥有一款开发板来用于学习,是初学者必不可少的工具。

近年来FPGA开发有向于高级语言化开发的趋势,但是目前市场的大量需求还是传统的数字通信,高速逻辑接口等开发应用为主。所以目前网上可购买的FPGA开发板都是以高速逻辑接口等应用为主的开发板。今天就跟大家分享一下新手如何选择FPGA开发板。选择开发板,性能,外设当然是第一要素了,FPGA开发板的性能最主要的就是看FPGA芯片了。

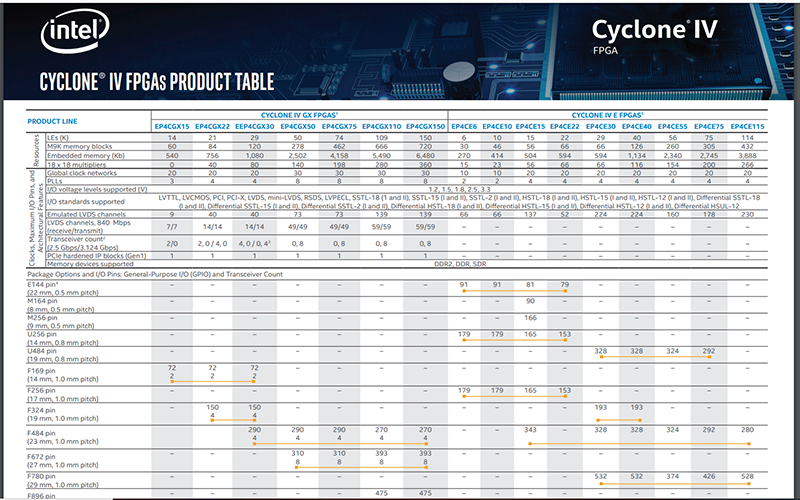

首先我们知道,ALTERA 的FPGA内部逻辑资源是由逻辑单元(LEs),嵌入式RAM(embedded memory),M9K存储块(M9K memory blocks),可编程互连单元,可编程I/O资源,PLLs等构成的。目前市场上的FPGA入门开发板,也是以ALTERA(已经被Intel收购)的cyclone IV E系列为主,当然也有一些开发板用的是cyclone III跟cyclone II,我们本着买新不买旧的原则(老产品线ALTERA公司停产了,目前在市面上流通的基本上都是翻新芯片),这里就不予赘述了。对于ALTERA cyclone IV E系列介绍表格,我们可以得到型号EP4CExx, xx在这里表示LEs 数量,数量级是K,拥有更多逻辑单元,在设计复杂的工程时,需要采用大量的逻辑单元的开发时,拥有的设计思路就多,选择也多。

ALTERA cyclone IV系列

在设计复杂的工程时,某些硬件模块资源不够时(例如M9K),我们可以有退路使用HDL编写自己的存储单元来用于工程使用,当然这种做法会消耗大量的逻辑单元,且与存储深度,存储位宽正相关。目前

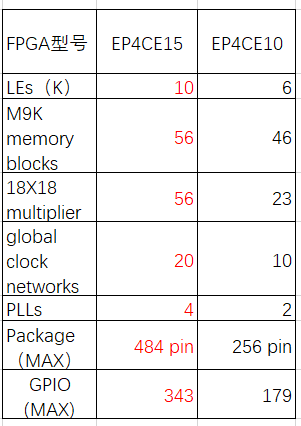

市面上都是采用EP4CE10,10k个逻辑单元,市面上比较火的一些开发板,采用的都是这一块芯片,而明德扬MP801采用的则是EP4CE15,EP4CE10咋看之下跟EP4CE15相差就只有5K个逻辑单元,但实际情况下,EP4CE10与EP4CE6只是简单的量变,而EP4CE10跟EP4CE15就是质变情况了,从上面的表格中两者相差的主要就是内部硬件块,M9K memory,embedded memory,硬件乘法器,全局时钟网络,PLLs,数量相差甚远,且这些模块才是FPGA开发中比较重要的资源。举个例子,对于M9K资源,FPGA在做数据处理的时候,在高速接口数据收发经常会采用输入与输出的接口类型不一致,以达到桥接的效果,在这些应用下输入数据与输出数据要做到带宽匹配,需要采用FIFO缓存,这里需要使用的M9K资源就与输入输出的带宽差异有关,差异越大,资源使用情况越多,FIFO是FPGA开发当中使用频率很高的逻辑。

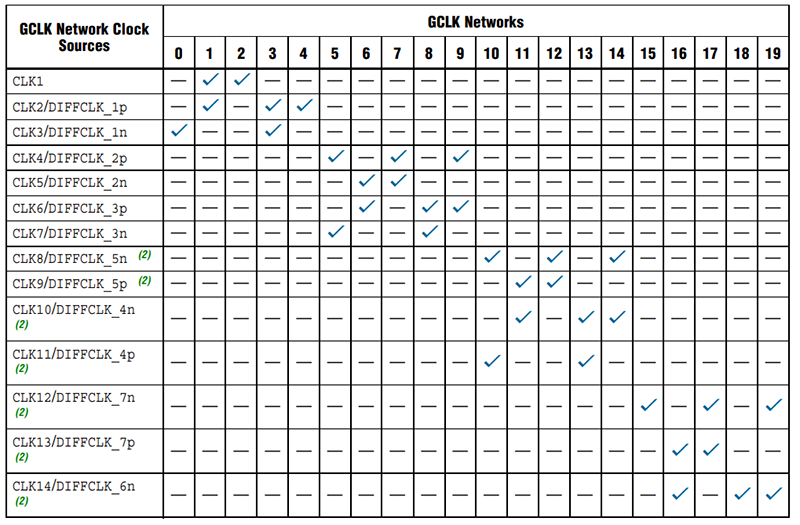

全局时钟网络也是比较关键的资源,对于外部高速数据输入的随路时钟,我们在FPGA内部数据处理的时候,会采用这个随路时钟作为各个数字逻辑的触发时钟,全局时钟网络在FPGA内部到达每一个逻辑单元时间是同步的,这样就减少了时钟偏斜,在FPGA 数字设计中,时序是一定要考虑的一个问题,且每个数字逻辑互联的时候,都会存在delay,这与PCB跟电缆中的传输延时类似,降低了工程时序约束的难度(这一块内容建议B站搜索明德扬时序约束视频查看)。

ALTERA cyclone IV E 全局时钟网络分配

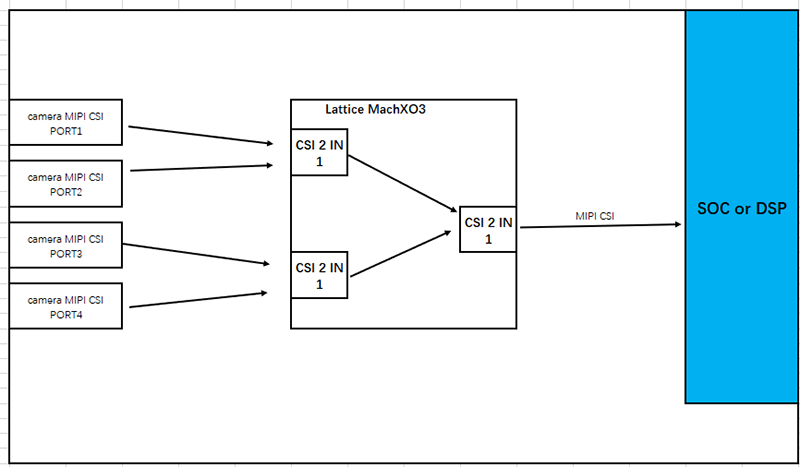

最重要的功能就是全局时钟网络还可以夸时钟区域(FPGA一般一个BANK为一个时钟区域),很多工程,内部逻辑往往需要跨时钟区域,这在高速接口的工程当中就是如此应用的,比如下面的明德扬MIPI CSI 4合1案例,4 port的MIPI CSI输入,用一个BANK的IO是接收不了的,而且还需要增加的发送端模块,就需要增加BANK。

明德扬MIPI CSI-2 4合1案例

还有一个很明显的差距,EP4CE10跟EP4CE15的PLLs,EP4CE15是有4个,而EP4CE10才只有一半。PLLs可以让外部基准时钟输入倍频,移相等操作,为数字逻辑系统提供需要且稳定的系统时钟,因为我们的工程往往需要多个数字系统,拥有更多的PLLs的EP4CE15系列在这真的是优势明显。

EP4CE10跟EP4CE15资源对比

EP4CE10跟EP4CE15差距远不只此,EP4CE10最高规格只到256pin,GPIO为179个,而明德扬MP801开发板使用的FPGA型号EP4CE15F23C8N,为484pin规格,具有343个GPIO。这里我们可以知道市面上比较火的一些开发板采用的都是EP4CE10,256pin规格,在内部逻辑资源,硬件资源对比EP4CE15差距巨大的情况下,GPIO资源也是差距巨大。所以同样都是采用ALTERA cyclone IV E,性能差距可见一斑。

当然,选开发板,不仅仅要考虑FPGA的性能资源,外设也是必须考量的情况之一。板载内存这一块,得益于IO数量的优势,明德扬MP801采用了三片16位位宽,存储深度为256Mbit SDR SDRAM,一些火爆开发板都是只有一片,这一点MP801在入门级FPGA开发板市场中完胜。

高速外设这一块,MP801板载1000M以太网PHY芯片RL8211,而高速AD/DA业界独有的板载,

高速ADC 是AD9280,拥有20MSPS速率;高速DAC是AD9709,拥有125MSPS速率。再看市面上火爆的开发板都是100M以太网;

一些开发板甚至需要另外购买AD/DA模块,还有一些开发板只有500KSPS的ADC,1MSPS的DAC,可以说对于高速开发学习这一块,MP801又是完胜。

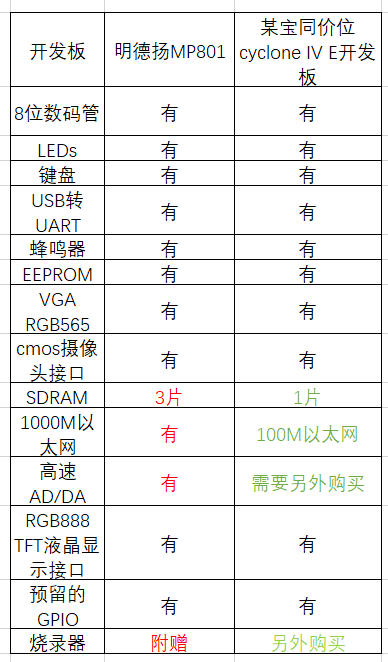

在下面图表1中,我们可以看到列出来的各种外设中,8位数码管、LEDs、USB转UART、蜂鸣器、EEPROM、VGA RGB565 、CMOS摄像头等对于初学者入门学习非常有帮助的外设都一一俱全。图表只是列举,并未一一列全。

初学者在入门以后,这些外设对于提高自己的应用于开发能力特别重要,到了提高阶段,如果又要重新购买更高级的开发板,这对自己的学习进度来说可不是什么利好关系;我们刚了解好这款FPGA的架构等信息的时候,被迫更换FPGA学习,又是一个漫长的学习理解过程,这对于新手小白来讲是痛苦又艰难的。最重要的是,淘宝爆款开发板再加了烧录器后的价格,竟然都差不多,因为MP801是有包含烧录器、摄像头、超6类网线的。这对学生党来说可是个利好消息,同样的价位,可以获得更高端的性能与外设。

图表 1

所以,初学者不仅仅要考虑选择比较容易上手的开发板,更需要拥有更强大性能外设的开发板,这样才可以在提高阶段拥有更好,更快速的学习过程。

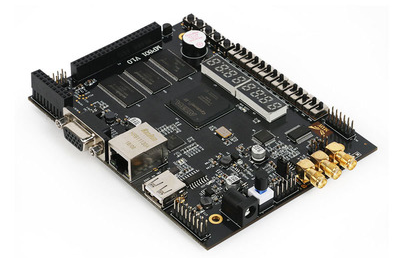

明德扬MP801开发板

想要了解更多FPGA开发板相关知识的朋友可以在下方留言,我们互相讨论互相交流!