MIPI CSI-2项目之MIPI协议介绍

本文为明德扬原创文章,转载请注明出处!作者:鱼丸粗面

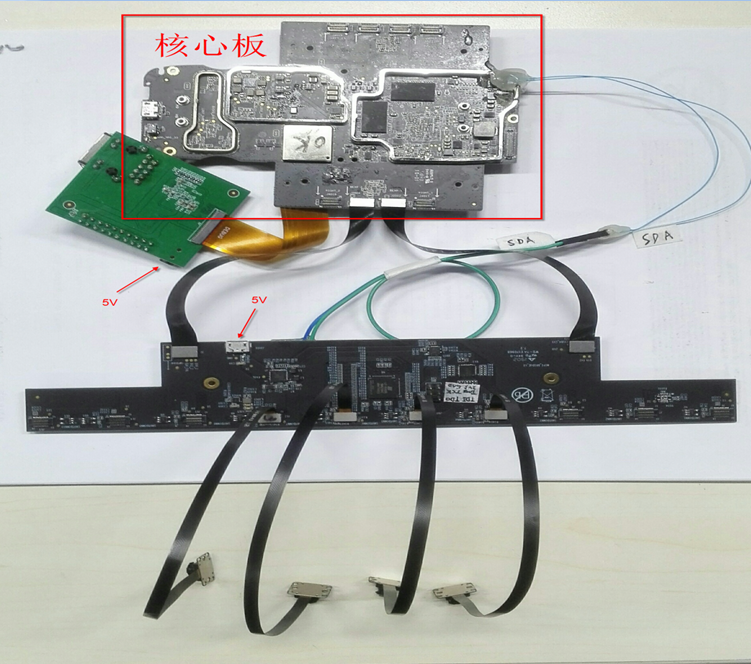

在我们的MIPI多路摄像头拼接项目中,需要用到MIPI通信协议,此项目包含核心板一块,核心板供电板(绿色)一块,AR0144摄像头4枚,能够实现4路MIPI图像数据,每2路做左右拼接后,得到2路摄像头数据,再按MIPI CSI协议发送给海思方案芯片。主要功能包括D-PHY协议解析、CSI协议解析、图像拼接、CSI协议打包和D-PHY协议打包等。

下面简单的介绍一下MIPI协议:

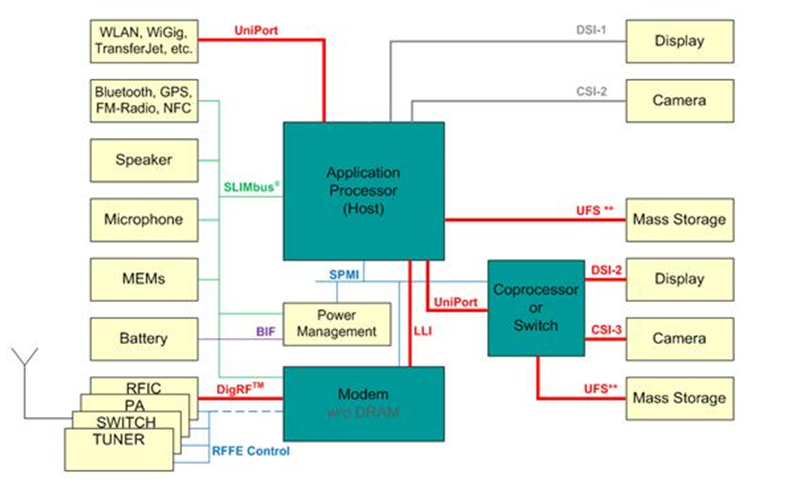

MIPI (Mobile Industry Processor Interface) 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。下图是按照 MIPI的规划下一代智能手机的内部架构。

图2 MIPI下一代智能手机内部框架

MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。以DSI为例,其协议层结构如下:

图3 DSI协议层

CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。

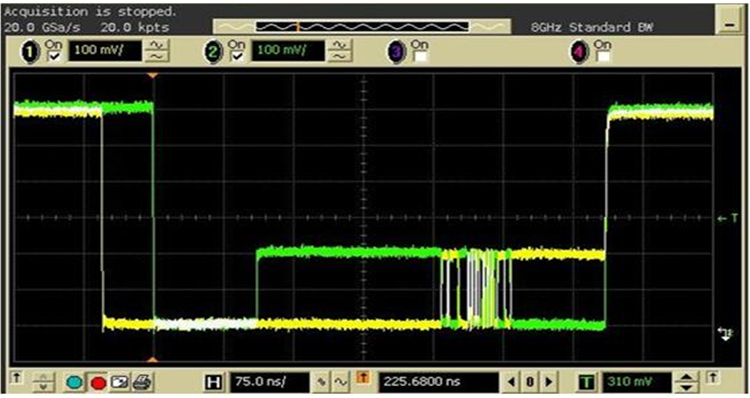

PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps);LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。两种模式的结合保证了MIPI总线在需要传输大量数据(如图4)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。下图5是使用示波器捕获的MIPI信号,可以清楚地看到HS和LP信号。

图4 两个数据通道PHY配置

图5 示波器捕捉到的MIPI信号

PHY由D-PHY (Lane模块)组成,PHY可能包含低功率发射机(LP-TX)、低功率接收器(LP-RX)、高速发射机(HS-TX)、高速接收机(HS-RX)、低功耗争用探测器(LP-CD)。其三种主要的通道类型分别为时钟通道、单向数据通道和双向数据通道。时钟通路分为主时钟路(HS-TX、LP-TX)和从时钟路(HS-RX、LP-RX);单向主数据通道分为(HS-TX、IP-TX)和从数据通道(HS-RX、LP-RX);双向数据通道主/从机分为:HS-TX, HS-RX,LP-TX, LP-RX, LP-CD。

图6 通用Lane模块架构

MIPI 还是一个正在发展的规范,其未来的改进方向包括采用更高速的嵌入式时钟的M-PHY作为物理层、CSI/DSI向更高版本发展、完善基带和射频芯片间的 DigRF V4接口、定义高速存储接口UFS(主要是JEDEC组织)等。明德扬掌握基于MIPI协议的多路视频合成工程,感兴趣的朋友可以加QQ 3358622769与我进行更加深入的讨论!