LVDS视频拼接GDDR7:1 IP核生成例化

本文为明德扬原创文章,转载请注明出处!作者:鱼丸粗面

由多个数据位和时钟组成的源同步接口已成为电子系统中移动图像数据的一种常用方法。比较流行的标准是7:1 LVDS接口(用于通道链路、平面链路和摄像机链路),它已经成为许多电子产品的通用标准,包括消费设备、工业控制、医疗和汽车远程信息处理。在这些应用中,使用低成本FPGA进行图像处理的做法已经变得相当普遍。特别是LatticeXP2™、LatticeECP2™、LatticeECP2M™和LatticeECP3™非常适合支持7:1 LVDS标准。

在明德扬的一个车载视频拼接的项目中,主机收发的视频信息是通过LVDS信号进行数据传输,这就需要有一个LVDS接口模块来进行数据的交互,其中就需要使用到GDDR7:1 IP核。该接口用于实现7:1 LVDS接收接口,使用ECLK实现7:1的速率变换。ECLK是慢速时钟进来后使用锁相环倍频3.5倍后的时钟,此时钟用于捕获接收器IDDRX71模块上的数据。接下来我来详细介绍此IP核的生成以及例化的过程:

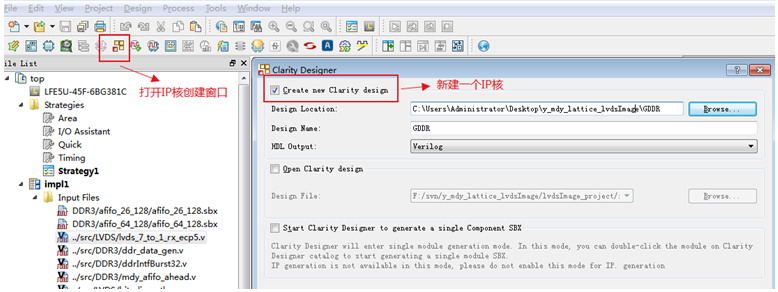

首先,创建一个新的IP核:

找到gddr7:1 IP核并进行gddr7:1 IP核创建:

图2 创建gddr7:1 IP核

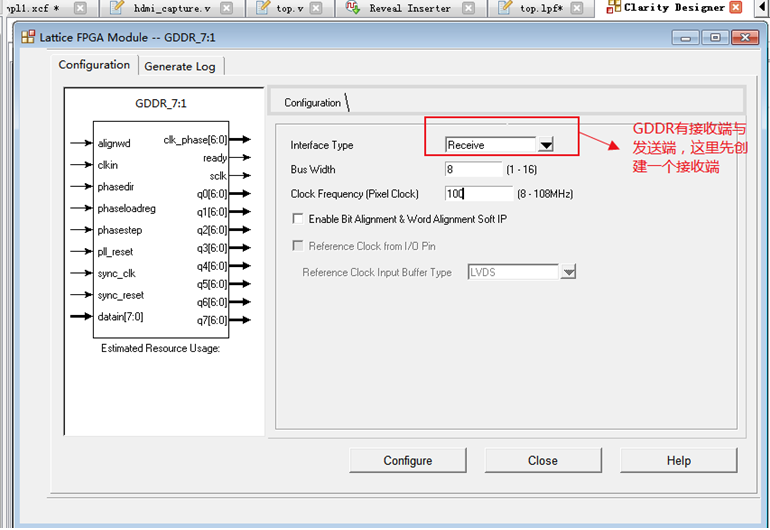

由于需要8Lane差分信号输入,因此Bus Width长度设置为8,输入慢速时钟频率设置为100M:

图3 gddr7:1 接收端设置

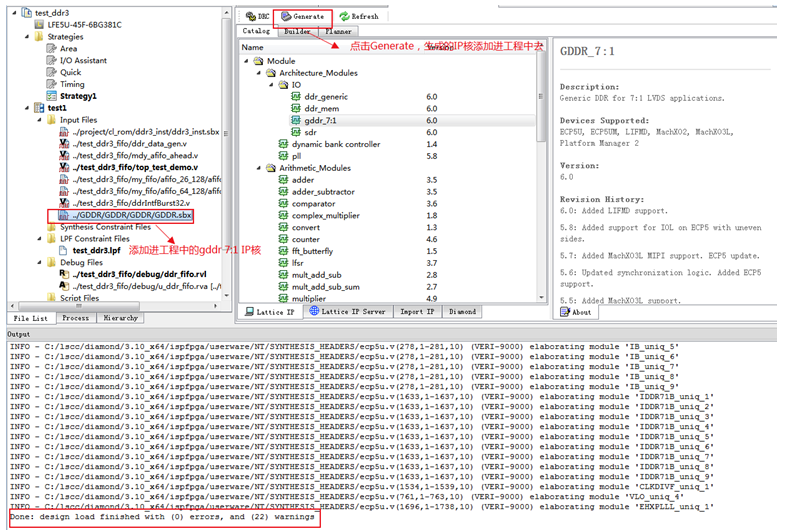

IP核生成成功后,点击Generate,即可将生成后的IP核添加进工程中去:

图4 gddr7:1 IP核添加进工程

LVDS串行数据输入进FPGA,经过解串之后还要有同步字操作,用于数据的World Align、Bit Align,找到数据的起始位,解串后的并行数据进行一系列操作后需要再转换为串行数据输出,这时候需要再次例化一个gddr7:1 IP核:

图5 gddr7:1 发送端设置

生成gddr7:1发送端后,点击Generate将生成的IP核添加进工程中去。

至此,LVDS的加解串IP核添加完成。如有不明白的地方可以加我的QQ:3358622769,我将会具体的向有需要的同学进行指导。期待与大家一起探讨进步!