本文为明德扬原创文章,转载请注明出处!

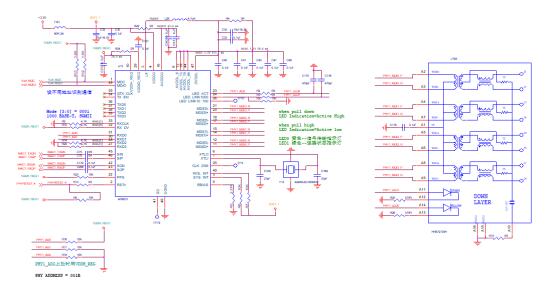

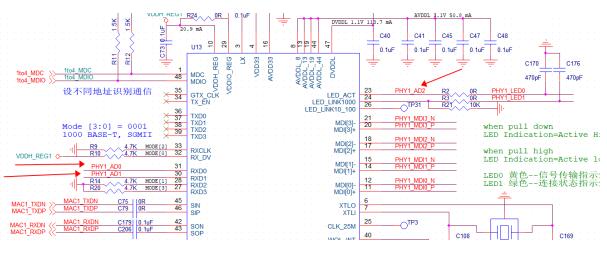

在上一篇的文章中我们对sgmii的数据协议进行了解析,那么本篇我们说一下sgmii的PHY芯片的硬件电路,其电路图如下所示。

上面电路图中的电路电源和地我们就不说了。现在结合数据芯片手册来说说AR8031。

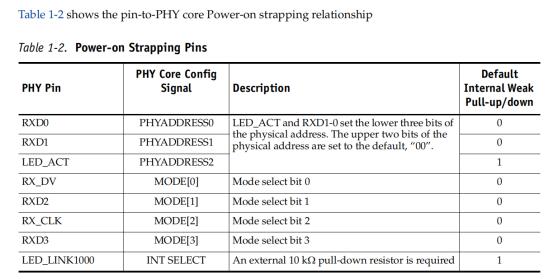

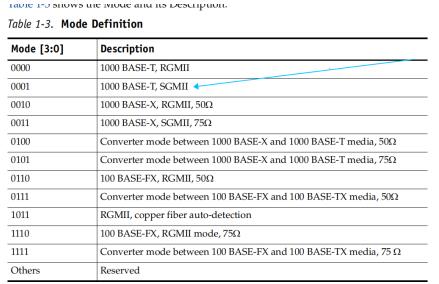

AR8031支持两种模式RGMII模式和SGMII模式,也就是说有两种模式的设计,请参考数据手册的第13页。

一、 Mode模式确定

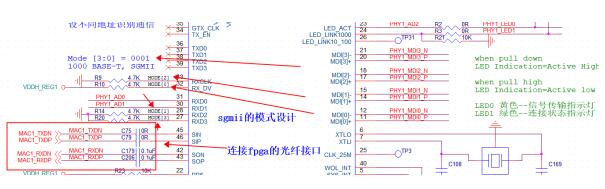

由以上的信息我们可以确定的Sgmii模式是怎么样设计的,如下图所示:

Mode设计为0001,连接FPGA的高速Serdes接口SIN/SIP 和 SON/SOP要经过去耦电容,滤除直流。

二、地址确定

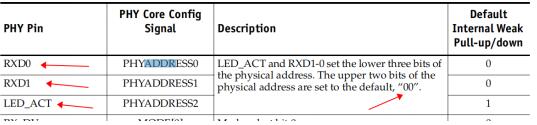

通常以太网PHY芯片都是可以进行寄存器设计的,那么在设计的过程中PHY芯片是有地址的,我们看一下PHY的地址的设计,先看一下数据手册,如下图所示:

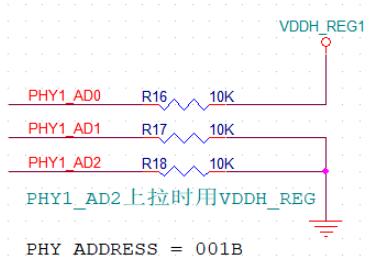

PHY芯片的地址的高两位是00,然后是RXD0, RXD1 ,LED_ACT是由用户自行定义的,在这里我们可以设计如下:

设计的PHY芯片的地址如下图所示:

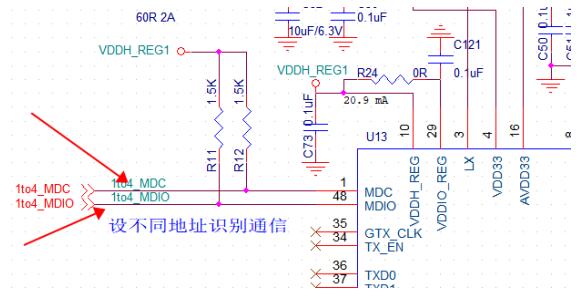

三、PHY芯片的寄存器设计

如何进行PHY芯片的寄存器的设计,主要是通过mdc和mdio进行设计

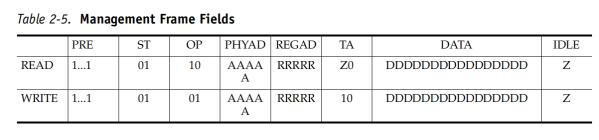

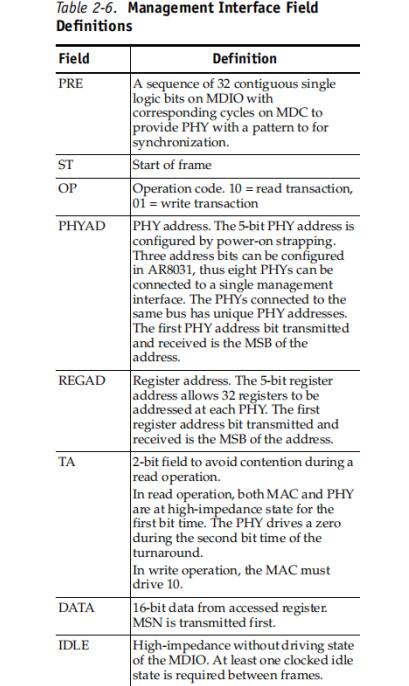

如果要进行mdc和mdio的程序设计,请参考数据手册的24页,如下图所示:

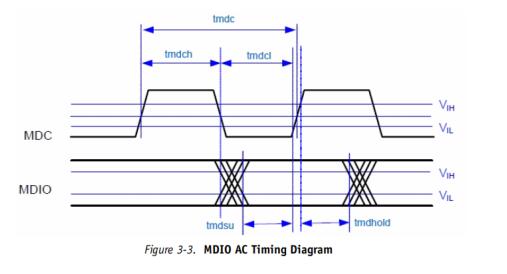

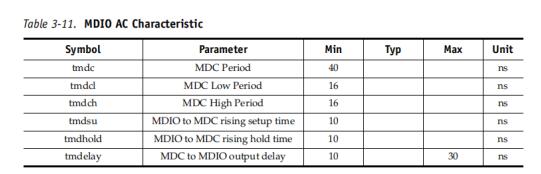

下图为mdc和mdio的建立和保持时间:

Table2-6主要是mdc和mdio要进行多少位的设计,如需要源码的话,可访问以下网址:https://item.taobao.com/item.htm?spm=a230r.1.14.11.368c328dQrUvj9&id=578233289514&ns=1&abbucket=20#detail

以上就是对AR8031设置sgmii的主要硬件电路详解,更多相关知识可以在评论中与我进行讨论!