如果同学们的问题我们帖子里面没有的请第一时间联系易老师微信同步:13112063618,我们对新问题进行补充!

明德扬最近做了抖音系列短视频,感兴趣可以关注明德扬抖音号:FPGA技巧分享(87481069842)至简书籍短视频(74803215644)

内容不断更新!点赞+关注,学习不迷路!

七、综合项目实践课——千兆网项目专题课

【问题7.1】千兆网课程里的udp和百兆网通用的吗?

答:本课程讲述的是千兆网,对于百兆网来说,UDP IP MAC和ARP协议都是相同的,

不同的是MAC IP核、FPGA和PHY芯片的接口不同。

本课程提供的是千兆网的工程,如果要使用百兆网,需要根据上面的内容来修改。

【问题7.2】千兆网课程有实现TCP协议吗?

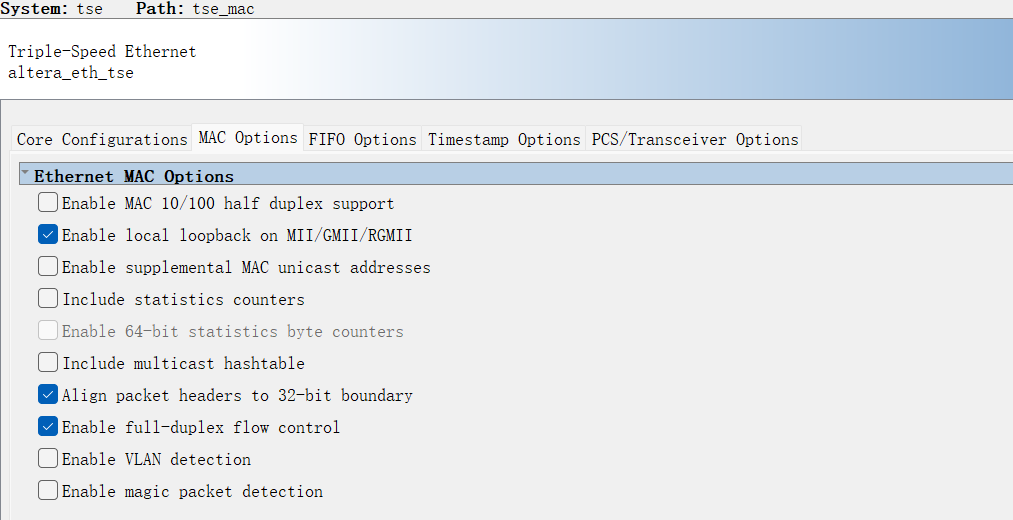

【问题7.3】请问下,三速以太网IP核配置时,32bit对齐选项的意义在哪里?

答:在接口为32bit时,每个VLD有效时的数量是4个字节。由于MAC头是14字节,不是4的整数倍,在发送方向,在补上MAC头后,

必须调整数据(拿出2字节与MAC头最后2字节凑成一个4字节的有效数据),这样处理比较麻烦。 同时道理,接收方向,去掉14字节MAC头后,

会有一个VLD多出2字节的有效数据,这样调整也麻烦。为此,MAC IP核里有一个功能,就是32位对齐功能。该功能决定,在SOP位置时,

最高2字节是否为无效数据。 当是无效数据模式时,发送方向插入2字节无效数据+14字节MAC头;在接收方向,删除前16字节MAC头,剩下就是效数据。这样处理就方便很多了。

【问题7.4】 只要勾选了32bit对齐功能,IP核自动添加2字节的无效数据?

答:勾选对齐后,接收方向将删除无效数据,直接输出数据,即SOP位置的高2字节也是有效的,一直到EOP位置。发送方向,认为从SOP到EOP的位置都是有效的。

不勾选的话,接收方向,IP核输出、SOP位置的高2字节是无效数据。发送方向,进到IP核的数据里,将SOP位置的高2字节视为无效数据。

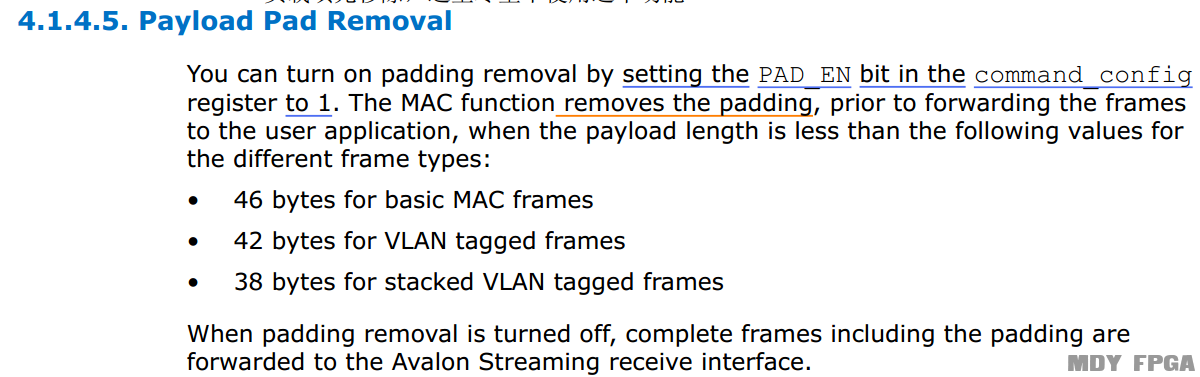

【问题7.5】如下图所示,当使用了PAD_EN功能时,接收方向,会将PAD去掉,但实际上没有去除,是怎么回事?

答:请看下面描述:第一段,当值小于600,该域反映的是长度,才会继续检查PAYLOAD长度,

进而才会有REMOVAL。

当值大于600时,该域反映的是类型而已,则不会REMOVAL。

【问题7.6】课程里会包含TCP协议吗?

答:TCP协议使用逻辑实现非常复杂,所以本课程不会包含此部分内容。

【问题7.7】RGMII支持10M/100M/1000M三种模式吗?

答:RGMII是"吉比特介质独立接口"的含义,即1000M的传输接口。其他几种接口包括GMII、MII等。注意一下,10M/100M/1000M三种模式,指的是该“芯片”支持这三种接口,不是说RGMII支持。

当芯片采用了RGMII或GMII时,就传输1000M;当采用了MII 100M时,就是传输100M。注意的是,RGMII和MII的部分管脚是可以复用的。

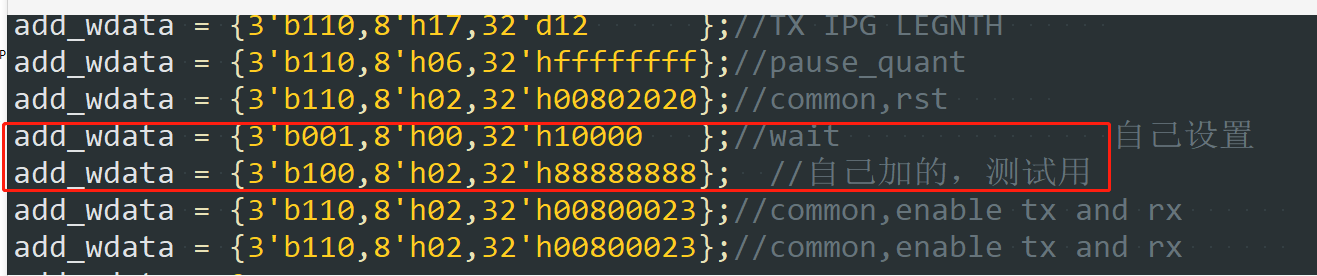

【问题7.8】千兆网配置寄存器的定义代码中,下面两个IP核数据手册中没有说明,是什么作用的?

答:第一行语句的作用是“等待10000个时钟周期”。目的是当完成前面的配置后,等待10000个时钟后,再去配置下面的寄存器。这是因为有时

候,配置完上面寄存器后,有可能要等一段时间才起作用,所以要等一等。这个“等待”功能是FPGA里面代码实现的。

第二句作用是测试使用的,可以删除,在调试时看看接口是否正确。

【问题7.9】本项目有没有配置外部的PHY芯片?

答:本项目是没有配置的,因为默认PHY芯片是不用配置就能正确使用的。

【问题7.10】、百兆网和千兆网的区别是什么?

答:1. IP核是一样的

2. 千兆网使用的是GMII接口,百兆网则是MII接口。gmii数据线是8位;MII接口使用是4位数据线,也就是TXD低4位和RXD低4位。

3. 时钟频率不同,千兆网是125M,百兆网是25M时钟。

4. 百兆网的TX时钟来自于PHY芯片,芯片管脚使用的是tx_clk,而不是gtx_clk。

5. MII接口的4位数据线,是先发1个字节的低4位,再发高4位。

【问题7.11】老师,咱们千兆网项目中,为啥用sharkwire抓包的时候 最大传输速率到不了千兆呢?

答:因为包文传输的时候,会有消耗的,例如包与包之间有帧间隙,并且每个包会有前导码和FCS部分。因此达不到理论的千兆。

【问题7.12】请问一下在千兆网工程里,初始化mac IP核时,signaltapii有些reg_cnt刚开始时,add_wdata会出现一小段莫名其妙的数据,是怎么回事 ?

答:请注意这个signaltap采样的时钟一定要跟代码模块的时钟一致。

SignalTap使用教程:http://old.mdy-edu.com/jishuwenz/2019/1210/107.html

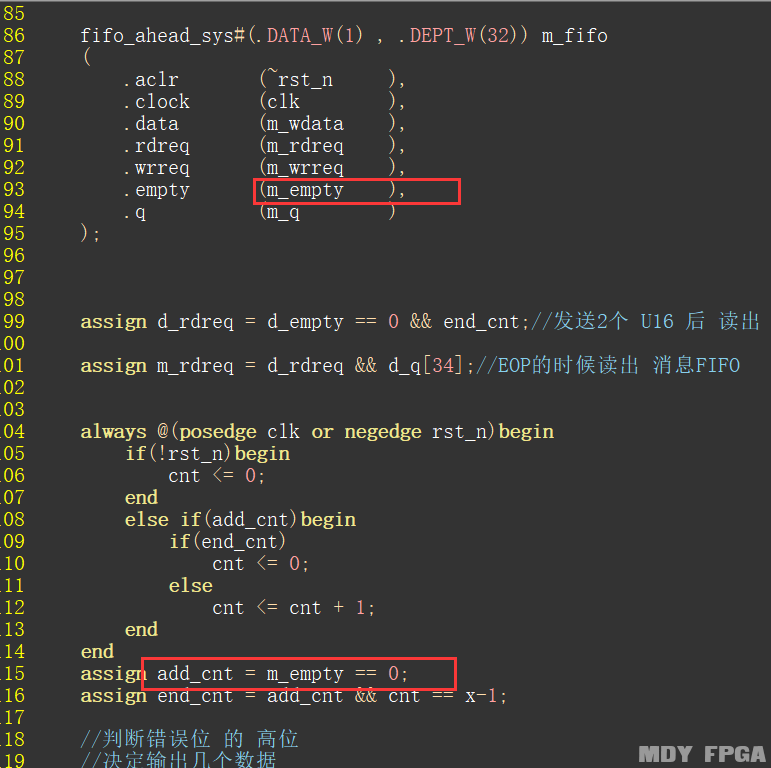

【问题7.13】在千兆网的rx_filter模块中,读数据的时候为什么用add_cnt=m_empty==0,这个信息FIFO的不空作为读条件?

答:信息FIFO非空,表示数据FIFO中存有一个完整的包文,因为需要判断包文是否正确,所以需要数据FIFO中保存一个完整包文之后再读出。

由于本模块需要将32位的数据转成16位的,计数器cnt数两次,表示数据FIFO需要两个时钟读出一次,当遇到最后eop的时候,由于可能存在无效字节,所以当无效字节为2个或者3个的时候,计数器只需要数一次就够了。

【问题7.14】在千兆网的rx_filter模块中,信息FIFO深度为什么设置为32,设置为1就可以了吧?

答:这里设置为32只是顺手而为,而且占用的资源也不是很多,所以就没有进行修改,深度改为1也是可以的。

【问题7.15】在udp发送的过程中,假设源端口为0x1234,目的端口为0x5678,那么发送的是12345678还是56781234?

答:发送的时候是按照12345678来发送的。

【问题7.16】为什么udp协议在发送和接收的时候,源端口和目的端口顺序会反?

答:包文的协议时固定的,只会按照源地址加目的地址的格式发送。

1. FPGA发送的时候,FPGA产生包文,端源端口是1234,目的端口是5678。然后发送格式是源+目,因此发送的是1234_5678

2. FPGA接收的时候,PC产生包文,源端口是5678,目的是1234,然后发送的是源+目,因此是5678_1234。

【问题7.17】请问一下,我编译千兆以太网的时候,为什么把这个clogb2文件添加进去就会报错,说是sv文件?还有这个文件有什么作用?谢谢

答:clogb2不是一个完整的module文件,它是被用include的方法加入代码中的。它不需要加到工程上,所以可以把它去掉。

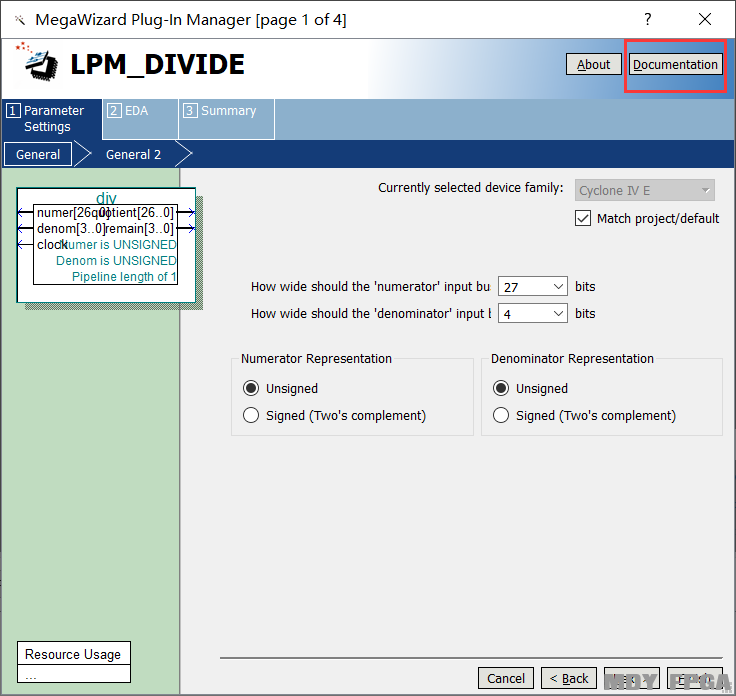

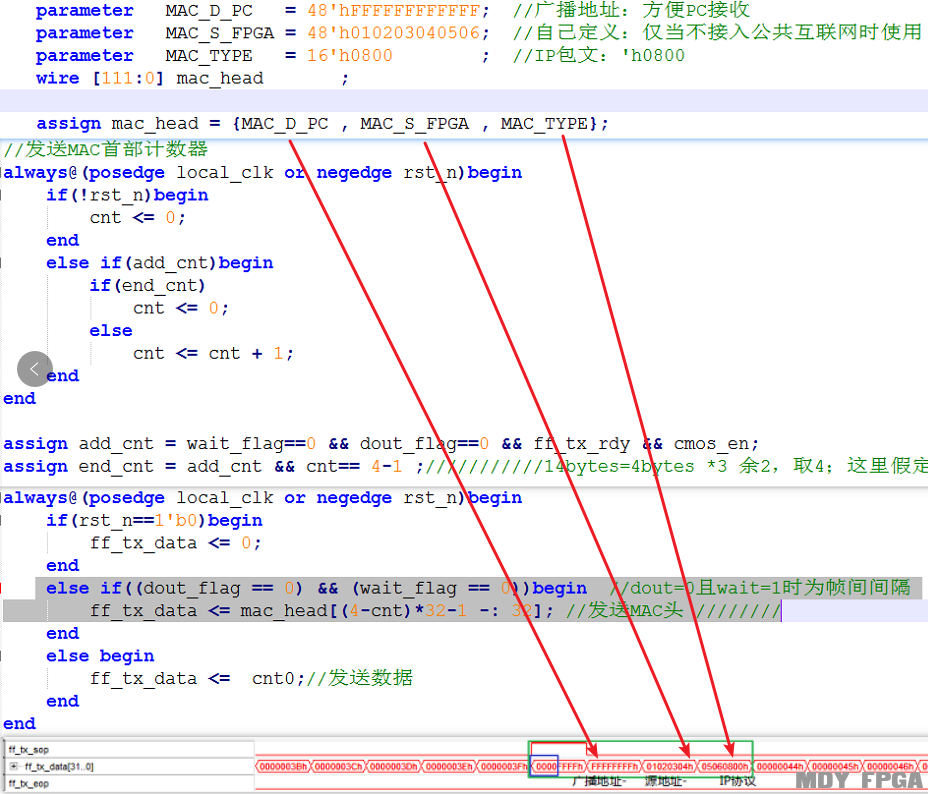

【问题7.18】请问下,在做练习工程的时候,需要自己设计MAC首部发送电路,MAC首部14字节,但数据位是4字节的,我需要定义 发送首部的计数器,这里4是不能被14整除的,我应该怎么处理?

答:1、可以在设计代码的时,把产生的mac头、IP头、UDP头拼接起来的时候,在最高位补2字节的无效数据零。

2、或者在mac_ip核进行相关的设置,具体可以查看相关数据手册附:数据手册在打开IP核后如图所示位置查看

【问题7.19】千兆网转百兆网的时候,需要给phy芯片一个参考时钟,是怎么给的?

答:开发板上有一个12M的时钟芯片,是给phy芯片的。外部晶振的事,跟FPGA无关

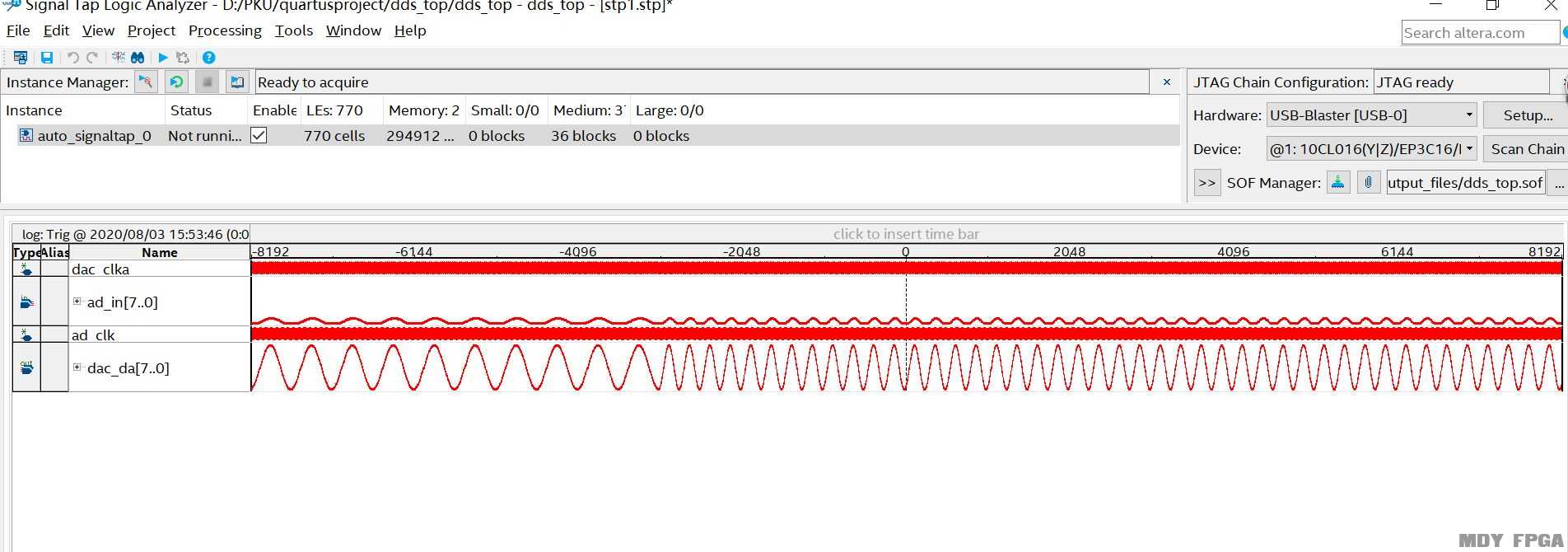

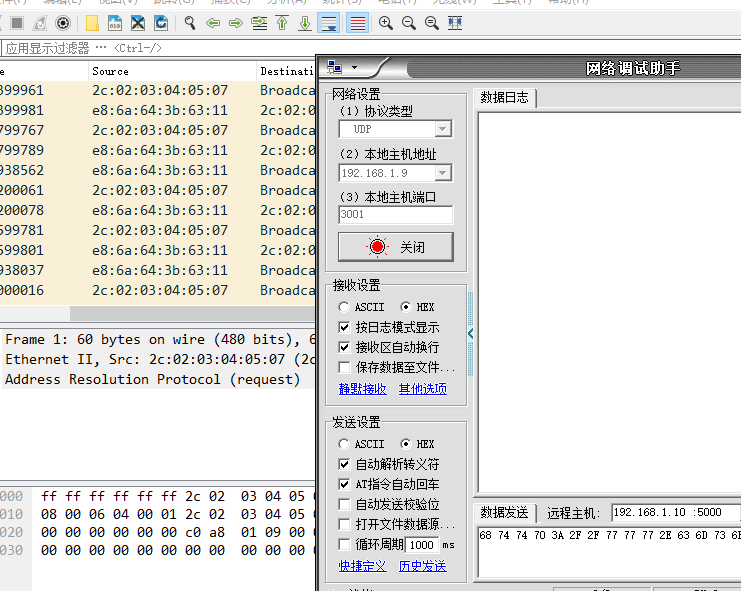

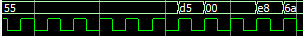

【问题7.20】我的采样时钟就是模块的工作时钟(always块里的);现在从MAC_IP核输出的数据不正确,根据常见问题PDF里问题1和6的解答,

有两种情况,如果时钟没问题那就有可能是IP核的输入信号有问题。我对应的代码和signaltap采集到的数据如图:

请问这种情况下,输入的数据算是正确的吗?

答:结果是正确的。原因同上【问题9】

【问题7.21】再设置好电脑的IP地址之后,把界面关掉,然后再打开就没有了,需要重新设置,怎么解决?

答:

1、点击左下角的WIN图标,输入CMD然后回车,打开DOS模式窗口。

2、在DOS命令行提示符下直接输入:“netsh winsock

3、reset”,然后回车,会提示需要重启,不要管它。

4、在DOS命令行提示符下直接输入:“netsh int ip reset

5、reset.log”,然后回车,提示重新启动计算机完成此操作。

6、关闭DOS窗口,重新启动计算机,问题解决。

【问题7.22】千兆网我们的和用mdio接口的有什么区别? 我们的教程是没有用到这个接口的

答:MDIO接口是用来配置外部的PHY芯片的,不是用来传输数据的,也就不是做网络协议使用的。 当您需要配置外部的PHY芯片时,可以使用MDIO接口,否则可以不用。

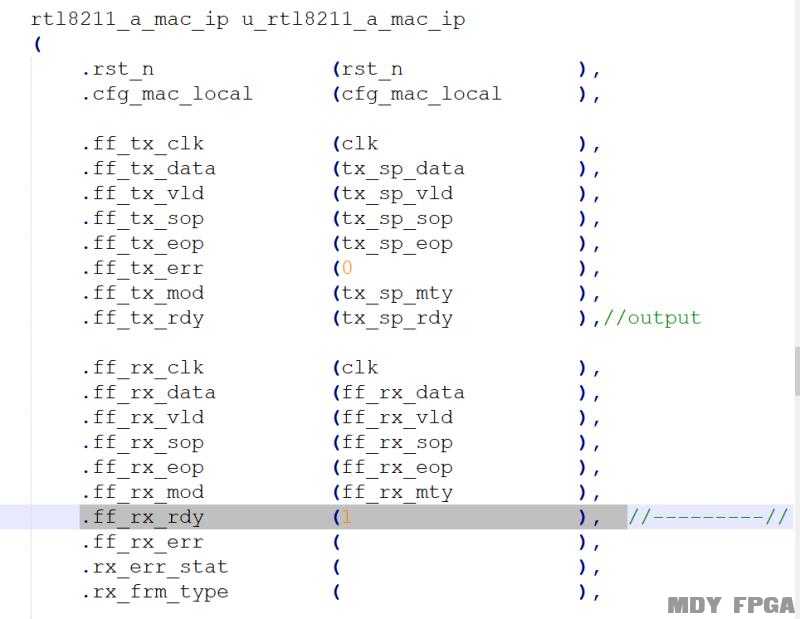

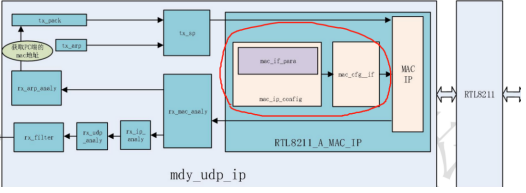

【问题7.23】请问千兆网工程里,输入给MAC_IP核的ff_rx_rdy信号为什么直接置1?跟速率和带宽有关吗?

答:rdy表示下游模块准备好指示信号,如果准备好了就为1,没准备好就为0。 在本案例中,下游模块是rx_mac_analy模块,该模块支持rtl8122_a_mac_ip模块任意速度的数据,

即无论怎么来,下游模块都能接收并正确处理,所以在此处置为1(时刻准备好)就可以了

【问题7.24】请问,一个基础问题,千兆网工程里多个模块都调用了FIFO,在不同模块里调用的fifo的例化名(比如:u_dfifo)能否重复?

答:可以试试操作,在不同模块是可以重复的。

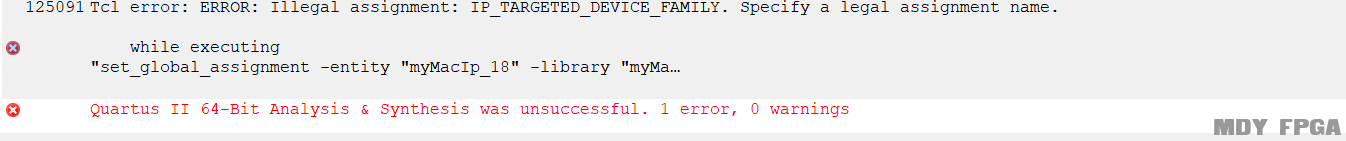

【问题7.25】这个是因为IP核没有破解吗?

答:这个错误就是高版本生成的工程在低版本中打开出现的编译错误,用高版本的quartus打开即可(如18版本的)

【问题7.26】千兆网课程使用的是哪个PHY芯片?

答:本课程使用的是MP801芯片,使用提RTL8211芯片。但课程中,几乎没有涉及到PHY芯片的内容,PHY芯片使用的是默认配置。对于其他PHY芯片,也是通用的。

【问题7.27】千兆网课程是ALTERA,是否与XILINX的通用?

答:本课程主要涉及到各个协议的RTL实现,这部分代码是通用的。但有一个MAC IP核,本课程的工程是使用ALTERA的,XILINX的亦有相同的IP,需要您移植。

总的来说,MAC IP占整个课程的比重不大,大概是5%的内容。

【问题7.28】您的UDP教程里面包不包含ARP和CRC328bit这两个地方的讲解?

答:有arp的讲解,但crc就不包括。

【问题7.29】千兆网课程的源码中有相应的tb仿真代码嘛?

答:没有,但如果要验证功能正确性可以上板验证和仿真文件

【问题7.30】请问下载程序后,电脑检测不到本地以太网,把程序删除又可以检测?

答:可能程序里有复位管脚,把这些PHY芯片复位了。

【问题7.31】以太网通信中,抓包工具wireshark能抓到 但网络调试助手收不到 是怎么回事?

答:可能性有如下几种,请逐一排除。

1. IP地址不正确,请检查IP地址,尤其注意目的IP和源IP的区别

2. 端口号不正确,请检查端口号,尤其注意目的端口和源端口的区分。

3. 目的MAC地址不正确,可以尝试发送广播包文(非ARP包文)测试。

4. 包文过短,小于60字节。

【问题7.32】工程仿真的前导码后为什么有两个字节的0呢? 按理说应该紧跟目的MAC地址 图中e8 6a就是目的MAC开头.

答:MAC IP核的有一个32bit对齐的功能,关于该功能意义,请看【问题7.3】。

如果出现上图中问题,有可能是MAC IP核中的32bit对齐功能设置有误。

【问题7.33】千兆网项目中,是否包括TCP协议实现?

答:千兆网项目是使用的UDP协议,而非TCP协议。

目前来说,TCP协议由于有握手机制、重发机制等功能,在逻辑上实现相当困难,暂未看到商用的案例。

【问题7.34】高速采集后的数据 是存到内存或者flash吗 ?

答:激光项目:采集到数据后,内部进行计算和处理,并将结果通过千兆网上传到上位机。

大数据采集项目:从光纤采集到数据后,保存到DDR3中,然后读出送到PCIE上位机。

【问题7.35】请问插上千兆网模块后,PING不通?

答:千兆网模块是一个基于PHY层的模块,不是完整的网卡,实现的是PHY层的协议,没有实现MAC层、TCP/IP层协议。

因此,不可能PING通(因为PING功能是在TCP/IP层实现的)。要实现PING功能,需要编写FPGA程序来实现。

【问题7.36】插上设备后,电脑识别成百兆网问题?

答:上电后,电脑与千兆网模块之间会开展自协商对话,根据双方的环境确定通信速率。如果希望工作在1G,而实质协商成100M,则依次按如下检查。

1. 检查电脑网卡是否支持1G,具体请看网卡设置

2. 检查网线是否支持1G,有类型的要求。

3. 换台电脑试试

4. 以上都测试过后还不行,请找指导老师确认。

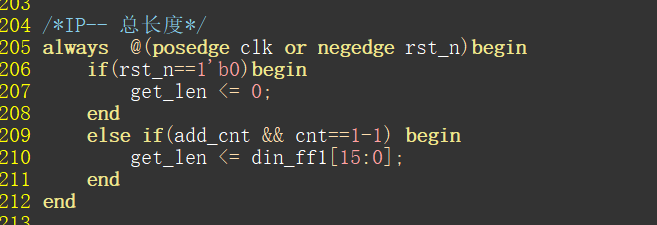

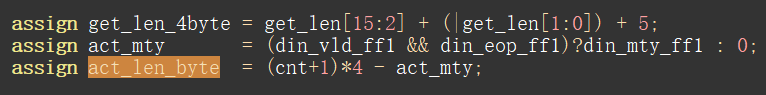

【问题7.37】请问千兆网的rx_ip_analy.v文件,getlen是获取总长度,第二个图片get_len_4byte是完全不懂,请老师给个提示?还有+5又是什么意思呢?

答:IP长度是20字节,get_len_byte是实质获取到的数据长度(不包括IP头),单位为字节;get_len_4byte是实质获取到的长度(包括IP头),单位为32bite。

【问题7.38】你好,这个rx_ip_analy部分的,我不太清楚到底是实际的采集长度小于等于输入获取的长度还是输入获取的长度小于等于实际采集的长度。

感觉上面说应该cnt <get_len_4byte,下面又说act_len_byte < get_len是错的。

答:get_len:从长度字段获取到的长度;

get_len_4byte:从长度字段获取到的长度,单位为4字节;

act_len_byte:从数据字段中获取到的长度;

所以,从数据中获取到的长度,小于“字段指示的长度”,就是错的。

【问题7.39】请教大家一个问题,以太网调试的时候,主机网卡不是realtek PCIE FE Family,主机接收不到fpga发送的报文怎么办?

答:一般来说,只要发送端发送的包文符合网口传输协议,无论什么网卡都可以都到包文。可以检查一下

①fpga发送的包文协议是否正确;

②检查网口识别的速率是否与工程速率匹配;

③检查网卡是否有问题

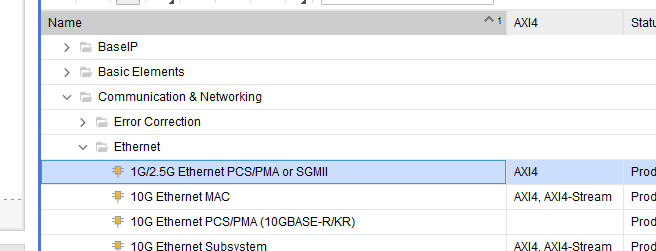

【问题7.40】千兆网工程使用sgmii接口,请问在vivado中用哪个ip核呀?

解答:GMII和RGMII接口使用的VIVADO IP核为:tri_mode_ethernet_mac。而SGMII接口使用的IP核为:1G/2.5G Ethernet PCS/PMA OR SGMII。注意:SGMII模式,使用上面的这个IP核。注意,SGMII协议会与本课程中的MAC协议不同,要特别留意。

【问题7.41】问:千兆网课程的MAC是使用的官方IP核,还是自己RTL写的?

答:本课程的UDP、IP、ARP等协议,是MDY的RTL代码写的。而MAC部分,使用的是官方IP核。 在平时使用中,MDY也自己写了简化版的MAC层部分代码,主要实现的是添加前导码和校验和。

这一部分没有文字说明,也没有教程,如果有疑问,请自行消化。下载链接如下:http://fpgabbs.com/forum.php?mod=viewthread&tid=4481&page=1&extra=#pid5534

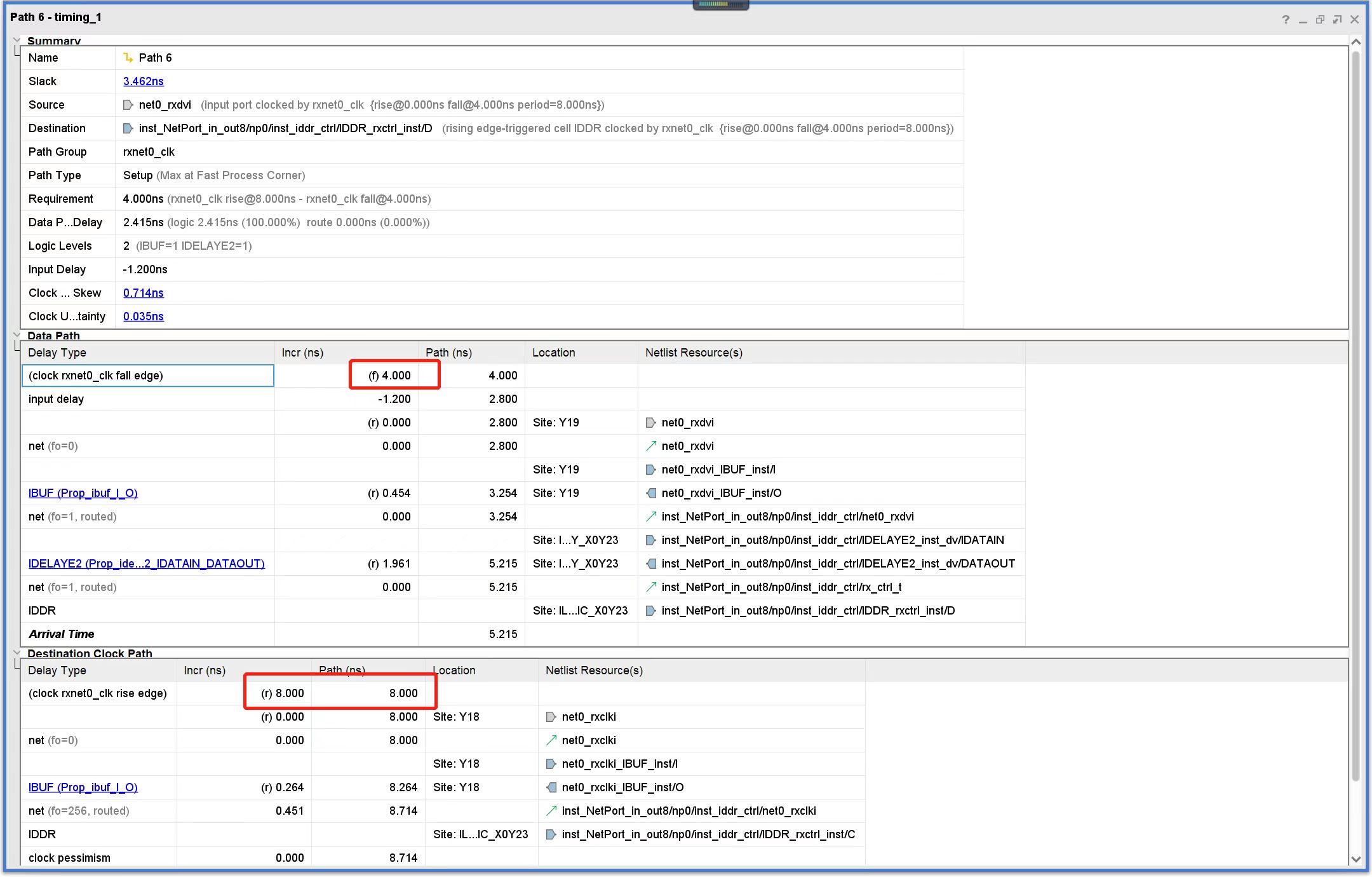

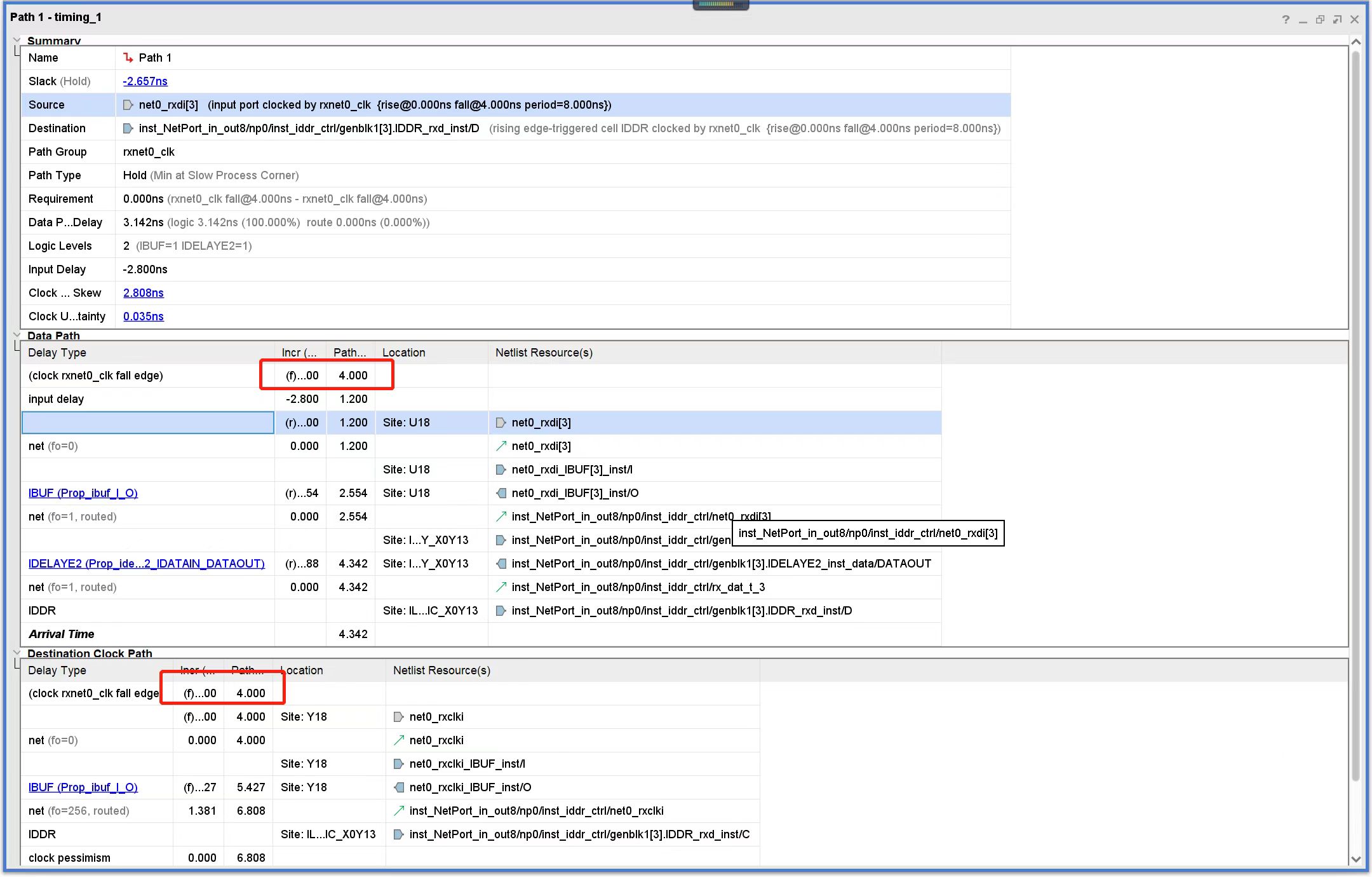

【问题7.42】问题:以太网约束中,建立时间的时序报告如图一,请问下为什么上面是4ns,下面又是加8ns呢? 保持时间分析如图二,为什么这两个都加4?

图一

图二

答:

1. 这项目是RGMII模式,时钟为125M,上升沿和下降沿均采样,相当于时钟周期是4ns。

2. 建议时间和保持时间都是从4ns开始计算,可能是约束时钟时指定的,指定从4,可以看时钟约束。(有些是从0开始)

3. 建立时间分析时,目的时钟路径要加上时钟周期(4ns),保持时间分析时,目的时钟路径不需要加上时钟周期。

原因请看时序约束问题汇总贴8.16 (http://old.mdy-edu.com/wentijieda/20210410/1294.html)。

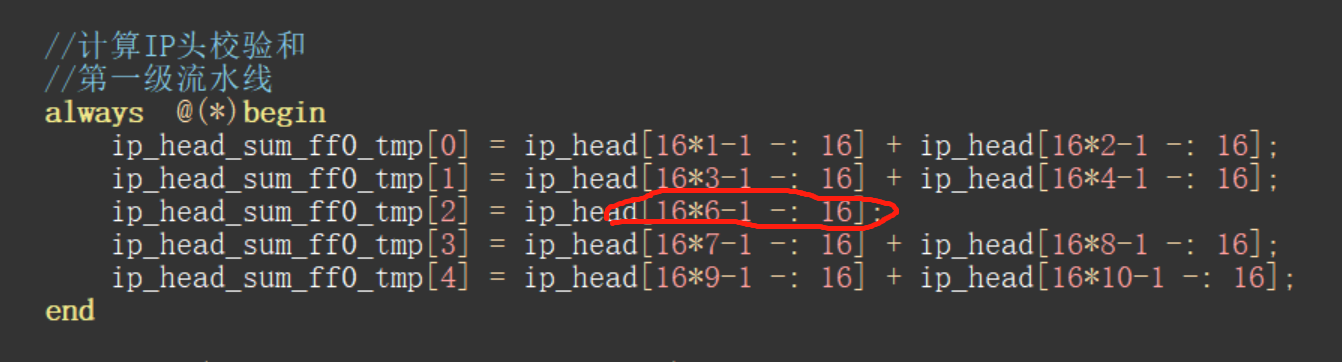

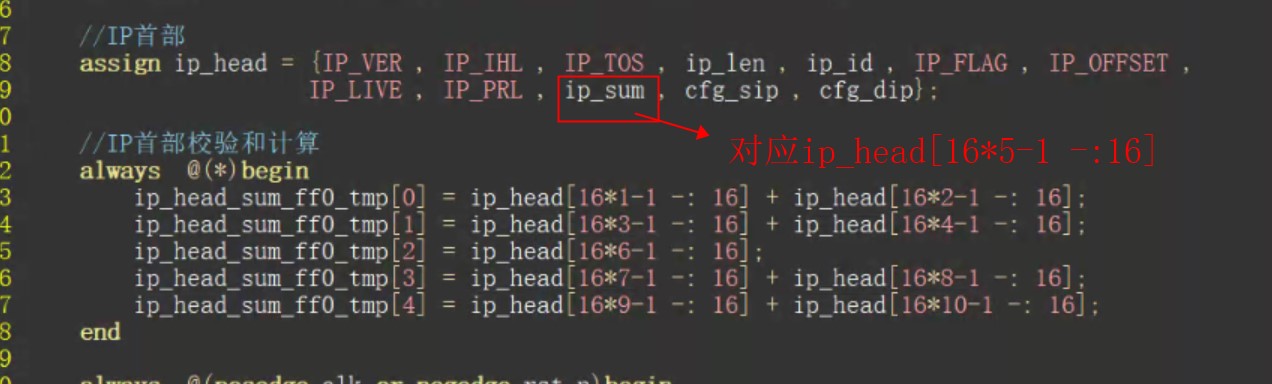

【问题7.43】请问一下,IP校验和,校验和字段不加,这部分应该是5吧,16*5。

解答: 如图所示,ip_head[16*5-1 -:16]对应的是IP校验和的值,但此时还未计算出IP校验和的值,所以ip_sum=0,因此可以省略对ip_head[16*5-1 -:16]的求和计算。

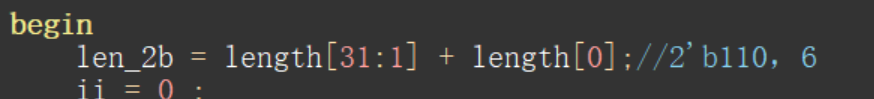

【问题7.44】想请问一下,以太网tx_pack模块的测试文件,这条语句是什么作用呀?

解答:用于计算长度的有多少个2字节长度的数据。length表示长度有多少字节,而len_2b表示长度有多少个2字节。信号length不取最低位,相当于数据除以2。

【问题7.45】问:当把板子和电脑的网线相连后,电脑那里显示“未识别网络”,如何解决“未识别网络”问题?

答:“未识别网络”这是正常现象。

当把FPGA板子和电脑相连后,无论FPGA有没有程序,此时双方通信均是“MAC层”的协议。该层协议只识别出速率,即1G还是100M速率。

而“未识别网络”是指TCP/IP层的协议,需要TCP/IP层的完整协议支持,这是FPGA板子没有的,也难以实现的功能,所以肯定是处于“未识别网络”状态。

在真正应用中,FPGA板子和电脑只是点对点通信,不需要组网。

【问题7.46】问:如果我想将GMII口换成RGMII口的话,是只需要将位宽以及MAC重新配置一下就可以了吗?由于RGMII口是双边沿采样,所以不确定需不需要加额外的操作。我看网上用vivado的时候还需要用原语将phy给的rxclk处理一下才行。

答:将GMII口换成RGMII口的话,除了需要将位宽以及MAC重新配置一下,还需要更换一下硬件电路部分电阻。

【问题7.47】问:就是这个选项卡里面,勾选local loopback的时候,这个回环是MAC侧回环还是phy侧的回环呀

答:这个回环是MAC侧回环。

【问题7.48】问:千兆网工程里有一个用户时钟:100M。这个100M时钟是否可以用125M代替。

答:用户时钟只要大于75M即可。在提供的参考工程文档里,有这个说明,可以看文档。

【问题7.49】问:为什么是干什么用的?是不是IP头?

答:伪首部仅是参与校验和计算而使用的,不会放到包文中进行传输。

【问题7.50】问:如下图,UDP包文协议中,各部分的位置在哪?

答:按照一个包文的先后顺序,其包文字段分别是: 前导码+MAC头+IP头+UDP头(不包括伪首部)+UDP数据+校验码。

【问题7.51】问:接收方向做CRC校验,是如何确认结果的正确性的?

答:CRC接收校验有两种方式。 第一种,接收过来的数据做CRC校验,结果与接收过来的CRC校验值比较,相同则接受正确,第二种,数据和接受过来的CRC结果一起做CRC校验,结果应该为“固定数”。注意,这里是固定一个数,不一定是0,因为CRC算法里,还存在输出结果反转和异或等操作,会导致结果不一定为0。

【问题7.52】问:接收方向做CRC校验,将数据和CRC位一起计算,结果一定是0吗?

答:数据和接受过来的CRC结果一起做CRC校验,结果应该为“固定数”。注意,这里是固定一个数,不一定是0,因为CRC算法里,还存在输出结果反转和异或等操作,会导致结果不一定为0。

【问题7.53】问:在千兆网工程中,很多模块都有使用到了rdy信号,该信号的产生有些是跟FIFO的存储数据个数关联。如FIFO深度为4096,当存储数据大于4086时,rdy为0;小于4086时,rdy为1。为什么这样设计?

答:rdy是本模块准备好信号,为1时表示可以接收数据,并且保证能够正确处理。为0时,要求上游模块不能发送。 当FIFO满了的话,进来的数据无法保存,就会丢失。所以满了当然rdy为0。为了让上游模块有一定的缓冲时间,将提示的水线设置小一些,例如4096的,就设为4086,这样上游模块可以晚几个时钟响应也是可以的。 至于是4086,还是4090,根据项目情况自己设置。

【问题7.54】问:千兆以太网的macIP核部分的完整视频有没有?我看这个IP核说是也需要配置,还有ctc校验,这些都是自动完成的吗?(千兆网)

答:没有,这部分不是直接使用就可以了,我们工程里有一个配置表代码 直接可以用的,ctc是自动完成的 不需要参与

【问题7.55】问:请问老师这部分讲解有吗,找不到?

答:没有讲解,直接使用

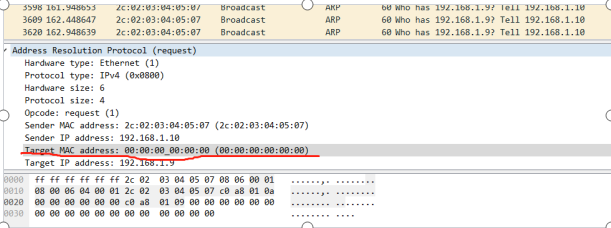

【问题7.56】问:麻烦问下千兆以太网接收mac地址是0是怎么回事呢?

答:广播包应该是这么显示的

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8.射频前端

需要了解相关信息可以联系:易老师13112063618(微信同号)