八、时序约束专题课

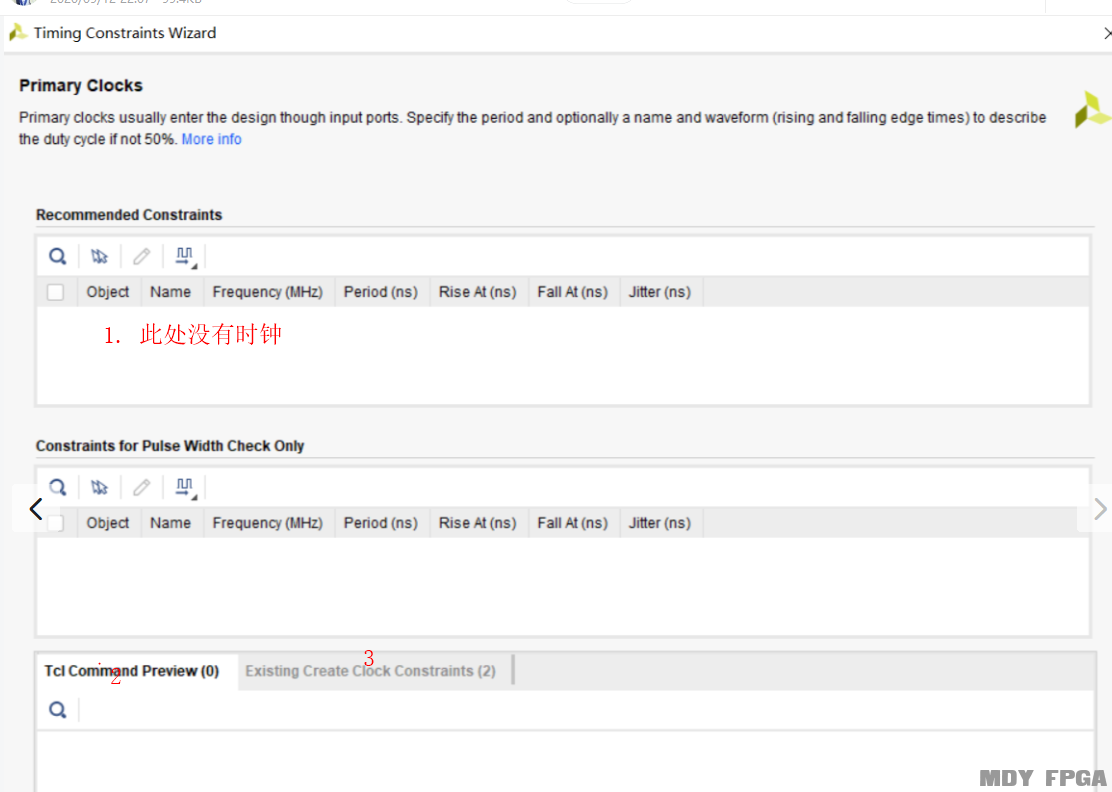

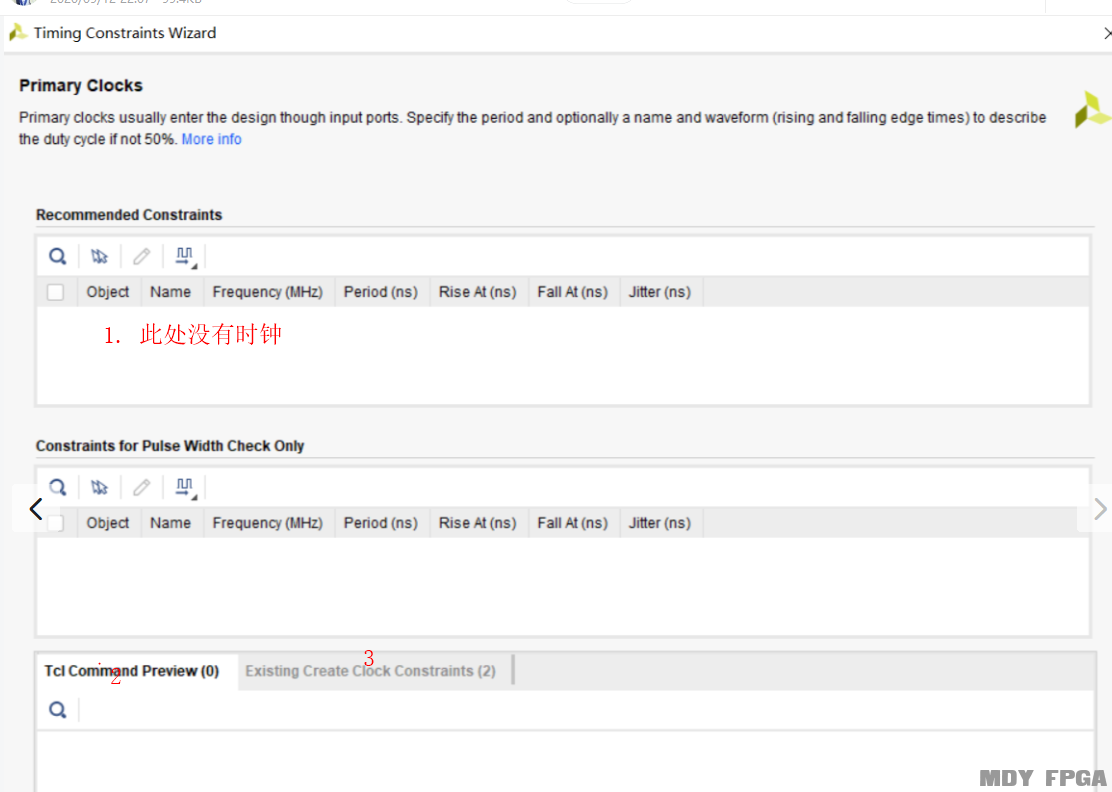

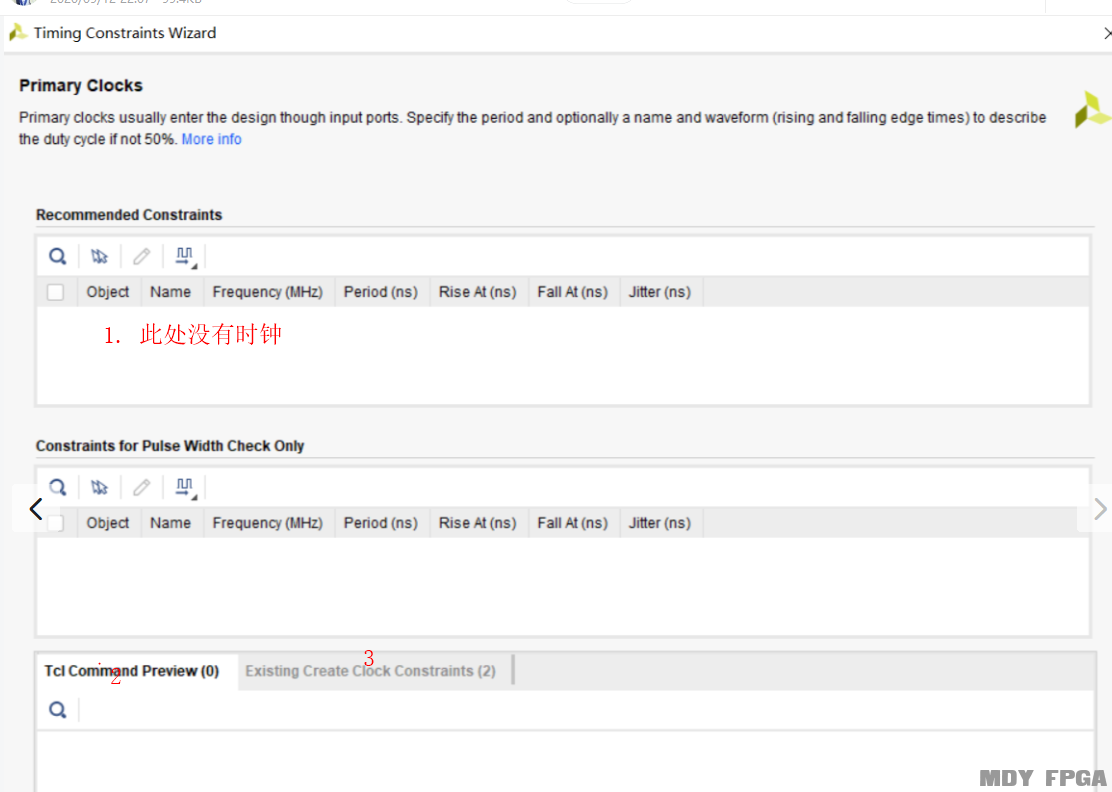

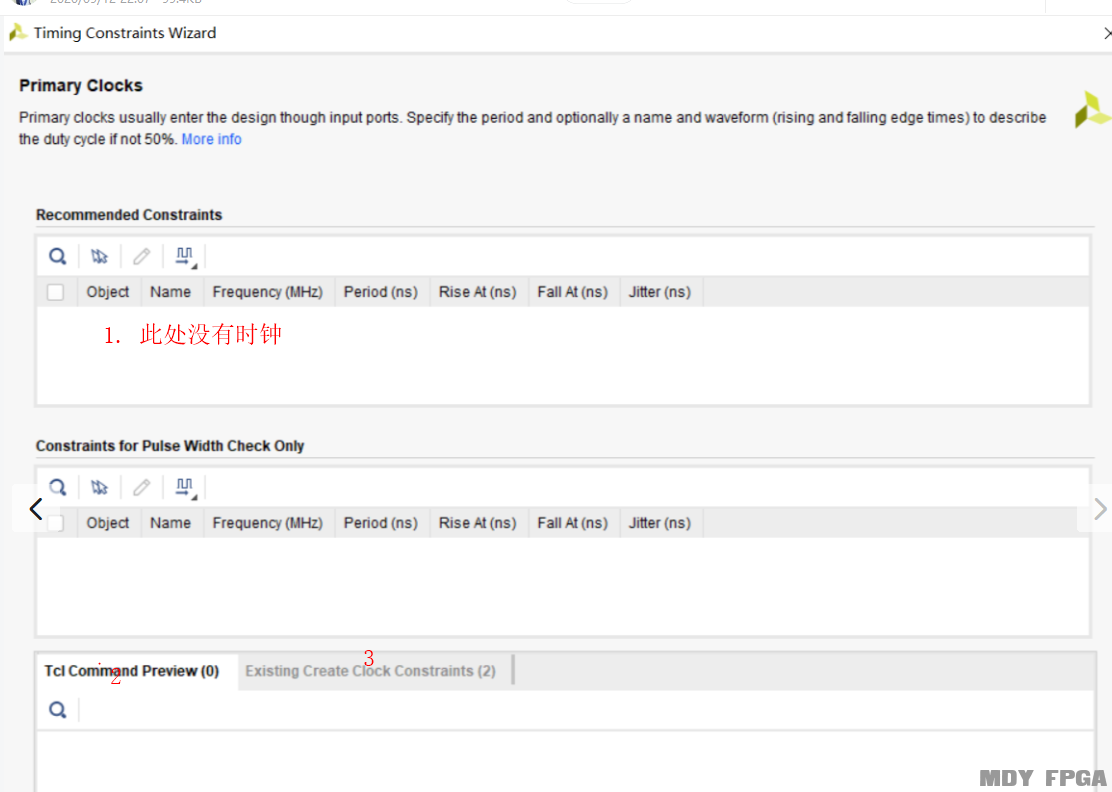

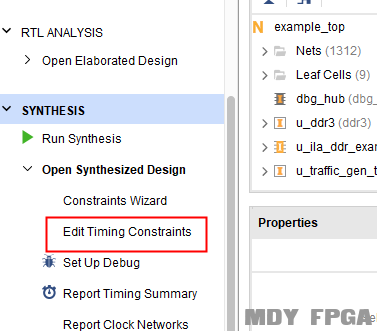

答:请注意,位置1的地方是列出的是“没有被约束的时钟”,如果该时钟已经被约束了,就不会在这里列出来了。

注意上图中3的位置,该列说明了有2条时钟约束。可以点击这里看看,是不是已经对时钟进行约束了。

为什么会有时钟被约束了呢?因为该工程已经有约束文件。

【问题8.2】VIVADO/QUARTUS练习中,rst_n是否需要约束?

注意的是,该信号是输入信号,但没有随路时钟进来。所以该信号可以认为是无时钟的情形,按照课程理论,应该定义一个虚拟时钟。

定义了虚拟时钟后,再重新使用约束向导,约束rst_n。

【问题8.3】在VIVADO中,如何设置虚拟时钟?

答:虚拟时钟不能在时序约束向导中添加,需要在下面窗口添加

Clock name为该时钟命一个名字,Source objects是不需要填的,因为是虚拟时钟,就是没对象了。

【问题8.4】时序约束出现时序违例(Slack为负数),如何处理?

答:首先指出一个误区:当约束出现错误时,想当然地认为是“时序约束做得不对”,所以应该怎么去改“时序约束”,从而让这些错误消失,这是一个错误的观念。时序约束的作用:在于检查“设计是否满足时序要求”,它是用来审视自己设计的,很多情况是,要改设计代码来满足时序要求。

当时序约束提示有错误时,应该阅读“时序报告”,从报告中分析时序路径(数据到达时间、时钟到达时间和数据要求时间等),根据报告分析错误的原因,并根据原因来实行不同的方法。

以建立时间违例,说明具体方法如下

1. 时序报告中,找到提示错误的路径,即目的寄存器,以及源寄存器。注意,这是两个寄存器的点。

2. 首先判断,源寄存器的时钟,与目的寄存器的时钟,是否相同。如果不同,可以认为是异步时序,见步骤3;如果是相同,则看步骤4。

3. 如果是异步电路,那么处理方法如下:

A. 确认做了异步处理。对于数据,则是通过异步FIFO来做异步处理;如果是控制信号,则要经过打两拍来处理。

B. 确认做了异步处理后,仍然会报“时序违例”的。这个时候,可以该路径设置成set false path,不用再检查。

4. 同步电路下,具体处理如下:

A. 查看两个寄存器点之间,经过了多少加法器、乘法器、除法器等。

B. 对于除法器,要特别留意,一般是1个时钟计算不完的。那么可以 a.想办法不用除法;b. 通过使能信号控制获取除法器结果的时间。

C. 对于乘法器和加法器,或者其他组合电路较多的。想办法分隔成流水线来实现。可以参考MDY 流水线的内容。

5. 如果是IP核的违例,检查是否时钟不满足IP核的要求。如果没问题,就不用管。

6. 如果是ILA等在线调试工具路线的违例,则一般不用处理。

7. 如果是线延时太长的,可以尝试打一拍处理。即A->B的线太长,可以打一拍,变成A->C->B,这样线延时就小了。

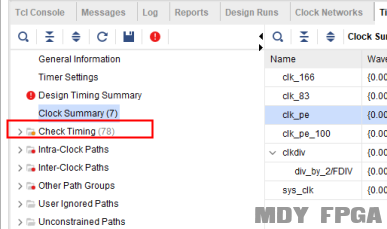

【问题8.5】VIVADO中,如何查询未约束的时钟、未约束的输入延时和输出延时等?

【问题8.6】如下图所示,跨时钟域打两拍的方法,其实只是一个信号的传递,当第一个信号出现不稳之后或者错误之后,后面就会把这个错误的信号继续传递下去,并没有起到纠错的作用

答:上图中打两拍的方法,其本质不是为了“纠错”,它的作用是为了防止“亚稳态”。

防止亚稳态的本质:防止中间状态过长。之所以采用两级触发器的方法,是因为D触发器出现亚稳态的可能性非常小,而两级D触发器出现亚稳态的概率就更小了。

【问题8.7】既然打两拍的方法不能纠错,那“打两拍”还有什么意义?

传输过程中,如果发了0,如果全部接收模块都认为是1,这并不是问题,这是可以预防和可控的(例如检测多几次就行了)。

但是亚稳态的时候,如果发了0,但部分接收认为认为是1,而另一部分模块认为是0,至于哪些模块认为是1哪些是0,这是随机的,不可预知的,这就是灾难。

更详细的内容,建议参考:FPGA知识大串讲 http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=581

【问题8.8】模块A的时钟clka为100MHz,模块B的时钟clkb为300MHz。现在模块A要把32bit的数据送给模块B。模块A要如何发送,模块B要如何接收呢?

答:方法1:采用异步FIFO的方法。

方法2:采用指令信号的方法传输,模块A产生vld信号给模块B,模块B对vld进行同步化处理(打两拍)后,检测同步化信号的上升沿。

需要注意的,VLD的信号是让模块B周期的三倍或以上。由于clka是100M,产生的vld是10ns,而clkb是300M,周期是3.33ns。所以模块A只要产生1个时钟的vld给模块B即可。

【问题8.9】模块A的时钟clka为300MHz,模块B的时钟clkb为100MHz。现在模块A要把32bit的数据送给模块B。模块A要如何发送,模块B要如何接收呢?

答:方法1:采用异步FIFO的方法。

方法2:采用指令信号的方法传输,模块A产生vld信号给模块B,模块B对vld进行同步化处理(打两拍)后,检测同步化信号的上升沿。需要注意的,VLD的信号是让模块B周期的三倍或以上。

由于clka是300M,产生的vld是3.33ns,而clkb是100M,周期是10ns。所以模块A要产生10个时钟的vld给模块B。

【问题8.10】一块电路板上,有两个芯片,芯片A的时钟clka为100MHz,芯片B的时钟clkb为100MHz。现在芯片A要把32bit的数据送给芯片B。模块A要如何发送,模块B要如何接收呢?

答:方法1:采用异步FIFO的方法。

方法2:采用指令信号的方法传输,模块A产生vld信号给模块B,模块B对vld进行同步化处理(打两拍)后,检测同步化信号的上升沿。需要注意的,VLD的信号是让模块B周期的三倍或以上。

虽然clka和clkb都是100M,但他们不是同一个晶振产生的,因此都是异步时钟。为了满足以上要求,所以模块A要产生3个时钟的vld给模块B。

【问题8.11】A, B时钟都是50M,但是他们不相关,为了防止编译器把他们默认为同一个时钟,是不是要用一个异步时钟组约束,来告诉编译器他们是不同的两个时钟?

【问题12】 建立时间可以是负值吗?

【问题13】 程序原本时序可以通过,加上singalTap节点之后时序不通过是什么原因

由于改变了资源,因此肯定对时序是有影响的,有可能改善了也有可能恶化了。如果时序有问题,分析路径,如果是在线调试工具路径,评估是否会有风险,没风险就算了

【问题8.14】时序约束什么时候要做?

2.一般时钟大于100M的时候,我们就要做一下时序约束。

【问题8.15】时序约束建立时间和保持时间的生活案例。

1. 13点起飞,起飞前15分钟要到机场,这个15分钟,就类似于建立时间要求。

2. 机场每小时有要飞一趟飞机,每个小时表示的是时钟周期。

3. 飞机起飞后,机场要保持10分钟,之后才能来下一批乘客,这个10分钟就是保持时间。

4. 这个人出发去搭13点的飞机,因此他要在12点45分之前到机场,并且是12点10分之后到机场。既不能早到,也不能晚到机场。

5. 如果这个人12点45分之后才到机场,那就搭不上本趟飞机,即违反了建立时间要求。(建立时间影响的是自己坐飞机)

6. 如果这个人12点10分前就到了机场,那就会因此上一趟飞机的起飞,即违反了保持时间要求。(保持时间不满足,影响的是上一批乘客坐飞机)

7. 这个人是计划去机场,因此他要估算几点能到机场。首先他会算所有情况下的最大延迟,如刚到路口红灯就来了、走路最慢等,在这种最慢的情况下,如果能在12点45分前到,说明建立时间没问题。

然后,他会算所有情况下的最小延迟,如刚到路口绿灯,走路最快,在这种最快的情况下,如果能在12点10分后才,那说明保持时间没问题。

【问题8.16】为什么建立时间分析的时钟到达时间要加一个时钟周期而保持时间分析则不用呢?

而保持时间分析,则是“本个时钟”发出数据后,如果延时太小,会影响“本个时钟”对上一个数据的采集,因为不需要加1个时钟周期。

另外,要注意一点,保持时间是跟时钟周期无关的。

【问题8.17】一个外部的信号,经过状态机的“组合逻辑”,这也要做同步处理吗?

答:需要做同步处理的。首先明白一点,FPGA里的时序逻辑=组合逻辑 + D触发器。组合逻辑的最终结果,还是要发D触发器的。所以还要做同步化处理的。

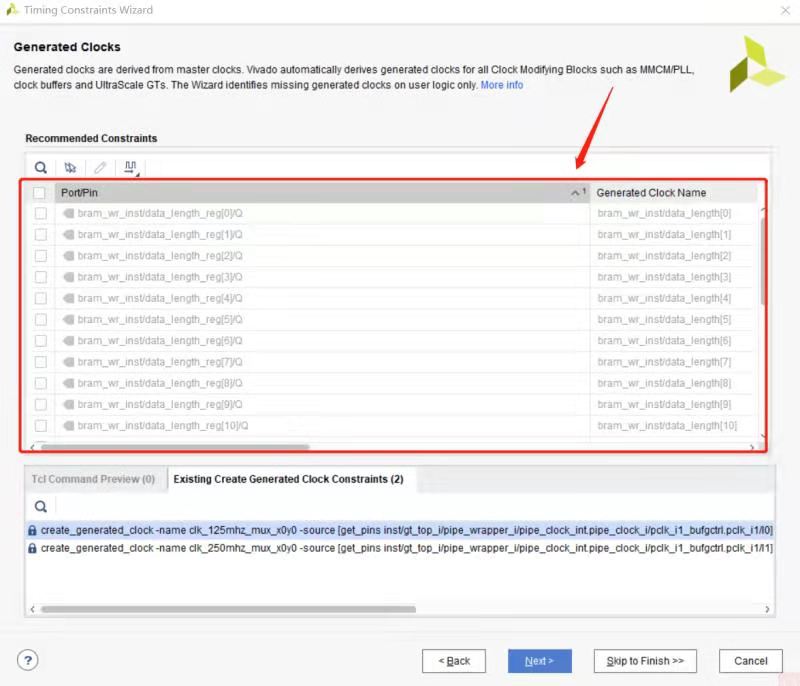

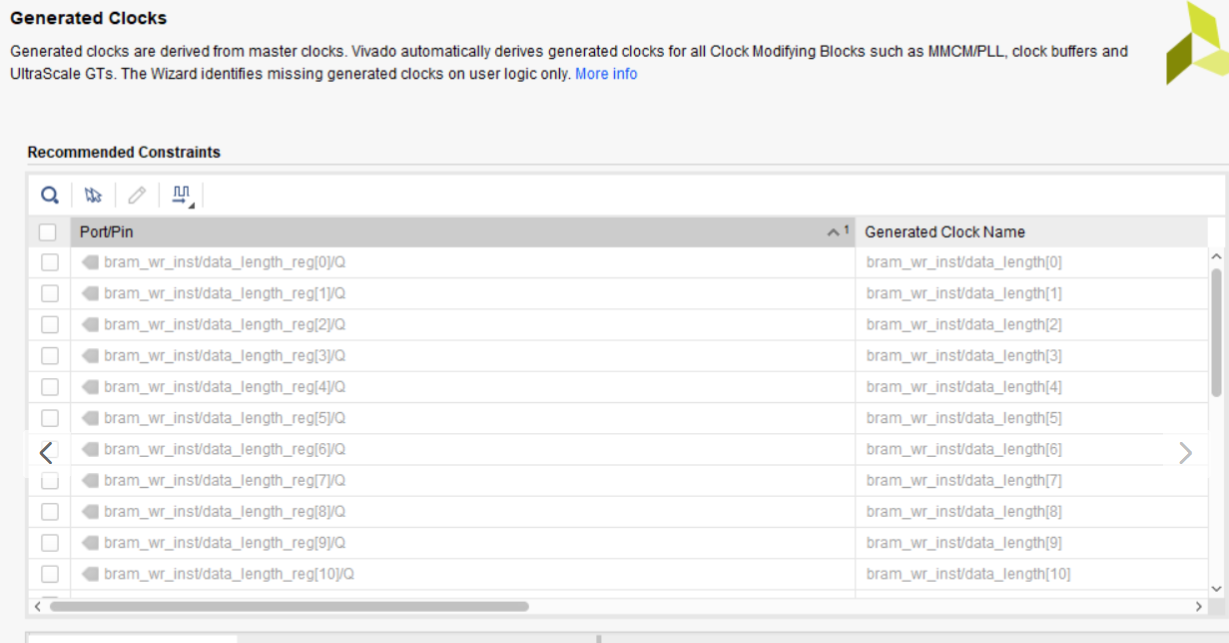

【问题8.18】请教下,做时序约束,做到这步时,这些都要勾选上吗?

答:当然不是,要逐个分析确认,没有一选就全选上的道理。

【问题8.19】下面的生成时钟约束,是否一定要勾选?

答:这应该看生成时钟那一节视频,里面重点强调了“什么叫时钟”? 上面的图里,您应该要搞清楚,它被识别出时钟了,正不正常?如果是正常,那您肯定是要添加约束,定义频率吧。如果它不应该识别出时钟了,

那您应该检查您的代码,看是不是代码不规范引起,或者有没有潜在的问题。注意一下:约束不是目的,约束是为了查看报告,看设计有没有问题的。

【问题8.20】系统同步只可能是单沿采集?没法像DDR那样双沿采集?

答:系统同步也是可以是双沿采集的,但比较少。课程里,只是介绍了部分情形。

如果想看所有情形有哪些,可以打开VIVADO的时序约束向导,可以设置INPUT DELAY窗口查看。

【问题8.21】QUARTUS生成SDC时,默认出现的那条时钟约束是正常的么?我自己删掉就行了?

答:默认生成的当然是不正常。

【问题8.22】老师问一下,我画的后边那个部分,我认为应该没有数据吧?

答:不是 这个不是有没有数据的概念 而是数据是否稳定的概念。

【问题8.23】请问下有没有针对SDC时序约束语法的讲解吗?

答:时序约束里,只讲解了用到的部分。如果想看更多部分,我估计你要看这个语法的权威资料了。

【问题8.24】老师您好,我在学习时序约束视频,看到第一个视频这块“流水线设计思路:乘法器可以分成加法器,然后加法器还可以分成什么,一直听不清”

答:最后可以分成与门这些最简单的门电路。

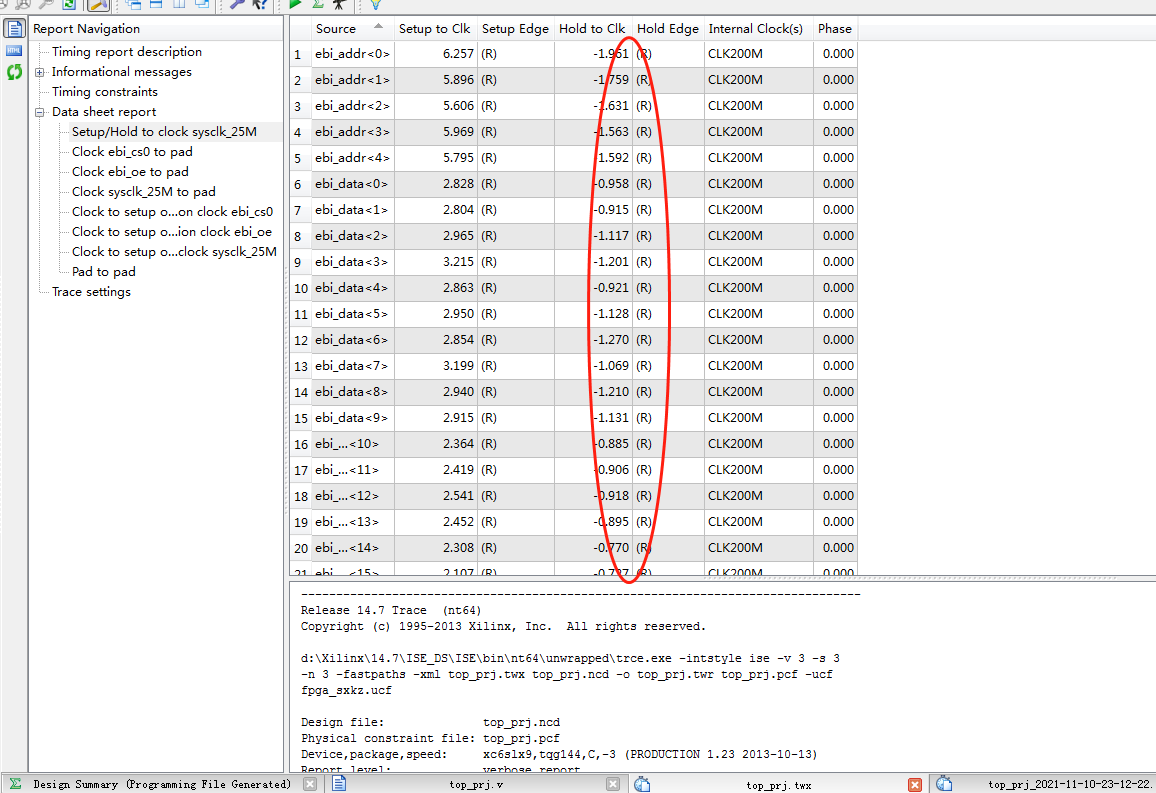

【问题8.25】老师请问红色的是不是不满足时序要求?

答:不是的,setup和hold时间形成一个时间窗,只要在这个时间窗里信号稳定就饿可以了 在使用时序分析工具的时候,字体为红色时间提示是不满足时序要求

【问题8.26】什么样的信号会被工具判断为时钟?

答:一个信号被VIVADO QUARTUS判断为时钟,不是看名称里是否带有“clk”等字母。而是主要看其是否用于“时钟”的行为中,主要有如下几种情况。

1. 被关联到always敏感列表里的时钟信号。说明会被连到触发器的时钟端,所以会被认为为时钟。

2. 被连到PLL和MMCM等时钟管理器的输入端,这会被认为是时钟。

3. 被连到锁存器的条件端,例如一个没有补全的组合逻辑代码,其条件就会被认为时钟。

【问题8.27】用ila抓取信号分析,发现异常,而时序约束报告正常,因此可以认为时序报告正常,而时序会有问题?

答:

1.在线逻辑分析仪是用于判断逻辑是否出现问题,可以认为是检查时钟节拍下的逻辑判断。而时序约束是解决D触发器的建立时间和保持时间问题,是一个时钟内的时序问题。

所以,不能用ila来推导时序约束,这是不同层次的问题。

2.官方可以保证,用户代码和时序约束的生成结果是正确,即在输入的代码和约束,给出来的报告一定是正确的。但时序约束对不对,这是客户保证的。

3.出现结果不对,可能性很多,不一定是时序问题,要注意“充分必要条件”。

【问题8.28】同样的工程不做任何改动,有时编译后下板验证正确,有时编译后下板验证不正确,是不是时序问题呢?

答:有可能是,但又不一定是。这是时序不满足的一种现象。但反过来,没有说,出现这种现象,就一定是时序问题。

【问题8.29】设置时钟约束时,假如有虚拟时钟的情况,虚拟时钟是必须要设置的吗?

答:

1.原则上所有接口有应有约束。

2.设置虚拟时钟,可以方便将对应信号归到该虚拟时钟好,这样方便做分析,例如看有没有跨时钟域等。

3.是不是一定要做,取决于项目老大要求,不做不一定有问题。

【问题8.30】一个always模块下,if 、else if,,,else ,写的太多了 ,是不是会容易造成时序问题呢?这种说法对吗?

答:这里有一个定义要搞清楚的,什么叫“多”?

1. 是3个就多,还是10个?每个人标准不同。

2. 即使是同一个人,使用不同的器件,这个“多”也是不同的。有些高级的器件,10个IF也不多,有些低端器件,3个也多。

3. 即使同一个人,同一个器件,但if里的判断条件也有讲究。如果判断条件里一个除法器,那1个if也多,如果只是判断0和1,那么10个也算少。

4. 最具可操作性的做法,给定时钟约束,看时序报告。报告没问题,那就是没问题;否则会有时序违例的错误。

【问题8.31】output latency一般设置成多少呢?pipeline 有啥用?

答:由于除法器占用资源较大,难以在一个时钟周期内计算完毕,需要多个时钟才计算完,这个pipeline就是设置多少个时钟周期的。

如果您不清楚要多少个,设置填一个较大的数,然后看时序报告是否正确。如果正确,就没问题。

【问题8.32】请问:MDY的案例中,为什么串口需要对din进行同步化,而SCCB就不需要对sio_din进行同步化?sio_din也是外部器件进来的吗?

答: 是否要对信号进行同步化,最核心的理解是“该信号是否能够保证满足建立时间和保持时间要求”,也就是“该信号的变化和时钟存在确定性相位关系”。

以串口为例,串口的输入信号与FPGA时钟是没有任何联系的,该输入信号可以在任意时刻变化,也就有可能刚好在时钟上升沿变化,从而不满足建立时间要求,

因此要做同步化处理。而SCCB案例中,由FPGA时钟里产生了sio_dout、SCK等信号,而sio_din在sck作用下变化,所以sio_din与FPGA时钟是有一定关系的。

可以认真看时序图,在FPGA对sio_din有采样时刻,时序已经要求sio_din要稳定不变的,所以可以不用做同化处理。

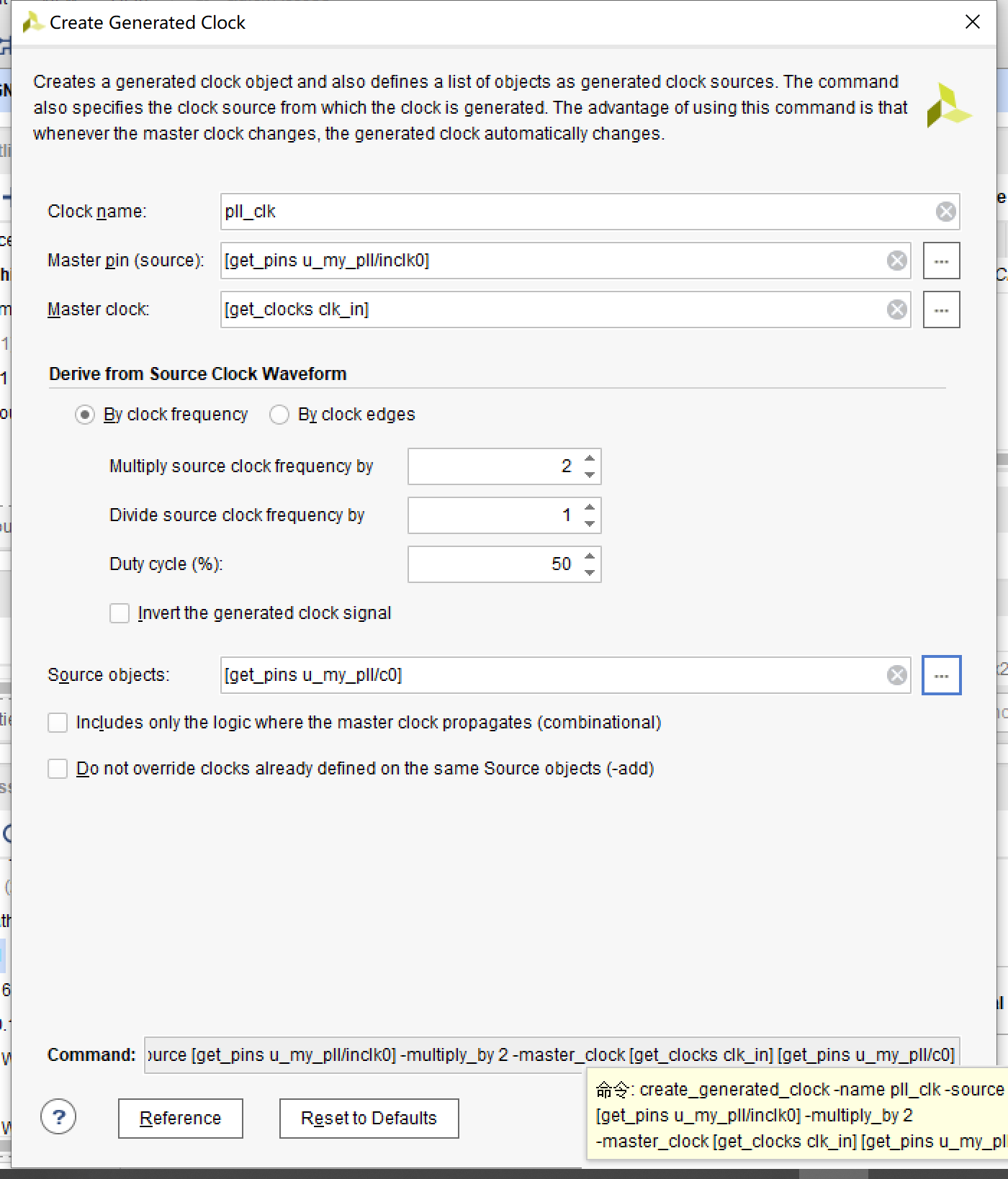

【问题8.33】请问工程中使用了PLL,在做时序约束时,generate clocks窗口显示没有PLL产生的时钟,如下图,为什么?

答:PLL、MMCM等产生的时钟,默认是由工具自动推导约束的,不用用户来约束。虽然用户没有约束,事实上是做了分析的。例如下图中,

可以看到c0_my_pll这个时钟。其中,c0_my_pll是工具自动命名的。

用户也可以自己约束PLL/MMCM产生的时钟,方法如下图。

按照方面方法,约束好,重新分析就可以了。

【问题8.34】问:如果使用的IP核内部代码出现了时序约束违例,该如何解决?

答:IP核是由官方提供的代码,一般用户不能修改,如果该IP核出现违例,可以从以下方向入手:

1. 一般IP核是有指定的频率范围,可以从数据手册找到,请看是否满足了数据手册要求。

2. 如果频率正确,还会出现报错,可以检查时钟和复位管脚有没有正确使用,根据经验,这通常是引起问题的原因。

3. 尝试修改编译策略,重新综合看看。

【问题8.35】问:请问时序约束只是针对FPGA输入与输出端进行约束,而不是针对FPGA内部模块之间或者模块里面。这样理解是否正确?

答:不是的,内部肯定也跟约束有关。

【问题8.36】问:老师,想问下时序约束,DDR4的uiclk需要时钟约束吗?(时序约束)

答:需要的,设置好时钟频率,周期就可以了,就是需要create clock就好了

【问题8.37】问:关于input delay的抖动解释。(时序约束)

答:需要理解的抖动,不是指一个波形的结果,是多个波形叠加的结果。假设说一个PWM波形,周期为10ns,理想情况下变高为2.5ns,变低在7.5ns。由于存在不确定延时情况,所以有时候变高在2.6ns,变低在7.6ns。有时候变高在2.4ns,变低在7.4ns。有时变高在2.3ns,变低在7.3ns。数个波形叠加,就看到了抖动的现象。