明德扬最近做了抖音系列短视频,感兴趣可以关注明德扬抖音号:FPGA技巧分享(87481069842)至简书籍短视频(74803215644),内容不断更新!点赞+关注,学习不迷路!

一、波形规则

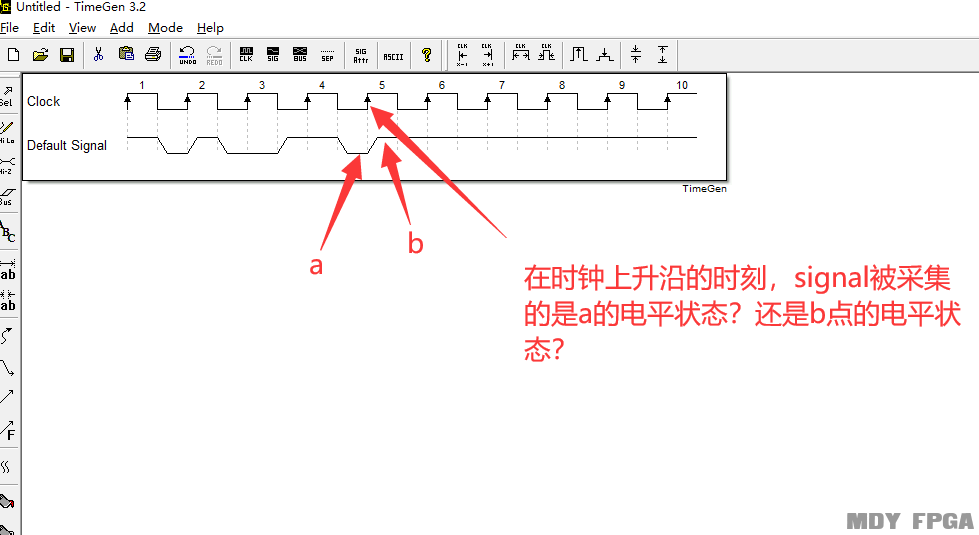

【问题1.1】如下图所示,在时钟上升沿看信号的问题。

答:采集到的是a点的状态。即MDY看波形的技巧:时钟上升沿前看输入。

注意,该技巧有前提条件:默认为同步信号,即信号与该时钟是同一时钟域信号。

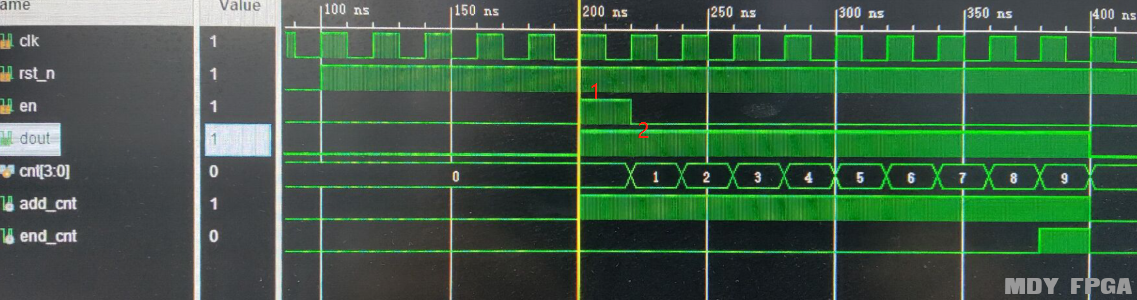

【问题1.2】按照MDY看波形的技巧:时钟上升沿前看输入信号,即信号等于1后,下一个时钟沿才检查到该信号为1。

但我在仿真的时候,发现是信号变1的瞬间就检查到了。如下图,期望是在2时刻dout变高,结果 在1时刻就变高了。

答:该问题本质是仿真的bug问题,在测试文件中产生en的那里,应该加上"#1"的延时,不要让en的边沿和时钟边沿对齐。

更详细的原因,请看如下贴子:关于在仿真软件中计数器提前计数的问题 http://old.mdy-edu.com/wentijieda/20210409/1211.html

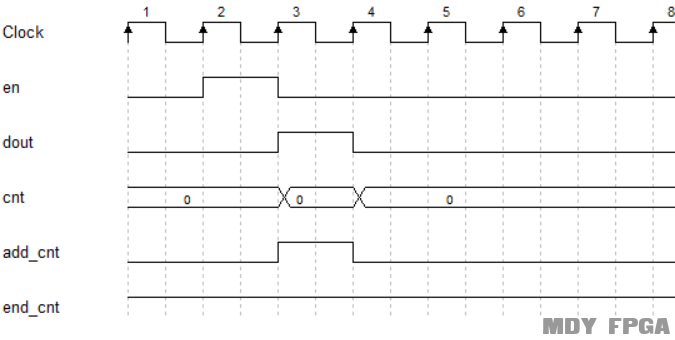

【问题1.3】 如下图所示,收到en之后并没有间隔一个时钟周期,只有半个时钟周期。

答:仿真的时候,是以时钟为单位进行判断的。以时钟上升沿看到en=1为开始点,这样看的话,就是1个时钟周期。

【问题1.4】 “时钟上升沿前看条件”,如下图所示,如果A是输入的话,不是“亚稳态”了吗?

答:1. 波形图规则的前提条件:同一时钟域的信号,即同步信号,所以不存在“亚稳态”问题,亚稳态是跨时钟域才产生的。

2. 这里说的“输入”,不是指“FPGA的输入”,而是指当前always代码中的“条件信号”。

3. 理想波形中,a的变化和时钟上升沿变化是一致的,看起来保持时间不满足。但实际在电路中,a的变化相对于时钟上升沿是有一定延迟的,该延迟就能满足保持时间要求。

二、信号定义规范问题

【问题2.1】关于rdy信号的讨论【汇总贴】

http://old.mdy-edu.com/plus/view.php?aid=1336

【问题2.2】请问咱这个cmos信号采集模块输出的dout_vld信号,当输出数据有效时,它是一个脉冲信号,还是持续的高电平信号呐

答:MDY里的任何vld信号,都用来表示数据的有效性,并且还表示了有效的个数。 即1个时钟的高电平脉冲表示1个数据有效;2个时钟的高电平脉冲,表示2个数据有效。

【问题2.3】使能信号同时出现问题 明德扬的练习中,接口信号会有多个en的情况,如en1,en2,en3等,或者如读使能rd_en和写使能wr_en。当这些信号同时有效时,该如何处理?

答:在模块内设计的时候,如果接口存在多个输入的en信号,我们有如下两个要求:

1. 上游模块发en的时候,同一个时刻只能一个en有效,不能同时多个en有效。(上游模块设计时保证)

2. 本模块在处理en的期间,上游期间不要再发en过来。(模块之间使用rdy来确认)

这样的处理方式,将大大简化了模块内部的设计;同时,也不会增加上游模块的负担。

【问题2.4】使能信号和标志信号有什么区别?

答:在明德扬规范中,使能信号一般表示某个阶段的触发条件,这个信号只持续一个时钟周期的高电平,比如en;标志信号一般用于区分多个阶段,

信号高电平持续时间和阶段时间相等,比如flag_sel信号。

三、计数器规范问题

【问题3.1】变量的表示能不能直接用en1、en2来决定,而不用flag_sel?

答:不能,这会违反“组合逻辑的设计规范”,组合逻辑不能有保持不变的功能,否则会生成锁存器,而锁存器是我们不希望有的。

关于锁存器的问题,可以看如下帖子:【答疑】关于锁存器问题的讨论 http://old.mdy-edu.com/wentijieda/20210410/1264.html

【问题3.2】变量法时,使用时序逻辑,判断en1和en2来决定变量x,是否可行?

答:功能可以实现,但意味着这需要一个寄存器组来存储变量x的值。注意,是一个寄存器组,非一个寄存器,因为x的每个比特都要存储,例如x=5,就需要3个寄存器存储。

所以,功能可以实现,但消耗的资源更多。

【问题3.3】 设计功能要求实现一个倒计时功能,数字是递减的。MDY的计数器模板都是递增的,是不是要改这个模板?

答:强烈建议不要改动模板,仍然是使用自增的计数器,例如cnt0,它是递增的,并且数20个。

然后再设计一个信号,例如data,data = 19-cnt0。这样就实现了递减功能。

所以,不要改架构。

【问题3.4】在计数器的模板中,结束条件(end_cnt)的判断已经在加一条件(add_cnt)成立的情况下了,是否下面对于end_cnt的设计中可以不加add_cnt,直接写end_cnt = cnt==x-1?

答:1、假设一种情况,波形图如下:收到en之后,dout变为高电平,持续1个时钟周期,这种情况下,计数器一直为0,如果结束条件不加add_cnt,就会像下图所示一样,一直为高,那么结束条件这个信 号就不能以表示计数器数完了,或者计数器数了1个的形式被后面的设计用到。

2、结束条件的意思是计数器数了多少个,数完了,而计数器数了多少个的标准表示方法为add_cnt && cnt==x-1,因此,结束条件需要加上add_cnt,否则意思就变了

[问题3.5] 当使用计数器时,加或者不加“add_cnt”有什么不同?即“add_cnt && cnt==5-1”和"cnt==4"这两个从含义上有什么不同?

[问题3.6] 如下面的代码中,x和y为0,会不会出现问题?

答:首先本代码设计中,flag_sel只会出现0,1,2的情况,所以不会执行最后那个else条件。

其次需要说明的是,本always是组合逻辑代码,按规范要求:条件一定要补全,否则会综合成锁存器,这是不希望看到的。因此,上面代码中的最后的else部分不能省略。具体,请看这篇文章:https://www.cnblogs.com/wen2376/p/15765384.html

四、状态机规范问题

【问题4.1】 4段式状态机 转移条件的生成 为什么还要&&当前状态?第二段case里不是有限制当前状态么?

答:1. 为了跳转条件更加的清楚,从波形图可以更容易看,为1表示跳转,为0表示不跳转。 如果不与上跳转条件,那么是不是状态机跳转,不仅要看“跳转条件”是否为1,还要看是什么状态,眼都花了。

2. 没必要去纠结是否多一个“与门”逻辑。这虽然牺牲了一个与门,但带来相当多的好处。

五、FIFO规范问题

六、定位问题交流【汇总贴】

http://old.mdy-edu.com/plus/view.php?aid=1337

答:包文中各个信号的含义请看《个人总结版:包文的理解》http://old.mdy-edu.com/plus/view.php?aid=1338

【问题7.2】rdy信号是不是有个说法一定要用组合逻辑产生?什么时候用组合逻辑?什么时候用时序逻辑?答:没有这种说法。用组合逻辑还是时序逻辑按实际需求来决定。

如上图所示,如果一定要在1000的数据位置产生 rdy信号,那么就用组合逻辑;如果在小于1000的数据位置产生rdy信号,就算相差几个时钟也是可以的话,那么就可以用时序逻辑。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 前端模拟采集、射频、电荷灵敏前置放大器

明德扬科技教育

明德扬科技教育