关于锁存器问题的讨论

如果同学们的问题我们帖子里面没有的请第一时间联系我微信同步:18022859964江老师,我们对新问题进行补充!

大家感兴趣可以关注明德扬抖音号:87481069842,内容不断更新!记得关注点赞学习不迷路!

很多同学提问到锁存器的相关问题,说明大家对这方面知识还不是很了解,今天我们就来探讨一下。

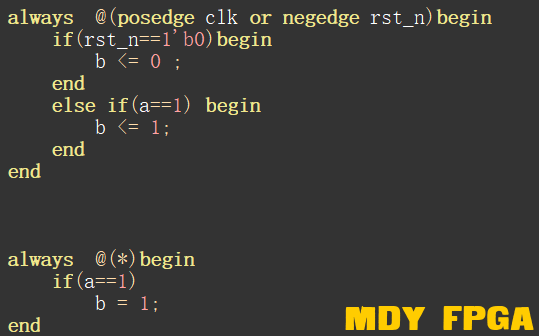

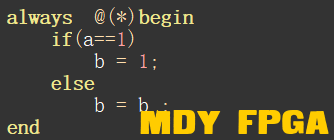

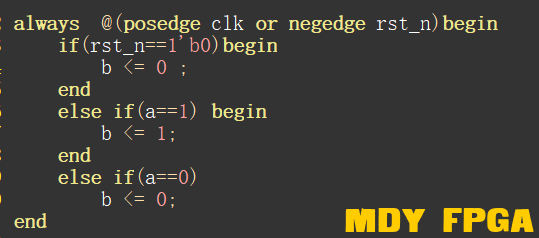

上面是两个没有else的代码,其等效于下面的代码。

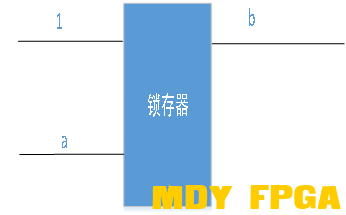

左边是时序时序逻辑的代码,右边是该代码所对应的硬件电路。特别注意图中红色的那个线,那个就是保持不变的“反馈”。

由图中可以看出,当时钟上升沿的时候,当选择器的结果赋值给信号b;非上升沿的时候,b一直保持不变,因此红色线在此期间也是保持不变的。

当a为0的时候,选择器选择当前b的结果,然后在下一个时钟上升沿赋给信号b。由引可见,实现“保持不变”的关键在于D寄存器。

问1:是不是所有的代码,if else都需要补全呢?

问2:是不是只要组合逻辑的if else补充了,就不会生成锁存器了?

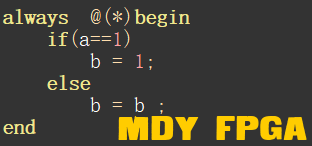

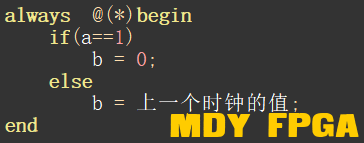

答: 不一定。这里的关键在于“保持不变”,千万不要从“代码层次”来理解,而应该从“功能的层次”来理解,要找准到底有没有“保持不变”。

例如,下面的代码,虽然else写上去了,但写不写else都是让b保持不变。所以这仍然会综合出锁存器。

问3:是不是组合逻辑不写else,就一定会生成锁存器?

答: 不一定。这里仍然要从是否包括“保持不变”这个功能来分析。如下面代码,假设a是1比特信号,其值只有0和1。

那么已经涵盖了所有情况,再不会有其他情况,所以不会出现保持不变的情形,这个时候也不会生成锁存器。

问4:case不写default,是否会生成锁存器?

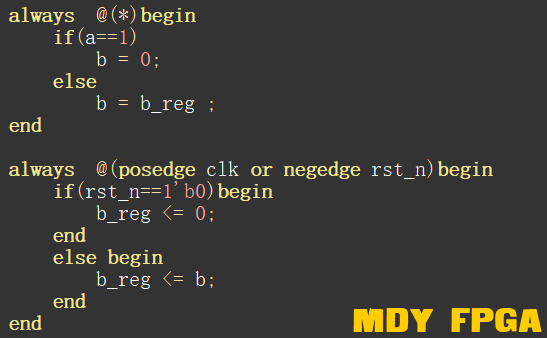

问5:功能上,我一定要实现“组合逻辑的保持不变”功能,该如何做?

问6:问题5的扩展,我就是要实现组合逻辑的保持,并且小于一个时钟周期的。

答:不正常需求,FPGA不会这么设计的。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 前端模拟采集、射频、电荷灵敏前置放大器

明德扬科技教育

明德扬科技教育