|

通过平时同学们反馈学习中经常用到的学习点,因此明德扬最近做了抖音系列短视频,都是一些FPGA学习技巧分享.

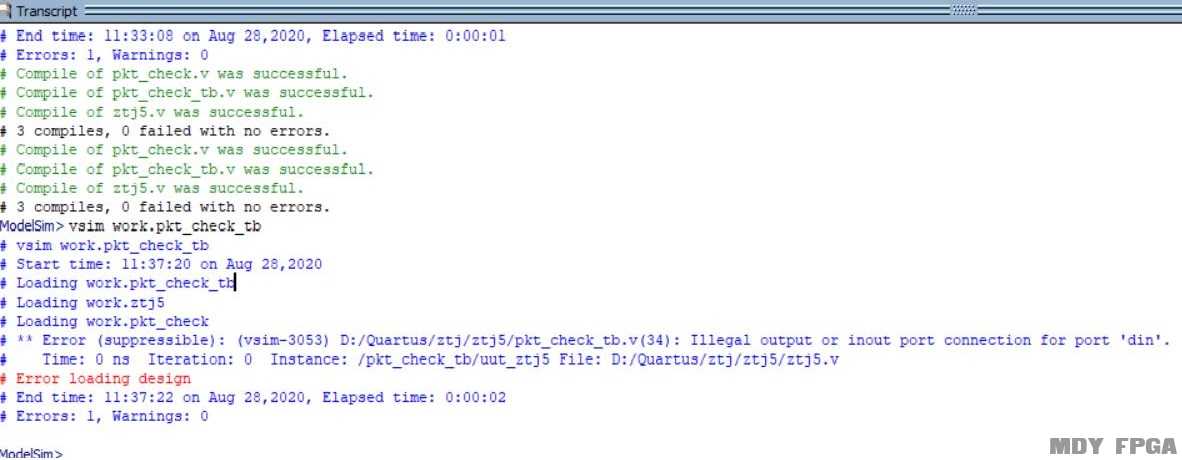

【问题2】这是出了什么问题?din输入的值出问题了?

答:这种情况的错误提示,如果是三态门(inout)管脚例化时,请按如下方法进行: 【问题4】如何在测试文件中,读取TXT文档的数据? 答:integer r_file;initial beginr_file = $fopen("../din_sim.txt", "r");endalways@(posedge clk) begin$fscanf(r_file, "%d", din);end上面就实现了将din_sim.txt里面的数据给到din的功能 【问题5】点拨教程的测试文件编号练习2中,提供的设计文件在哪里下载? 答:请看如下练习:03 测试文件的编写:http://old.mdy-edu.com/wentijieda/20210409/1213.html?1618046547请看以太网测试文件部分,其中的baowen.v就是了

答:这是为了避免时钟上升沿和信号上升沿同时出现,同时出现的话,在时钟上升沿就这个信号是0还是1(这种情况,实质的硬件电路是不会出现的)。

【问题7】在看波形时,部分信号只有“半个时钟周期”,是怎么回事? 答:仿真的时候,我们关注的是在上升沿的时候是0还是1,不关心测试信号是不是半个周期。具体可看:时序逻辑影响计数器精度:http://old.mdy-edu.com/wentijieda/20210410/1325.html

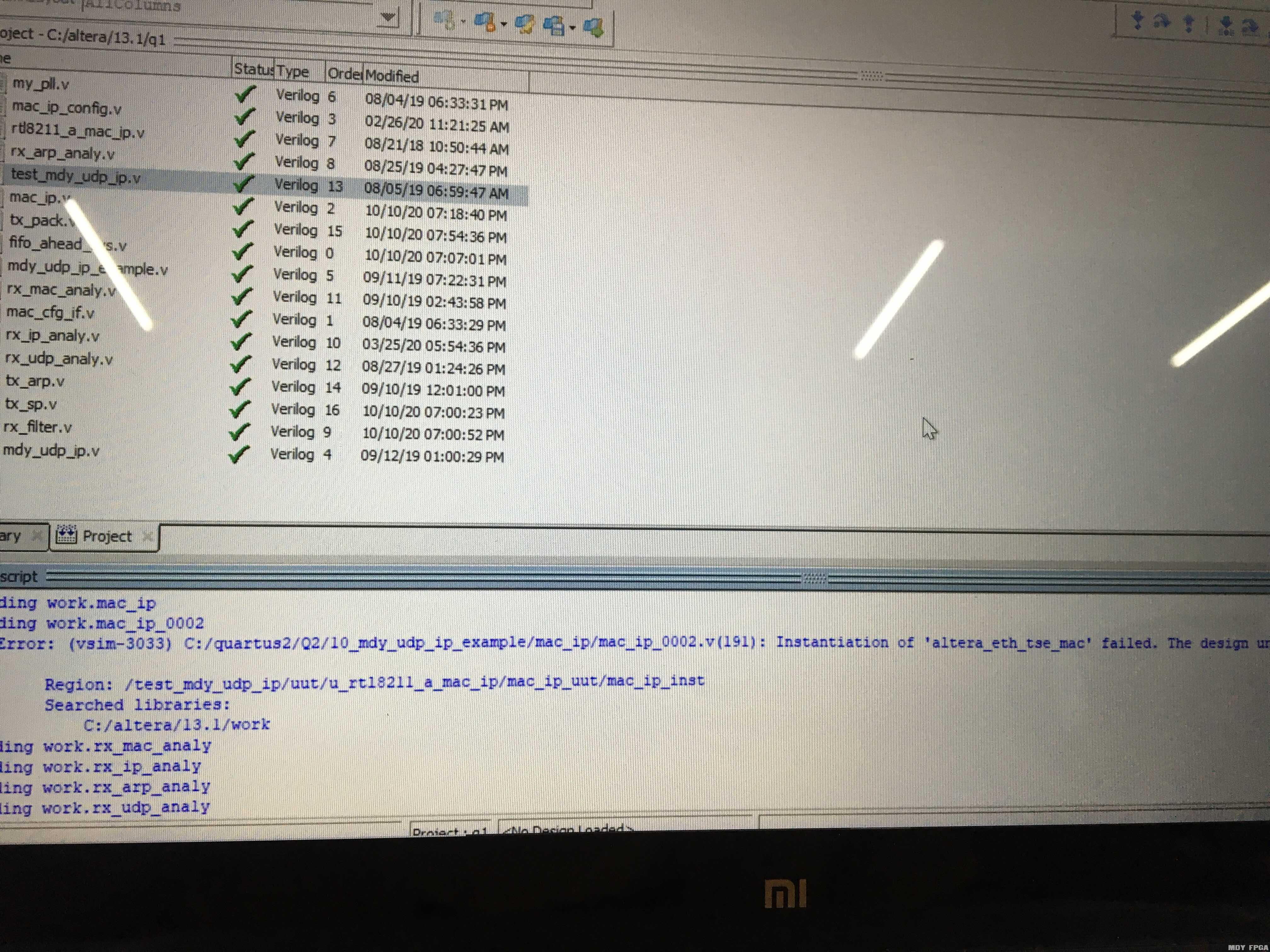

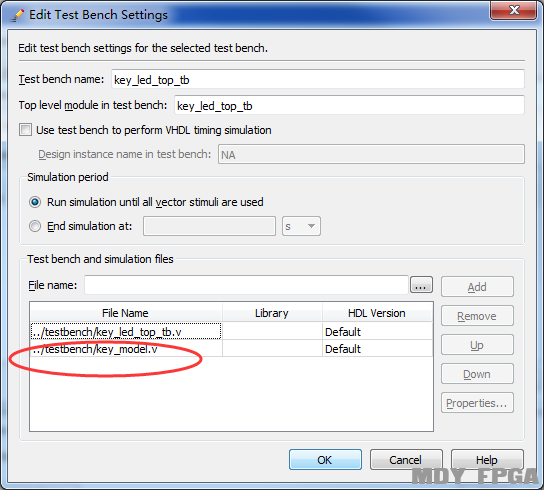

例如:对于串口接收,我们在编写testbench仿真接收模块时,使用了串口发送模块来产生测试数据, 而串口发送模块并不包含在Quartus 的RTL逻辑中,因此不会自动参与编译,无法得到仿真数据库;按键消抖时, 设计了一个按键模型,该模型仅用作仿真,也不会被Quartus自动交付给Modelsim编译。 解决方案:需要在设置NativeLink的时候手动添加该文件。如下图可以看到,我们设置时不仅添加了tb文件, 还添加了key_model文件,这样Moselsim才会根据该设置去编译key_model文件。  情况2:在做前仿真正常,在做后仿真的时候会遇到这个问题,这种情况主要考虑当前的工程中是否包含了该模块。 例如一个二选一多路器的实验,因为误把testbench文件设置为了工程顶层文件, 导致在后仿真时候因为没有对二选一多路器的逻辑内容进行全编译,导致找不到库, 此种情况也出现在对IP核进行仿真测试的时候,例如FIFO、PLL、RAM等。 解决方案:记得一定要将被测试的逻辑设置为quartus的工程顶层文件才能进行全编译得到时序网表文件,才能进行正常的后仿真。

【问题10】repeat(40) clk=~clk就是产生40个周期的时钟信号吗? 答:每隔40个时间就取反一次,所以周期是80。

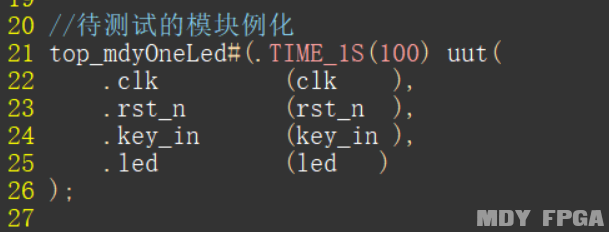

答:假设设计文件中有一参数TIME_1S=50000000,在仿真时,可以在测试文件中模块例化部分来修改这个参数,如下图所示:

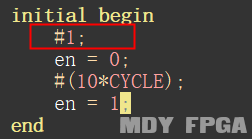

【问题12】Modelsim仿真产生随机数 答:reg data; data = $random % a; //产生从-a+1 ~ a-1 的随机数 data = {$random} % a; //产生从0到a-1的随机数 【问题13】当不符合“波形图规则”,或者对着代码,明明符合条件但就是没有执行的情况。 答:这由于信号的变化沿和时钟上升沿同时有效了。软件有时候会误认为是数据先变化然后时钟才变化,这是不符合实质情况的。 解决方法,在测试文件中,产生信号的那个initial里,先加1个单位的延时。 如下图(目标是让en和clk的变化沿有差异):

明德扬科技教育 明德扬科技教育

|