当今社会无线通信迅猛发展,无线通信用户激增,要解决通信系统容量、带宽限制等这些严重问题的一个关键技术就是多天线通信技术。

这项技术的使用能大幅度地提高无线通信系统的频谱效率和链路可靠性,

与单天线系统相比,用多天线系统发射和接收信号能获得阵列增益(或称波束形成增益)、分集增益、多路复用增益和干扰抑制等优势。

然而多天线技术带来诸多优势的同时会不可避免地引起通道不一致性问题[1]。

在实际工程应用中,阵列接收机的多个通道由于PCB(印制电路板)走线长度不等、通道特性存在差异等硬件的非理想因素,

导致多个通道接收到的信号存在差异,典型情况为多通道信号存在相位差,通道校正即通过通道校正算法,将多通道信号进行修正,使其差异缩小为一个可接收范围。

本文在现代通信系统数据传输速度极大提高的背景下,提出一种基于Xilinx Virtex-5 FPGA的高速通道校正的实现方案,

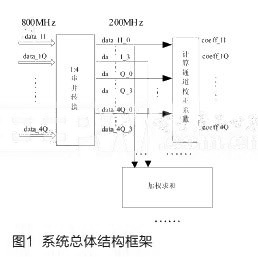

通过使用可靠的片内高速串并转换器ISERDES[2-3],将8路800MHz输入信号转换为32路200MHz信号,

进一步完成通道校正系数计算、加权求和等操作,从而实现800MHz的通道校正实现。

降低信号处理速度方法

由于FPGA内部集成的乘法器、加法器等IP CORE(知识产权核)运算速度最高仅有550MHz[3],在实际应用中为保证运算的稳定性,

一般采取低于300MHz的运算速度,要实现速度高达800MHz的运算速度,必须使用降低数据速率的方法。

本文中使用赛灵思(Xilinx)公司在其产品Virtex-5中集成的高速串并转换器(ISERDES),

它是为需要高速数据采集等应用开发的专用模块,能够提供高速的I/O处理能力,不受FPGA内部资源的限制,不占用系统逻辑资源[2]。

通过对ISERDES各参数端口进行配置,使其满足实际应用,本文实现将800MHz的输入数据实现1:4串并转换,并行输出的数据速率为200MHz。

整个系统结构框图如图1所示。系统包括:串并转换、计算通道校正系数、加权求和三个子模块构成。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8.射频前端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

需要了解相关信息可以联系:吴老师18022857217(微信同号)