基于FFT算法的电力系统谐波检测装置,大多采用DSP芯片设计。

DSP芯片是采用哈佛结构设计的一种CPU,运算能力很强,速度很快;但是其顺序 执行的模式限制了其进行FFT运算的速度。

而现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)在近年来获得了突飞猛进的发展,目前已成为实现数字系统的主流平台之一。

与DSP相比,FPGA最大的优势就是可以进行并行计算。在进行FFT 这类并行运算为主的算法时,采用FPGA的优势不言而喻。

用FPGA实现FFT算法进行谐波检测成为了一大热点。

以往FPGA的设计主要依靠硬件描述语言来完成。Xilinx公司推出了专门针对实现DSP的设计软件—System Generator。

在使用FPGA为原型平台运行算法时,它不仅能够对硬件的真实情况进行仿真,还能够自动生成硬件实现所需要的硬件描述语言代码。

与语 言设计相比,使用System Generator有三大优势:

第一,图形化操作,简单易用;

第二,实现的算法能确保与仿真结果相符;

第三,无需为仿真和实现建立不同的模型。

因此,利用 System Generator可以大幅度减少用FPGA设计DSP的工作量,缩短开发周期。

1 基于FPGA的谐波检测模型的设计

系统总体结构如图1所示。

(1)采样电路部分:包括互感器及滤波电路、锁相倍频电路和A/D转换电路。

待测电压、电流信号经互感器调理电路转化成便于采样的低压信号,

经滤波器滤除检测范围外的高次谐波、高频干扰信号和噪声;然后进入A/D转换电路,

电压、电流的模拟信号转换成可以用于计算的数字信号。

锁相倍频电路用于跟踪待测信号的频率变化,以实现对信号的整周期采样。

(2)如图1所示,虚线框内部分由FPGA实现。最主要部分就是控制单元和FFT模块。

控制单元主要由状态机的形式实现,当接收到锁相倍频电路送来 的倍频信号时,驱动A/D转换器进行采样。

A/D转换器完成一次采样,先将数据送入到FIFO模块暂存,当数据达到进行FFT计算所需点数后,状态机控制 FIFO模块将数据送入FFT模块进行计算。

为保证数据由A/D转换电路进入FPGA时的同步,A/D转换电路中的时钟由FPGA对开发板上的时钟分频后 提供。

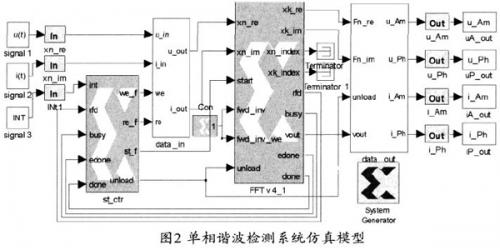

FPGA部分采用模块化的设计方法。在Simulink环境下搭建仿真模型,如图2所示。

模型的核心部分是FFT计算模块(FFT v4_1),围绕它设计了数据输入子系统data_in、数据输出子系统(data_out)和控制单元模块(st_ctr)。

用simulink中的信 号模块模拟出电压u(t)、电流信号i(t),考虑到后续数据输出控制的设计,预留了中断信号输入INT(signal 3),

为便于仿真,其间隔时间与采样时间同步。数据输入子系统主要用于对采样数据的转换和暂存, 数据输入子系统的主要包括scale模块、convert模块和FIFO模块。

数据输出子系统用于对FFT计算所得的结果进行处理,计算出电压、电流基波 及各次谐波的幅值和相位。

然后,搭建三相的电压、电流谐波检测模型(图3),其中包括了控制模块(ST_MA、da_out_ctr)和三个子系统A、B、C,每个子系统内 均有一个单相谐波检测模型。

控制模块ST_MA实现对整个模型运行时序的控制以及对硬件采样电路的控制;da_out_ctr用于控制数据的输出。

2 系统硬件电路设计

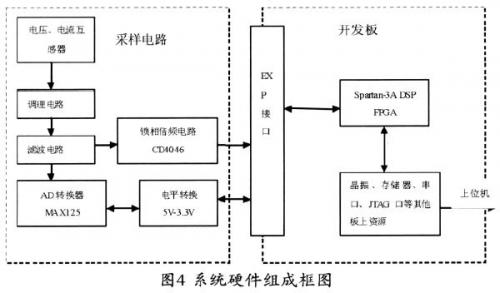

如图4所示,系统硬件由两大部分组成,分别是虚线框内的采样电路部分和开发板部分[6-7]。

本文采用的Spartan-3A DSP 入门级开发板是Xilinx公司出品的基于Spartan-3A DSP FPGA设计的一个开发平台。

采样电路实现对三相电压、电流的整周期同步采样,其设计尺寸与Spartan-3A DSP开发板相同,通过EXP接口实现与开发板的通信。

它包括:电压、电流互感器、调理电路、低通滤波电路、锁相倍频电路、AD转换器及电平转换电路。

3 硬件联合仿真与结果分析

3.1 硬件联合仿真

由于实验条件所限,本文采用的是单相220V的市电为检测对象。接入额定电压220V,标称功率800W的电加热器为负载。

首先用FLUKE434型电能 质量分析仪检测出该负载上的电压、电流的各次谐波参数,如表1所列,其电压总谐波畸变率THDV=4.9%,电流总谐波畸变率THDI=4.8%。

经采样后得到的数字信号量在0~5V之间,依照给定参数分别乘系数J、K,利用Simulink中模块生成一组表征电压、电流的数字信号作为系统的输入信号。如图5所示。

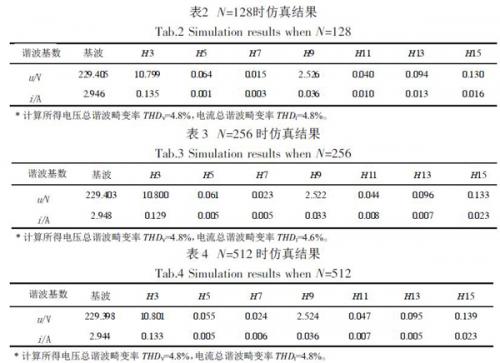

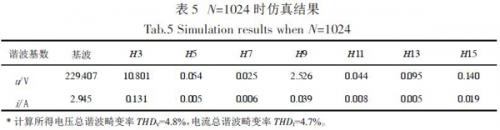

将FFT模块中的采样点数分别设置成为128、256、512、1024,并设置相应的采样频率,然后运行硬件联合仿真模型;将计算结果再乘系数1/J、1/K,得到表2~表5所示结果。

3.2 仿真结果分析

由各表中可以看出,计算出的幅值以及根据幅值计算所得总谐波畸变率的误差都比较小。

随着采样点数的增加,计算所得基波和较低次数的谐波幅值的误差和总谐波 畸变率的误差并没有明显减小,而次数较高的谐波误差减小较明显。

究其原因,N点FFT计算可以分解出0~N/2-1次谐波,N=128时就可以分解出63 次以内的谐波了。

而对于次数较高的谐波,采样点数的增加对其幅值误差的改善还是比较明显的。硬件实现时,在计算精度满足要求的情况下,考虑到实时性的要 求,可选用256点FFT进行计算。

此外,计算所得相位出现了很大的偏差;原本设想通过改变待测信号参数,分析仿真结果来推导出相位偏差的规律,

但是随着数值的改变,相位偏差规律并不 明显,并未达到预期目的。然而,在改变信号参数的分析过程中发现,

相位的改变对谐波幅值和总谐波畸变率的计算并没有太大影响,计算精度基本满足要求。

因 此,实际硬件实现时,舍弃掉相位计算,只计算出各次谐波的幅值及总谐波畸变率。

4 结束语

本文提出了一种采用基于Xilinx FPGA 实现FFT算法的电压、电流谐波检测的模块化的设计方法。

使用System Generator设计了谐波检测的模型及前端采样电路,并以Spartan-3A DSP开发板为平台进行了硬件联合仿真验证。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8.射频前端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

需要了解相关信息可以联系:吴老师18022857217(微信同号)