VIVADO使用教程——如果同学们的问题我们帖子里面没有的请第一时间联系我:QQ:3398694882,微信同步:18022857217吴老师,我们对新问题进行补充!

【关键问题!!!!重要!!!】VIVADO会在MESSAGE窗口出提示很多错误和警告信息!

但建议大家不要看此信息,原因如下:

1. 这些信息有可能是过时的,可能是之前报错了,因此修正了,这些信息没有更新。

2. 有些信息是错误的,但不影响整个工程的运行,例如某个IP核出错,但实际工程没使用此IP核。

3. 这些信息没有顺序,即哪些错误是先发生的不知道,影响定位。

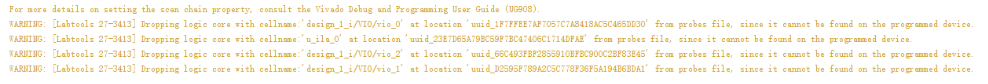

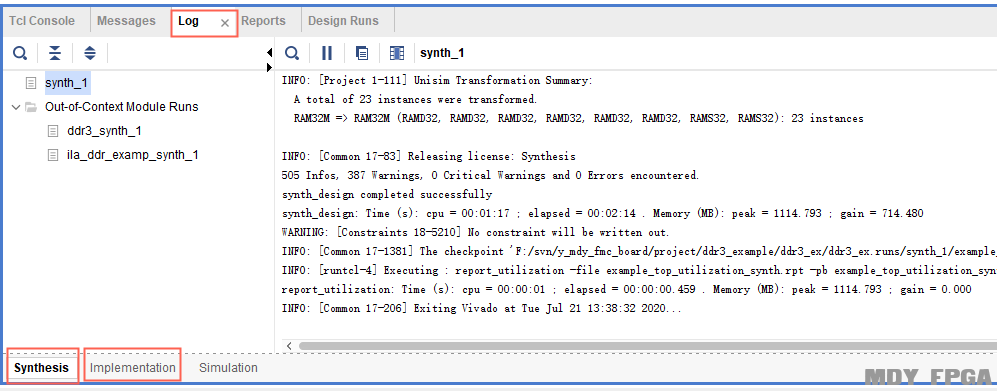

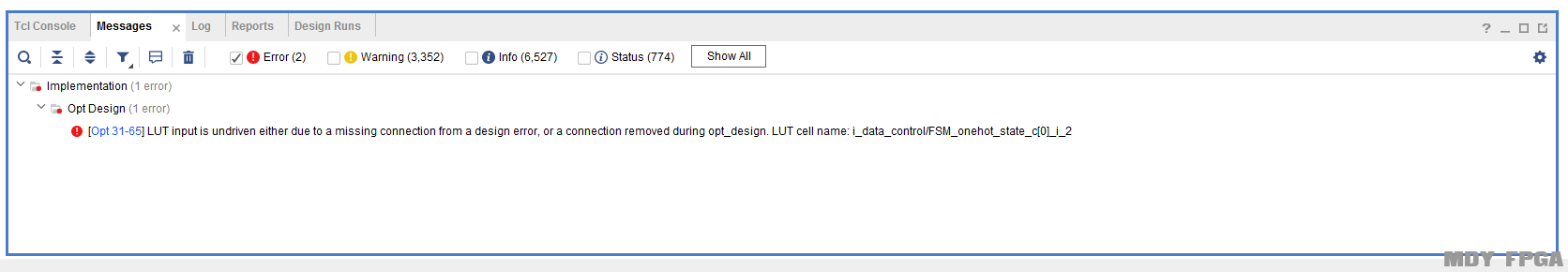

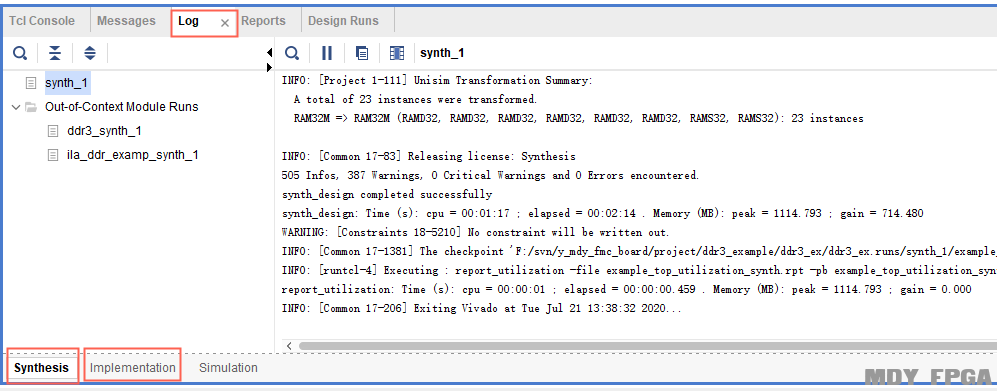

总之不要看MESSAGE栏的内容。最权威的信息,应该看LOG。如下图

要看LOG这一栏。 这一栏中,有Synthesis和Implementation这两部分内容。建议整个工程运行后,再看LOG中,第一个报错的地方,解决第一个报错的问题。

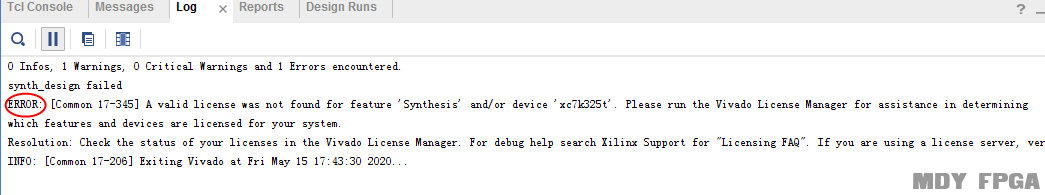

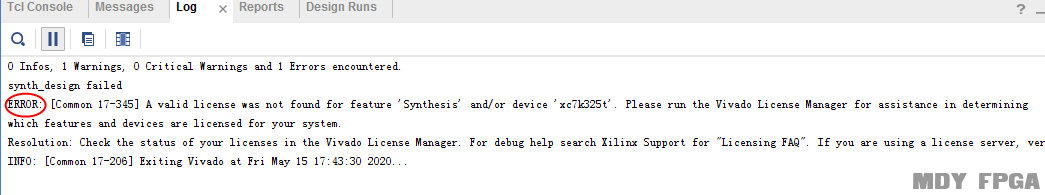

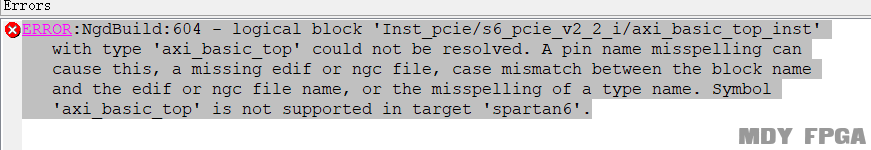

【问题1】使用VIVADO编译时出现如下错误,我使用的是K7芯片。

答:仔细阅读提示,该提示是说本软件没有K7芯片的license。您需要去官方下载一个K7芯片的LICENSE使用,该LICENSE是免费的。

LICENSE的申请方法,请参考:https://blog.csdn.net/wxh0000mm/article/details/84068162

注意,上面链接中讲的是申请VIVADO LICENSE的方法,本问题是指K7芯片的LICENSE,要选择时注意选正确。

【问题2】ILA报如下错误,大概意思是有一些信号没有连接。

The debug port 'u_ila_0/probe4' has 1 unconnected channels (bits). This will cause errors during implementation

答:1. 该报错是指ILA里有一些接口没有连接。您要检查一下例化时,是否全部的probe都已经连接了,

尤其需要注意的是:里面的每个probe位宽都要正确,也就是probe的位宽和信号位宽要一样。

2. 在message界面显示的是之前残留的信息,需要点一次reset synthesis run,重新RUN一遍,查看最新的提示信息。

【问题3】VIVAOD添加include文件报错。

答:一般include进来的文件,不是一个完整的module代码。该代码是不能像其他代码那样,通过添加文件的方式加到本工程,这是不正确的。

正确的方式是,在VIVADO的设置界面(在最左边的窗口,PROJECT MANAGER,点击setting),然后按下图设置。

如果还报错,注意要把该文件从工程中remove掉。

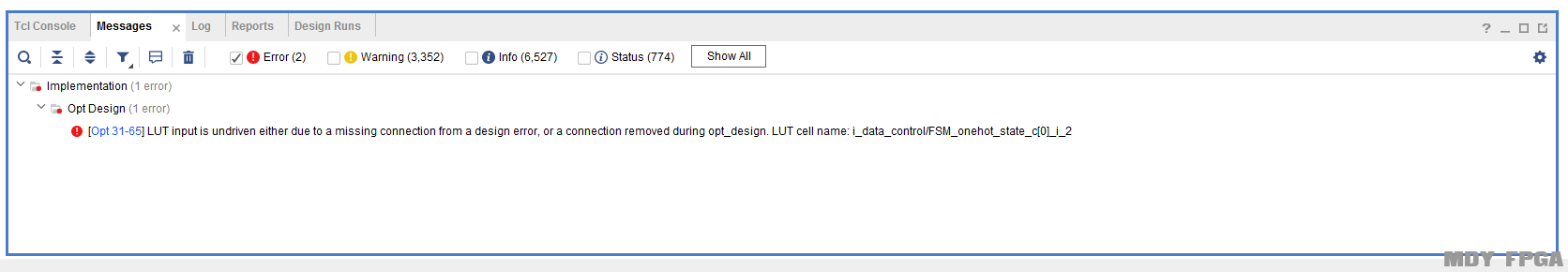

【问题4】不添加ILA,可以顺利生成bit流文件。添加ILA后,就在布局布线这里报错,这是什么原因呢?

答:使用ILA的时候,特别注意ILA的信号个数、信号位宽要与被测信号一致,否则会存在编译不通过的风险

像这种错误提示,如果看不懂,则看关键词和提示的信号。如上图中的FSM_onehot_state_c[0]信号,从代码上检查该信号是否存在以下问题。

1. 该信号是不是没有被驱动(也就是没被赋值);

2. 该信号是不是被 优化(包括直接或者间接未被使用);

3. 信号位宽不正确;

4. 该信号与其他信号有哪些不同。

5. 再不行,尝试改改该信号信号,重新综合看

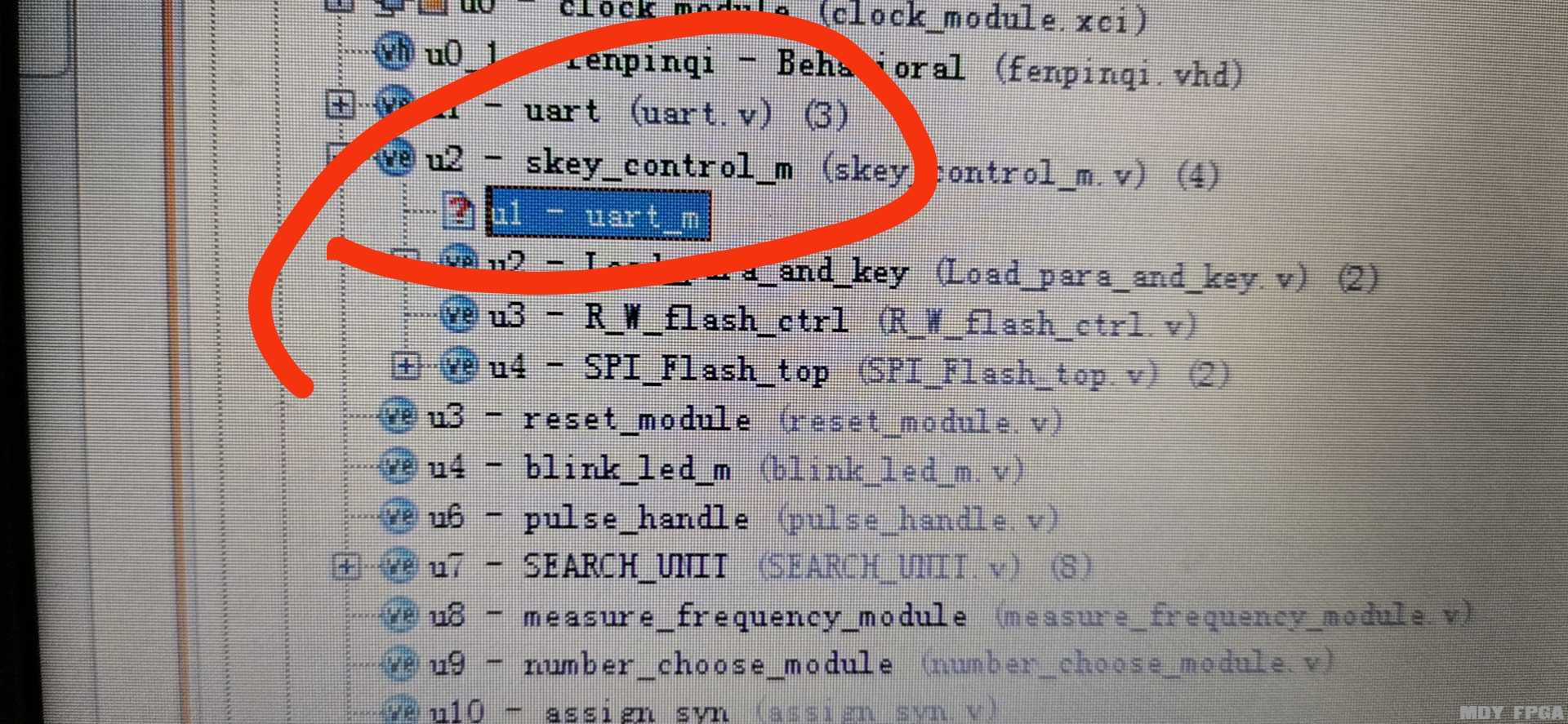

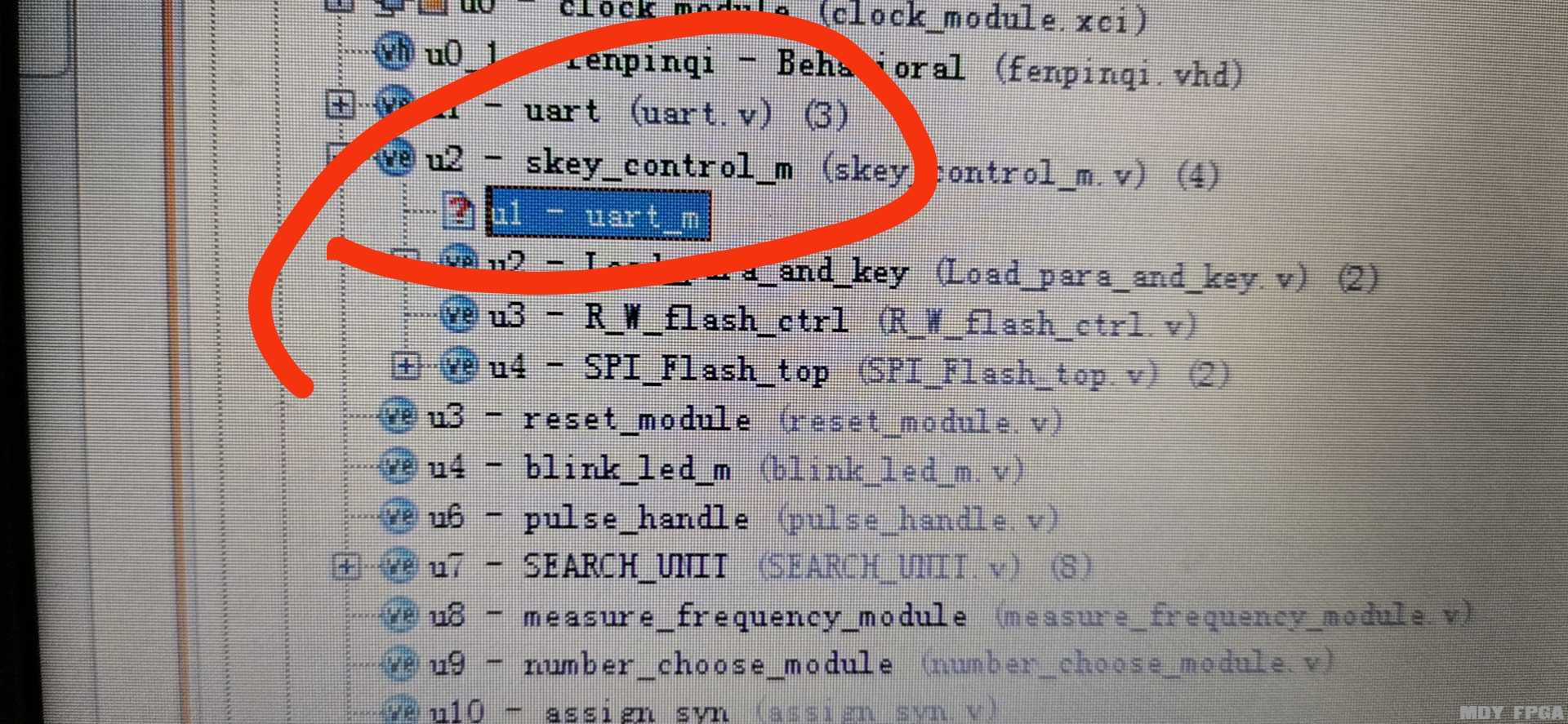

【问题5】以下图片出现?号问题是怎么回事?

答:出现问号,是表示该文件没有添加到文件,请把该代码添加到工程

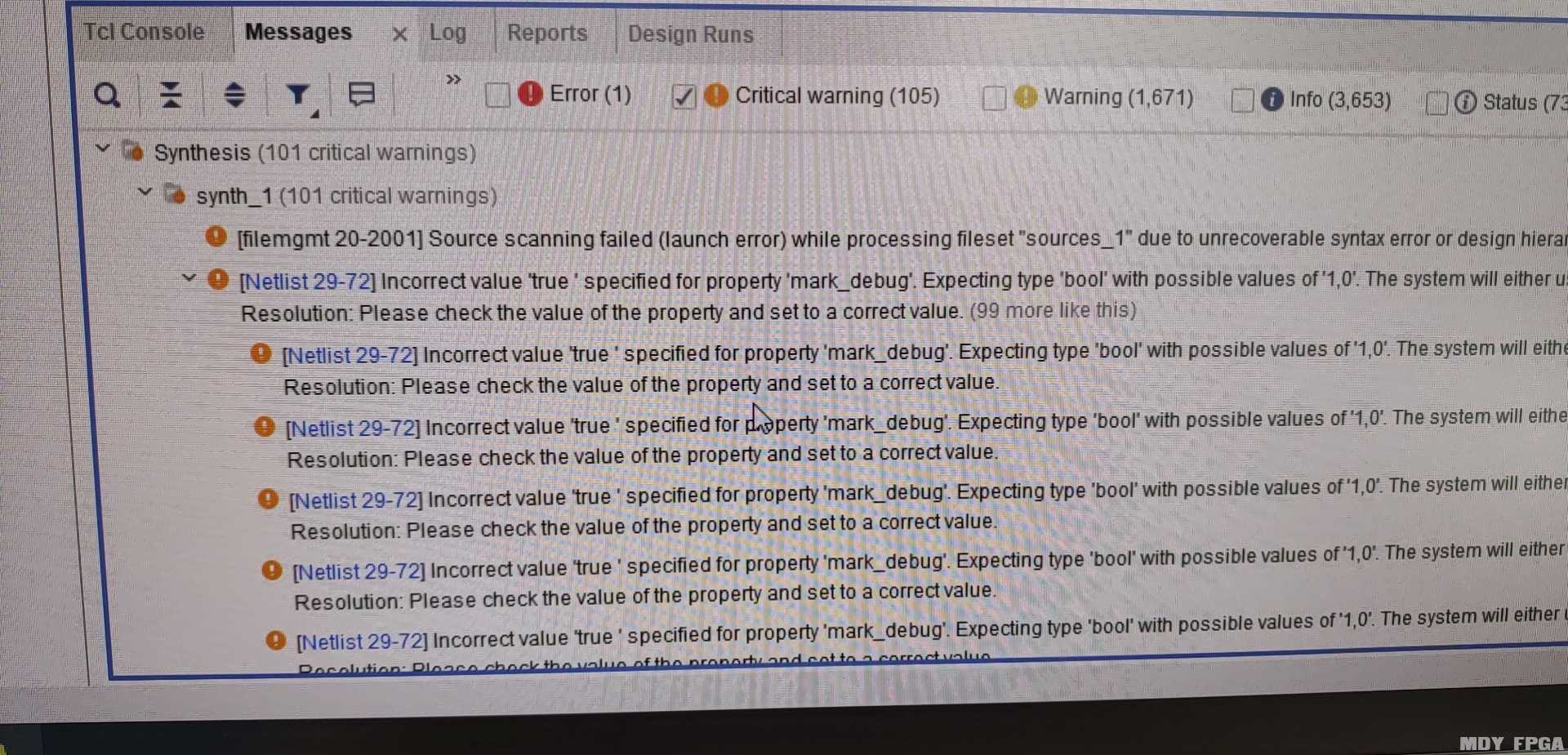

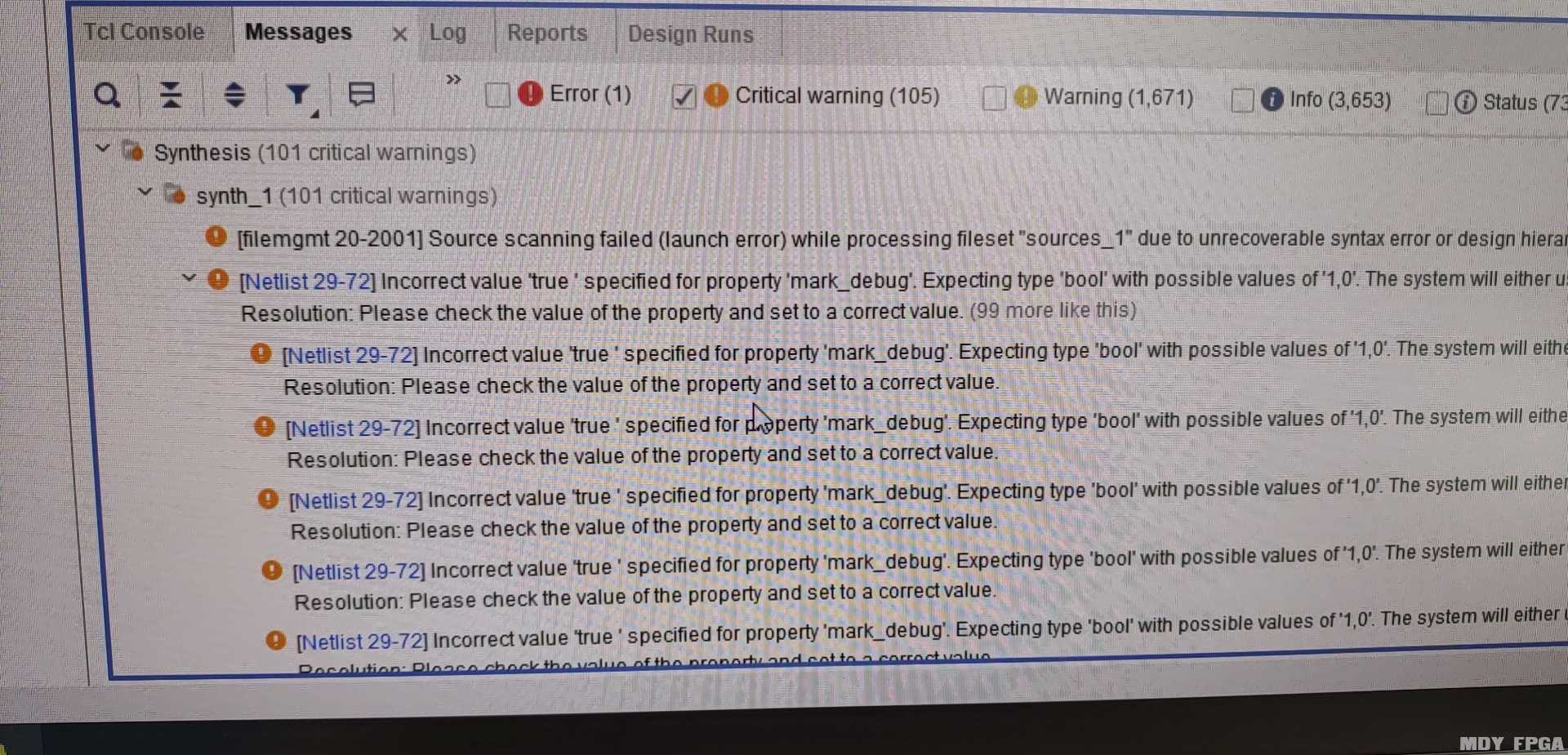

【问题6】 出现以下警告 Synthesis(101 critical warnings),请问如何解决?

答:拉信号到调试工具引起的警告,MDY不使用此方法,所以没遇到过。建议使用例化ILA的方法,我们已经形成了一套规范方法,有兴趣可以看下面链接 :

VIVADO使用教程:http://old.mdy-edu.com/wentijieda/20210409/1209.html?1617940294 请看 第六集:VIVADO教程06-MDY的ILA使用经验

【问题7】 出现器件识别不到有如下可能原因,如下图所示,请问是什么原因 ?

答:

1.下载器有问题,可以换一个下载器看看。

2.硬件电路有问题,需要检查。

3.电源未开。

4.下载器插反了。

5.FPGA芯片有问题,以上是可能原因。

【问题8】老师,什么情况下不用sdk?

答:只有纯逻辑设计,没有用到软核和ARM的时候,可以不用sdk。

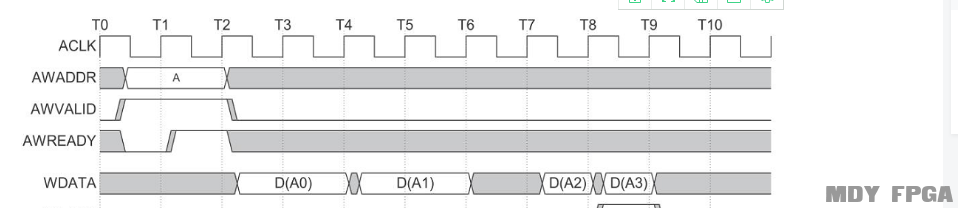

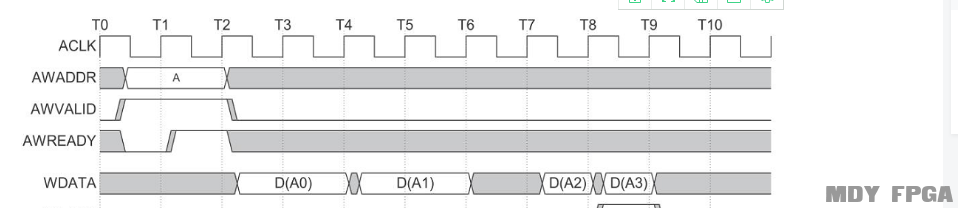

【问题9】下面是AXI总线的时序图,但我仿真发现,在AWVALID之前,AWREADY就变高了,这是错误的吗?

答:上面时序没有说,在AWVALID之后,AWREADY才为1。上图只是要说明的是:AWVALID和AWREADY同时为1,才表示一个有效的数据。AWREADY是可以任意时候为1的。 这也告诉我们,时序不要想当然地理解。

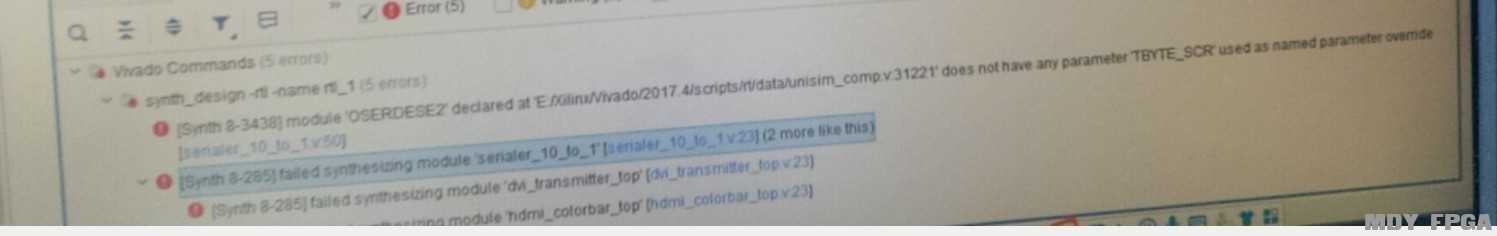

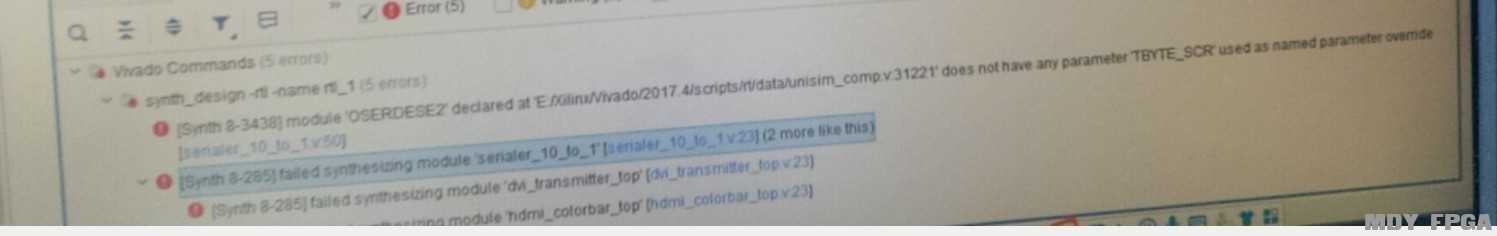

【问题10】Vivado-Synthesis: Verilog parameter overridden within instantiation fails with "ERROR:[Synth 8-3438]"

答:这句提示是说:在例化的时候,参数TBYTE_SCR在设计文件里找不到。即原设计文件里没有TBYTE_SCR,但例化的时候又使用了。

【问题11】布线里route design跑很久,不知是什么回事?

答:1.使用增量编译的方法,会节省一些时间。具体做法可以百度;

2.换一台性能更好的电脑。

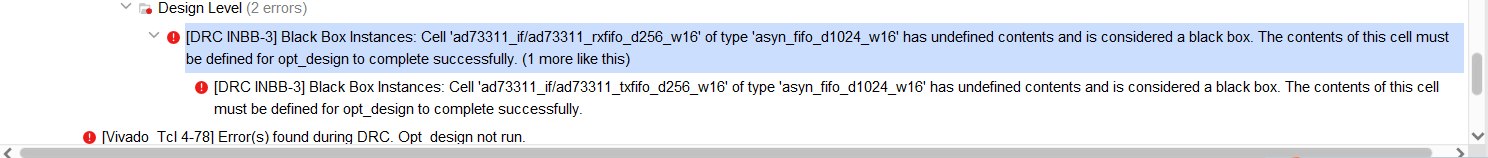

【问题12】在布局布线时,提示DRC错误,错误如下图。

答:看提示,一般抓关键词。注意图中的关键词:bank 14,rst_n,LVCMOS25,si5388_scl,LVCMOS33。在开发过程,要和这些词关联起来的步骤就是配置管脚,并且这些管脚与BANK14有关。

所以根据提示,可以去检查配置管脚的页面。

其实这里的问题是:在同一个BANK的管脚,其电压标准必须是相同的,例如都使用2.5V标准,或者都用3.3V标准。LVCMOS25是2.5V的,LVCMOS33是3.3V的。

解决方法:将rst_n配置成LVCMOS33,或者将si5388_scl配置成LVCMOS25

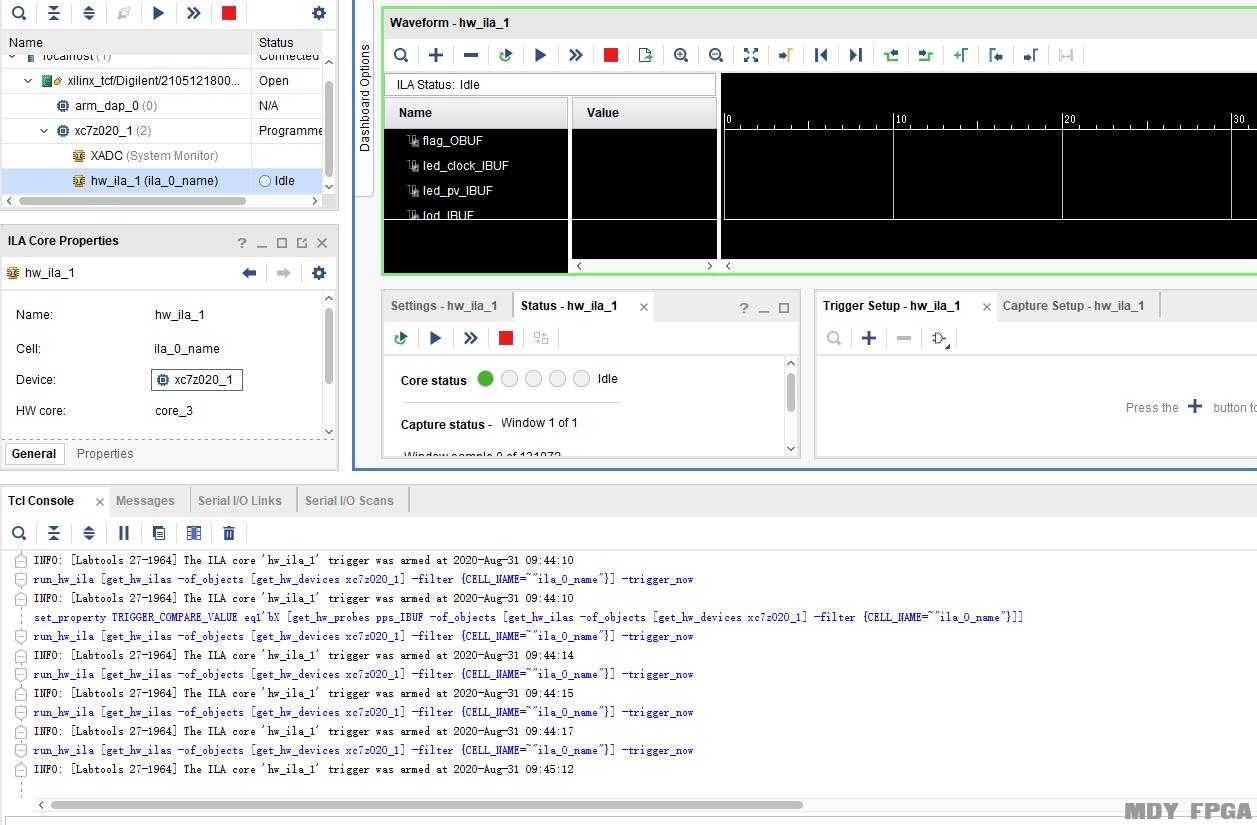

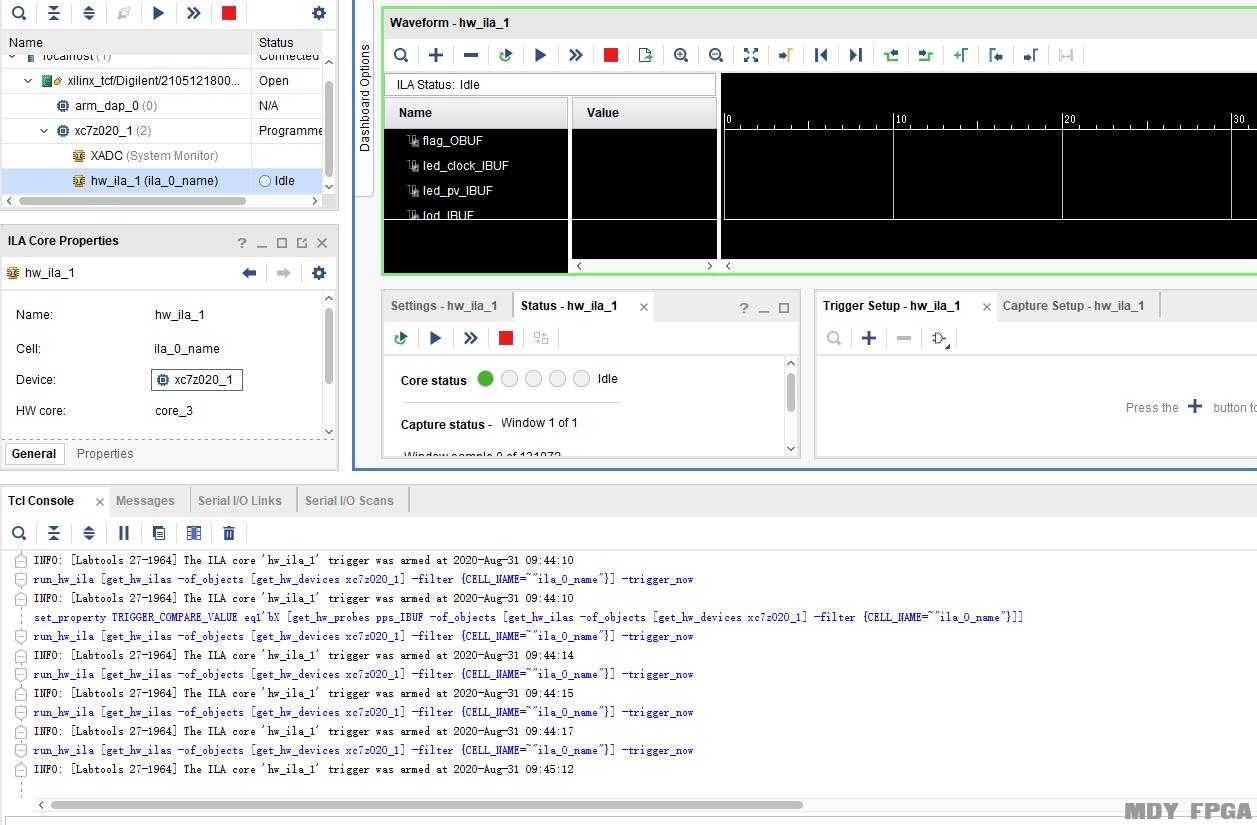

【问题13】老师使用ILA采样的时候 说明波形也没有 并且有这个警告是怎么回事啊-----Vivado INFO [Labtools 27-1964]

答:1、检查是否添加了siganls,并且您能够更早地看到它们,现在它们消失了?

2、可以关闭hw_ila1窗口,然后重新打开并检查是否可以看到任何信号吗?

如果不是,请单击“ +”按钮并手动添加信号。

同时点击立即触发并重新检查

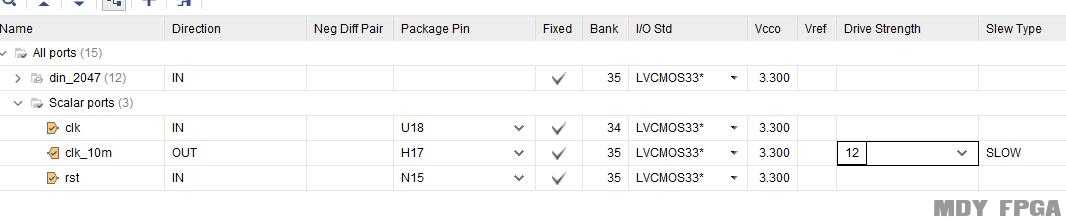

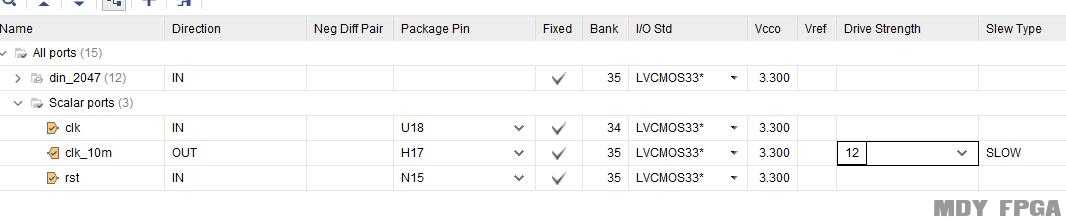

【问题14】老师这个管脚驱动强度是什么意思啊 选择的时候应该怎么选?

答:可以使用默认值,一直没改过

【问题15】我的iP显示锁定,更新IP怎么是locked by user

答:这是设计师对自己写的代码锁定了,其他人无法修改。所以这个就是直接使用即可。如果使用有问题,请找原设计师。

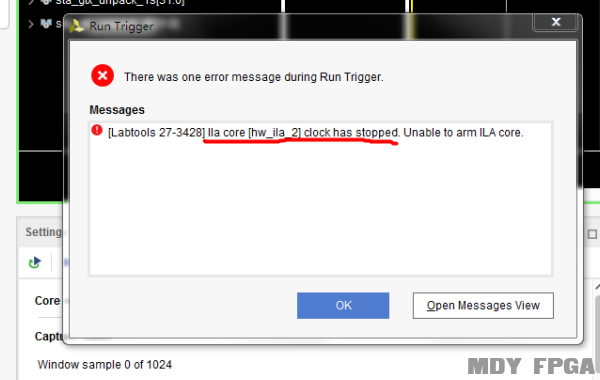

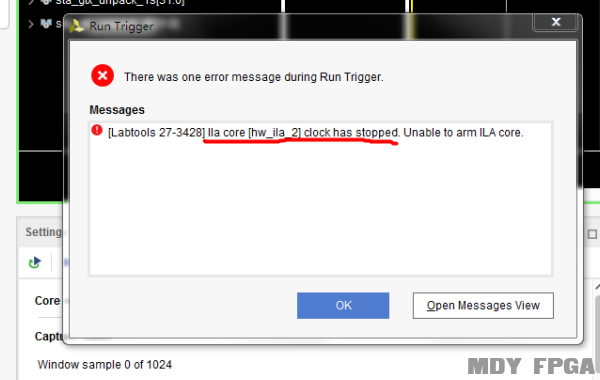

【问题16】使用VIVADO的DEBUG工具时,提示“clock has stopped,unable to arm ILA”

答:该提示是说,时钟信号停止了,也就是说上述做对中gtx_rx_clk没有像时钟那样,高低高低变化。请检查该信号,是不是拼写错误,还是说该时钟确实没有。

【问题17】Unrouted nets:4 net(s) are unrouted .The problem bus(es) and/or net(s) are............

答:出现这个错误的原因一般是:xdc文件中的约束不正确或者冲突,解决方法如下

1、根据实际使用情况重新进行约束

2、在将IOB属性更改为TRUE

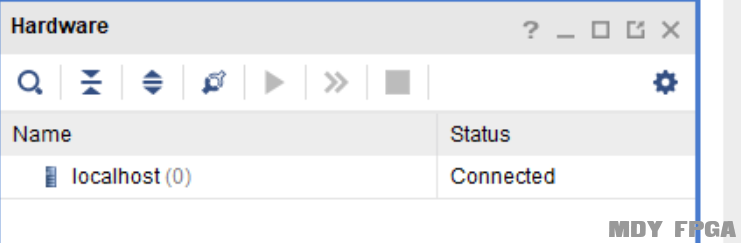

【问题18】:在vivado软件中烧写比特流时,打开硬件目标找不到JTAG,open target连接不上,

显示信息为:INFO: [Labtools 27-2285] Connecting to hw_server url TCP:localhost:3121

答:1.确认已经链接了下载器?

2.确认开发板已经通电状态?

3.有可能是下载器坏了,可以更换下载器看看?

4.有可能是板子硬件有问题 可以换板子试试看

5.有可能是Vivado的驱动没有安装好,只需要将驱动安装上即可,建议在安装的过程中,将vivado关闭以及Jtag连接器先拔掉,安装驱动成功后在重新开始打开vivado进行连接;

否则可能会在安装后也不能正常连接。在点击open target时,请将设备电源打开。

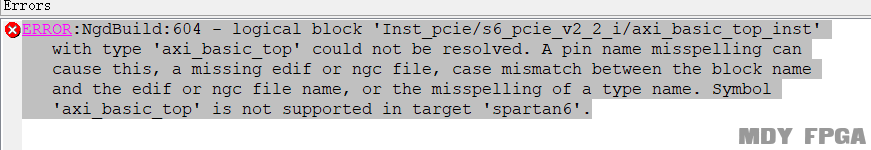

【问题19】

答:这是因为我们在添加文件时候,忘记添加NGC文件到工程目录中。下面就演示如何添加NGC文件到工程目录中。NGC文件既要添加到Synthesize的目录下,

也要添加到Implement目录下.

第一步:在Synthesize下添加NGC文件,如图在SynSynthesize中选择Process Properities

第二步:在到Implement目录下添加NGC文件,在Synthesis Options中可以看到-sd和-vlgincdir。

在-sd一栏中添加工程中所有的ngc或的edn文件的路径目录。在-vlgincdir中添加define.v文件的目录。

第二步:在到Implement目录下添加NGC文件

【问题20】打开MDY的工程后,会提示如下错误信息。

答:1. 工程中的路径,不要有中文的。

2. 上面提示是IP核找不到。但这些IP核有可能是没有用到的,所以这个错误可以不用理会。

【问题21】打开MDY的工程,IP核如下显示,无法打开。

答:MDY的工程,在分享的时候会减少大小,会删除很多无用的文件。用户下载后,需要重新生成IP核或升级IP核。

方法是在IP核右键,reset IP,然后重新“generate” IP。

另外,不同的VIVADO版本,也会造成此情况,要特别留意。VIVADO版本要保持一致。

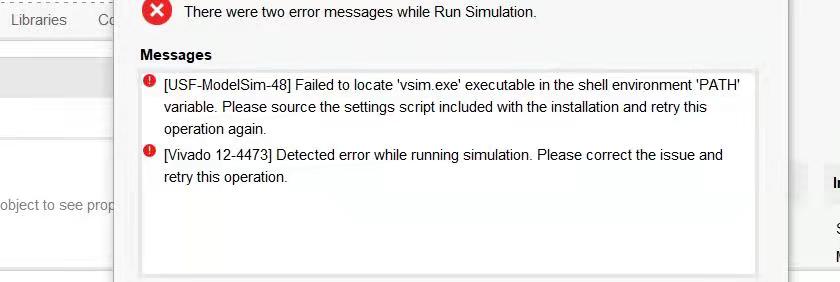

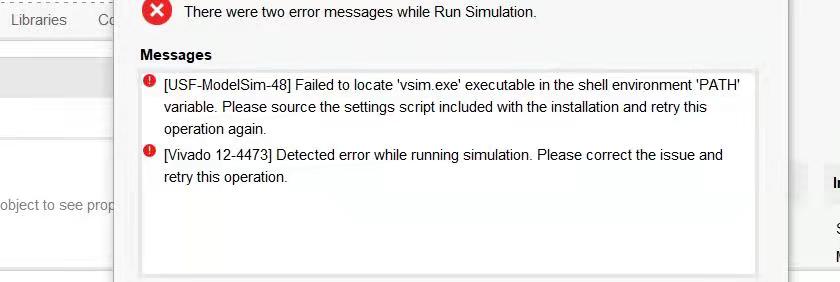

【问题22】请问使用vivado与modelsim联合仿真时遇到的图中问题怎么办?

答:信息是提示加载MODELSIM时出现错误,有以下排查方向,请仔细检查并排查

1. 在VIVADO中设置MODELSIM的路径,路径要填写正确,并仔细注意填写方式。

2. 注意MODELSIM的版本要正确

[问题23】请问Vivado在win10上安装打开后弹出error when launching 'E:XilinxVivado�7.3�in�ivado.bat':Launcher time out如图:

答:1. 找到(Vivado安装目录) 2017.3 bin unwrapped win64.o

2. 将' vivado.exe '重命名为' vivado.exe.backup ' (修改前记得备份)

3. 复制' vivado-vg.exe '并将其粘贴到当前相同的文件夹中

4. 将' vivado-vg - 副本.exe ' 重命名为' vivado.exe '

按如上方法尝试后,如果还是无法正常打开,请确保您已安装Microsoft Visual C ++ 2015。

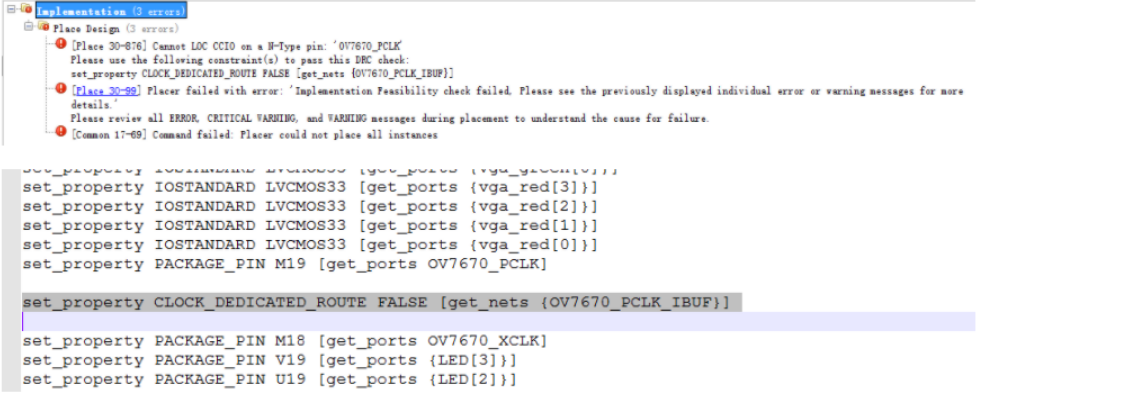

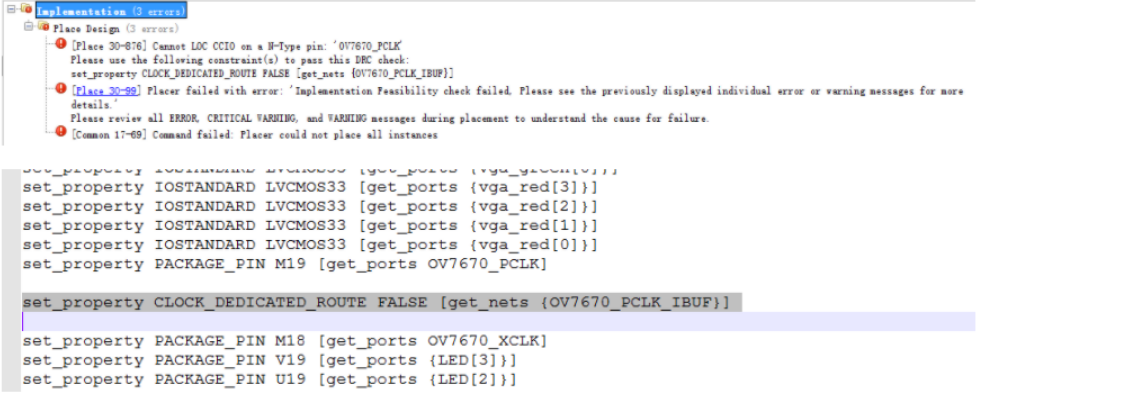

【问题24】请问Vivado的外部时钟输入问题怎么解决?

答:因为是IO管脚上,所以其周围没有全局时钟 BUFG,所以我们在 XDC 里使用:set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {OV7670_PCLK_IBUF}]

来屏蔽 Xilinx 的检测,从而通过编译。这个方式在软件提示的错误中也提供了解决方法

【问题25】请问Vivado工具中,怎么确定综合出来的电路能跑的最高频率?

答:目前没有找到方法。通常是添加时序约束,把需要的时钟约束上,然后看报告是否满足。

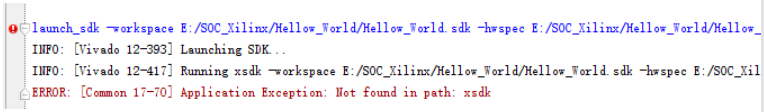

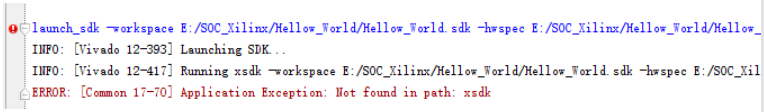

【问题26】[Common 12-70]Application Exception: Not found in path: xsdk

答:这个错误的原因是没有安装SDK,所以打不开SDK,可以找到vivado的安装包重新安装SDK.。

【问题27】Vivado编译怎么操作?用什么方法比较快?

答:1.Vivado编译起来相当的慢,这个方法可以提高编译速度,在VIVADO中一个run编译时支持的线程数如下表:(综合时一般是2线程)

2. 在tcl脚本处输入如下命令:设置多线程的命令为: set_param general.maxThreads 4,读取当前线程数的命令: 为get_param general.maxThreads

答:该代码被标黄了,表示存在语法错误或者不符合软件的编译综合规范,具体报错原因请查看编译报告。

【问题29】 如果出现以下情况是怎么回事?如图:

答:提示该bit文件不存在,所以请检查该文件是否存在

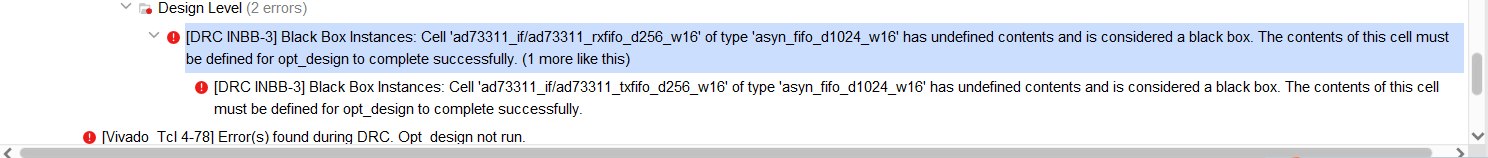

【问题30】:vivado error【DRC INBB-3】Black Box Instance......

答:报错的原因是设计文件没有找到的意思。需要检查该设计文件”asyn_fifo_d1024_w16“有没有添加进工程,如果没有,就添加。

【问题31】你们有没有遇到过 烧录进去之后 vivado测试模块的虚拟输入刷不出来的情况

关键词:vivado,烧录进去虚拟输入刷不出

答:我们也遇到过此问题,目前没找到根本原因。只是重新修改了ILA,重新编译后解决

【问题32】VIVADO打开打开ip核例程的时候报错这个一般是什么问题?

答:打开这个文件夹看看是否存在,如果文件存在,那就是路径名不要太长

|