|

Quartus教程 —— 如果同学们的问题我们帖子里面没有的请第一时间联系我:吴老师18022857217(微信同号),我们对新问题进行补充!

通过平时同学们反馈学习中经常用到的学习点,因此明德扬最近做了抖音系列短视频,都是一些FPGA学习技巧分享,大家感兴趣可以关注明德扬抖音号:87481069842,内容不断更新!记得关注点赞学习不迷路!

关键词:Quartus下载地址答:intel官网FPGA下载中心,Quartus所有版本都可以在此网址下载:https://www.intel.com/content/www/us/en/programmable/downloads/download-center.html

【问题1】QUARTUS打开后就闪退,怎么办?

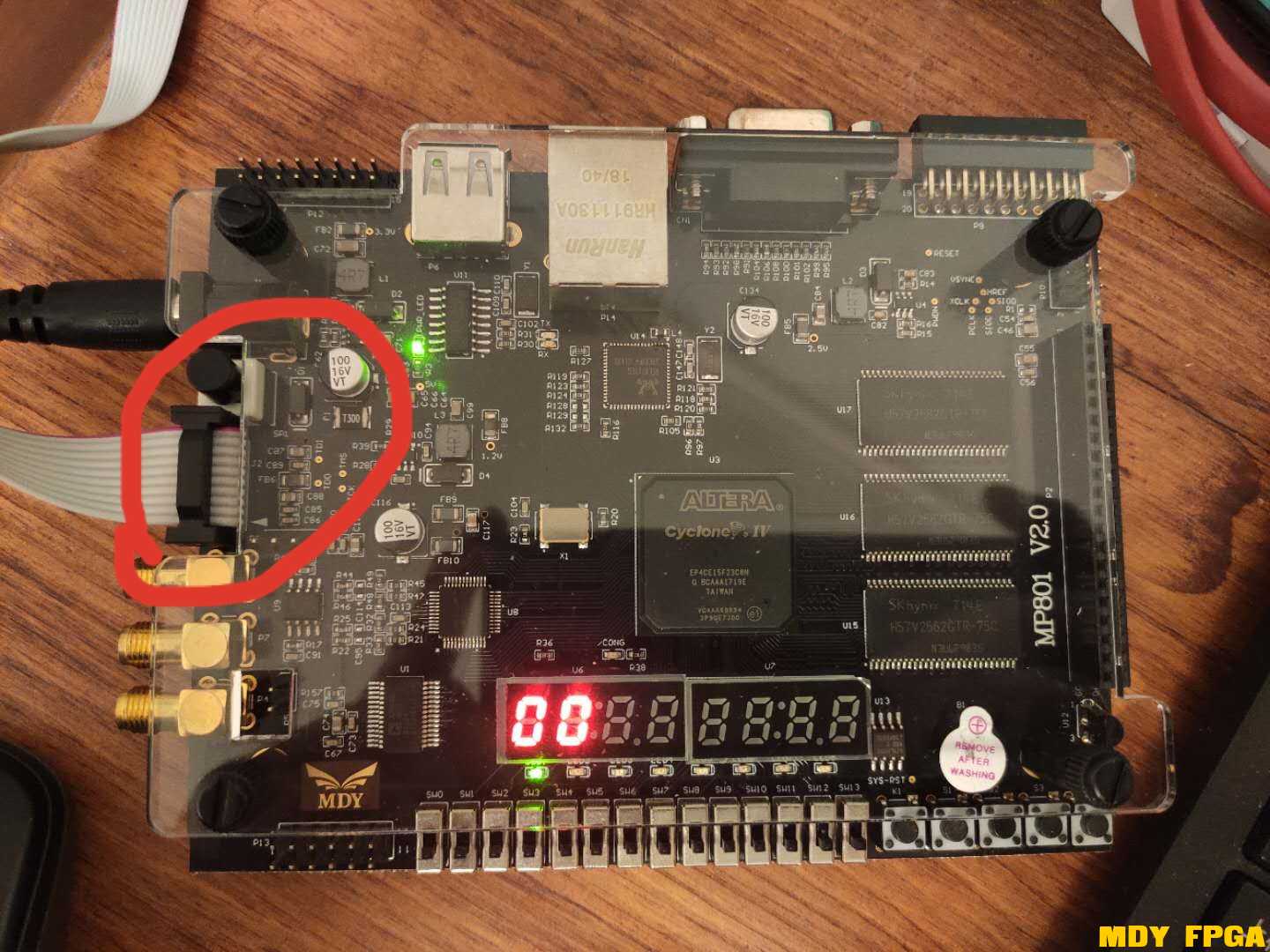

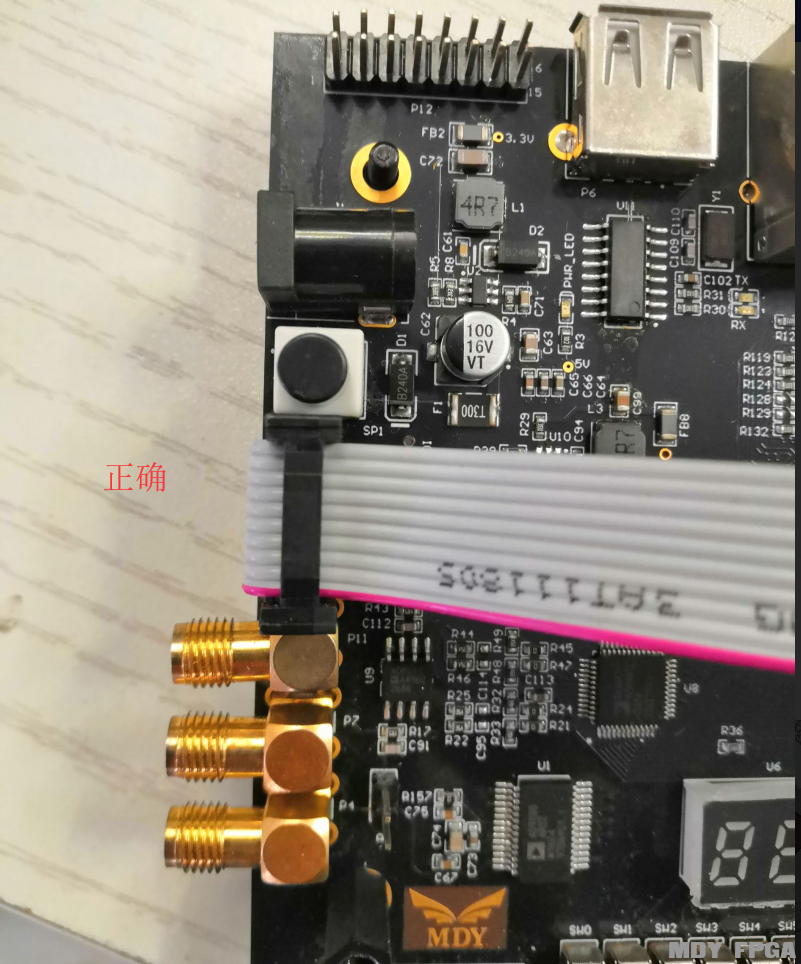

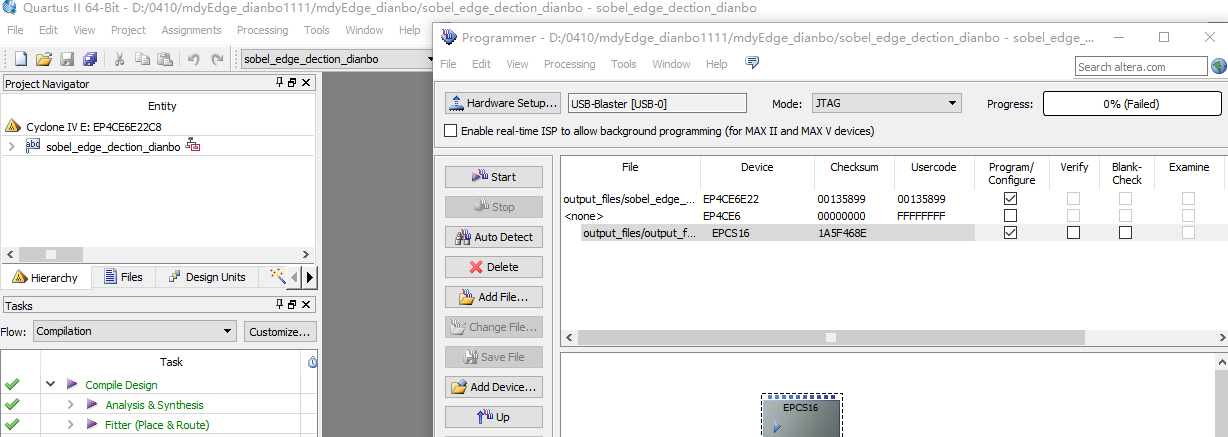

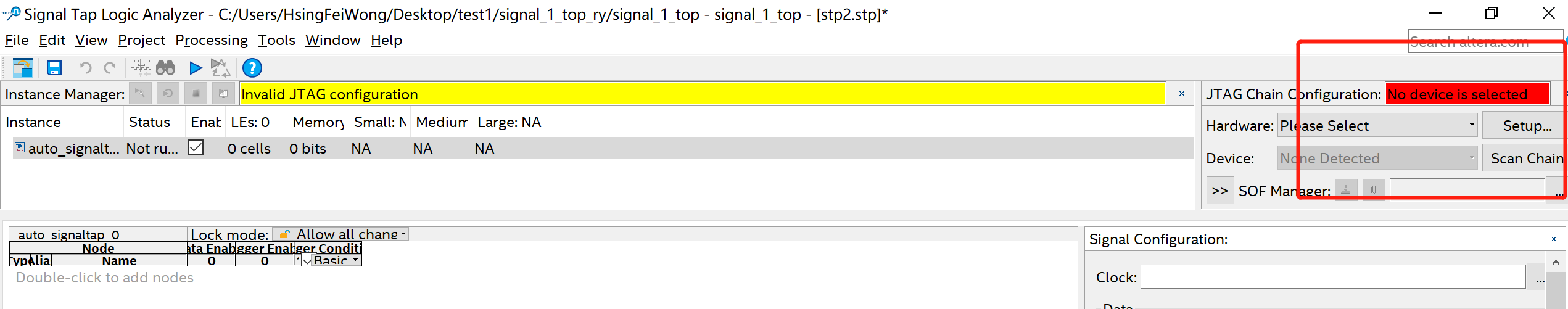

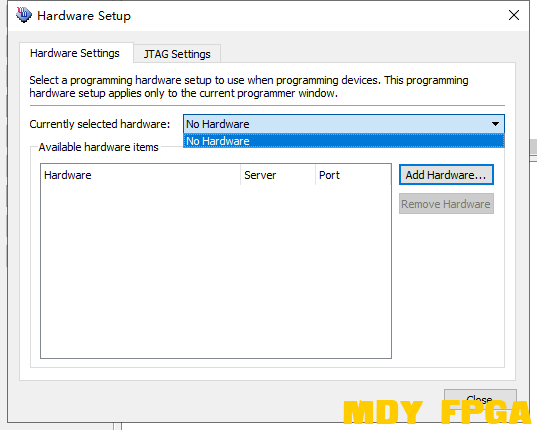

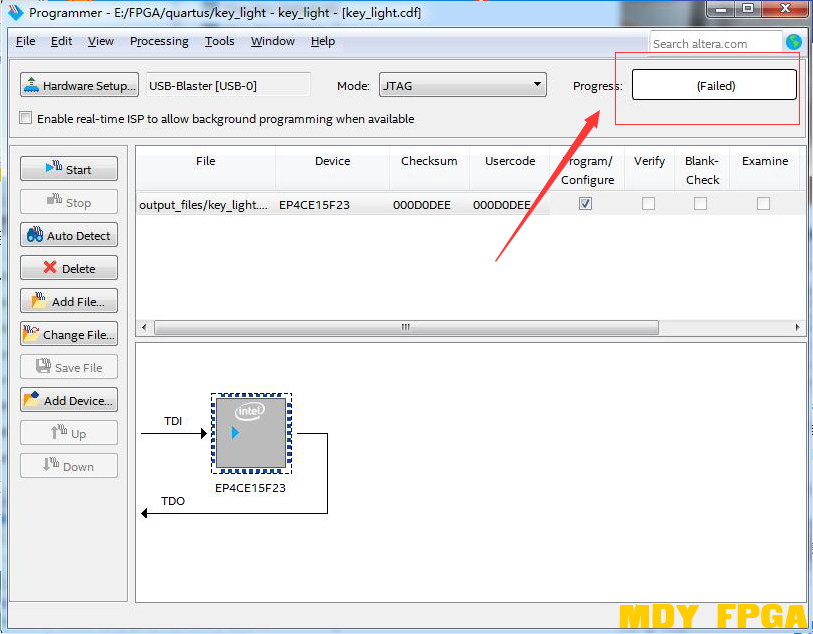

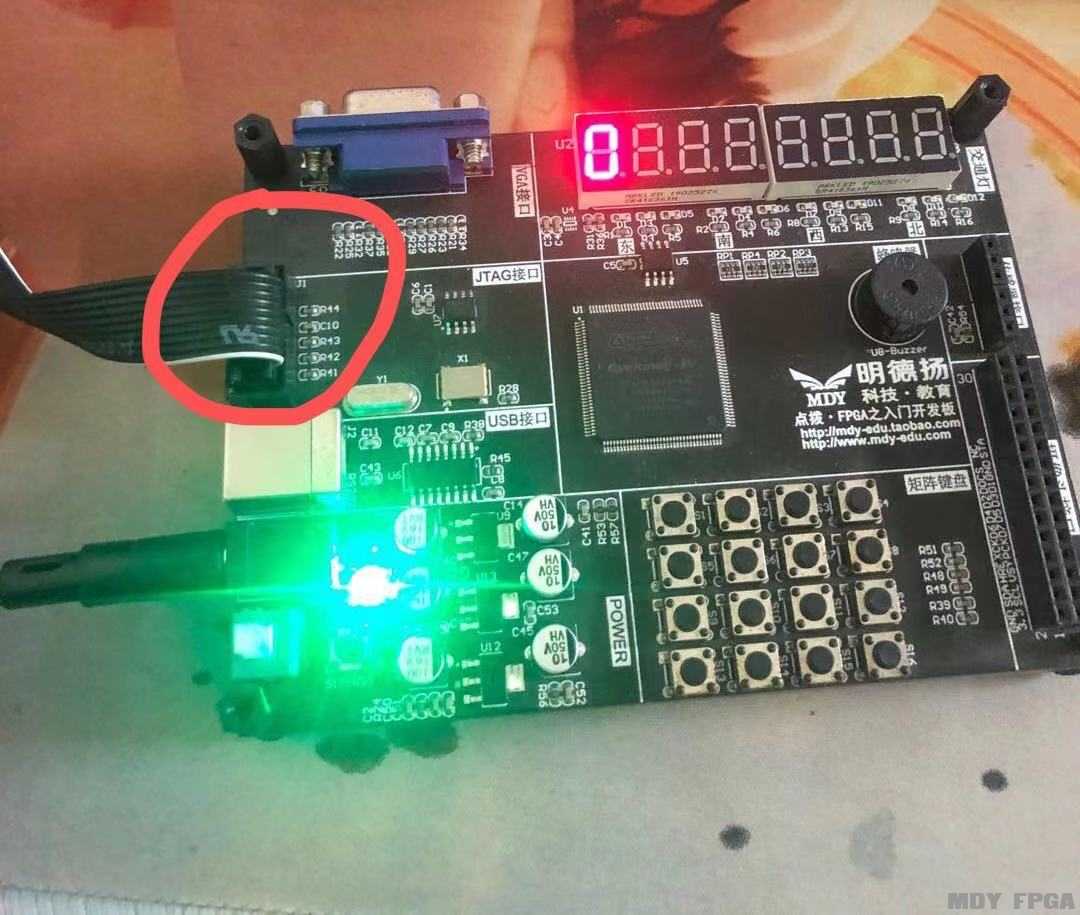

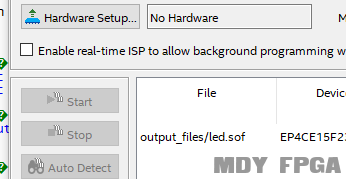

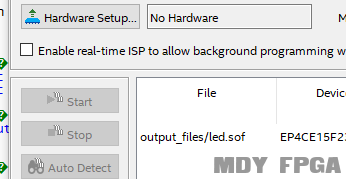

关键词:打开闪退 【问题2】下载时,没有找到下载器。如下图所示。 关键词:图中出现 No Hardware  答:请确认以下步骤 1. 需要连接下载器,即USB blaster 2. 确认JTAG头没有插反,请仔细对照图片确认。3. 确认开发板电源打开。 4. 如果还没有,请去电脑的设备管理器,检查是否有未安装驱动程序的硬件。如果有,请安装驱动程序,驱动程序搜索目录就是QUARTUS的安装目录。 5. USB电压太低,换一个USB口试试。6. 如果您电脑安装了多个版本的QUARTUS。那么需要到“设备管理器”,找到blaster,卸载掉当前的驱动程序,然后重装驱动程序。驱动程序搜索目录,就是您需要使用的那个版本的QUARTUS的安装目录。 【问题3】下载程序的时候,提示失败,如下图。 关键词:图中出现propress Failed  答:如果遇到下载失败的问题,请逐项检查。 1. 确保开发板电源处于打开状态。 2. 请确保下载器已经识别,具体见本贴前面的问题二。

3. 请确保下载器没有插反。下面左图是错误的插法,应该反过来插,红色的地在下面。 5. 如果仍然没有排除,请您找一下技术老师,注意把以上“步骤检查图片,一次性发给老师”。

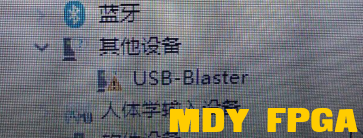

【问题3.1】连接USB-blaster下载器后,在设备管理器-通用串口总线 控制器,没有找到USB下载器。 关键词:USB-blaster下载器、设备管理器没有找 答:可以查看设备管理器-其它设备查询。如果还没有,请按以上步骤确认。

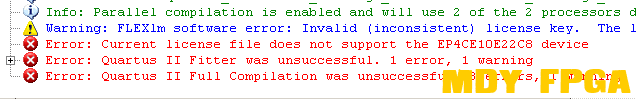

【问题4】Error: Current license file does not support the EPM240T100C5 device 。 关键词:not support

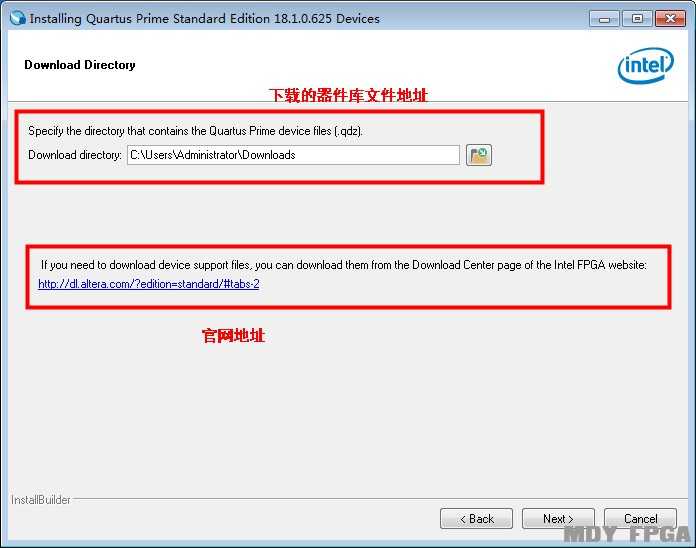

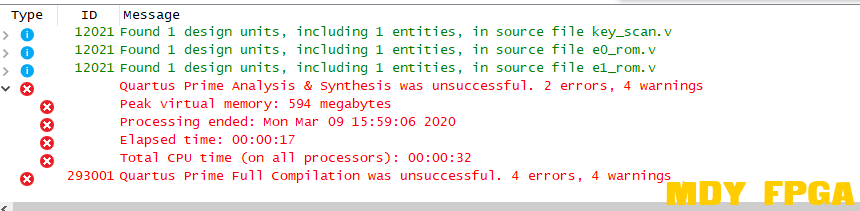

答: 2. 软件没有安装器件库,需要到官网下载您芯片的本: https://fpgasoftware.intel.com/18.1/?edition=lite&platform=windows 注意版本要正确。 【问题5】QUARTUS编译时出现如下问题。 关键词:peak virtual memory  答:1. 可能是路径问题:不能有中文路径或空格。 2. 可能是电脑内存不够,关闭QUARTUS,或者重启电脑试试。 【问题6】 设备管理器显示USB Blaster是感叹号。 关键词:USB Blaster、设备管理器、感叹号

答:

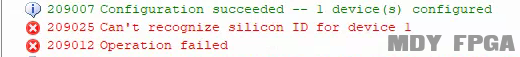

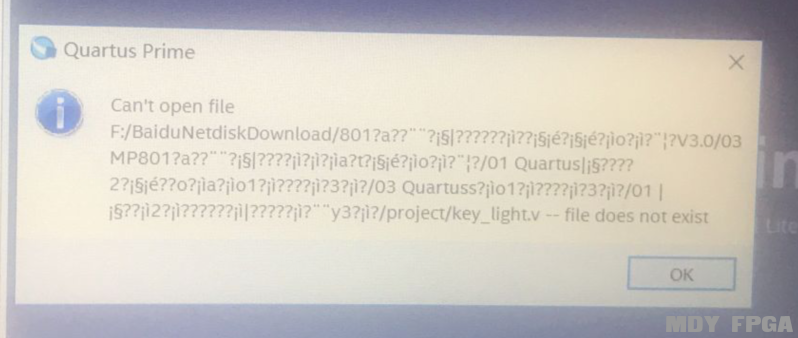

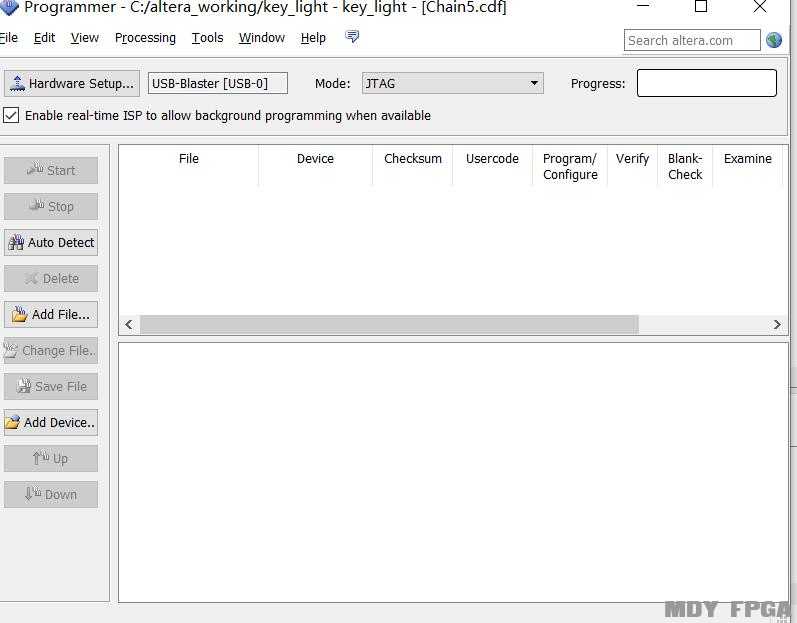

【问题7】 QUARTUS显示打不开文件,如下图所示。 关键词:很多乱码  答:文件和工程路径,不要有中文、空格和特殊符号。 【问题8】在下载的时候,如下图,start是灰色的。 关键词:图中Start图标是灰色  答:上图中没有添加SOF文件。可点击图中add file选项去添加sof格式文件。 1. sof格式文件,一般在该工程目录中可以找到。 2. 如果没有找到,请确保整个工程已经编译,正确编译之后会生成最终的文件xxx.sof。 【问题9】 烧录程序的时候,如下图,start是灰色的。 关键词:图中Start图标是灰色   答:如上图所示,需要点击Hardware Setup那里,选择USB BLASTER,就可以了。 【问题10】 烧录程序的时候,如下图,提示下载失败,并且提示: Error: Can't recognize silicon ID for device 1 关键词:烧录程序

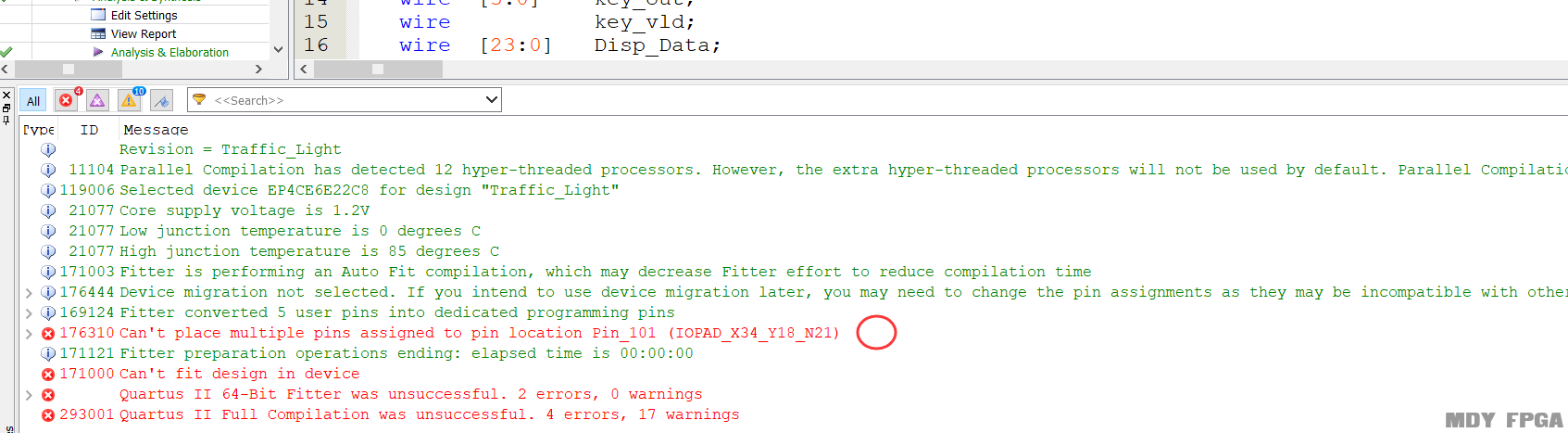

【问题11】 点拨板分配引脚后编译,提示无法将引脚分配到这个pin_101这个位置Error (176310): Can't place multiple pins assigned to pin location Pin_101 (IOPAD_X34_Y18_N21) 关键词:pin_101

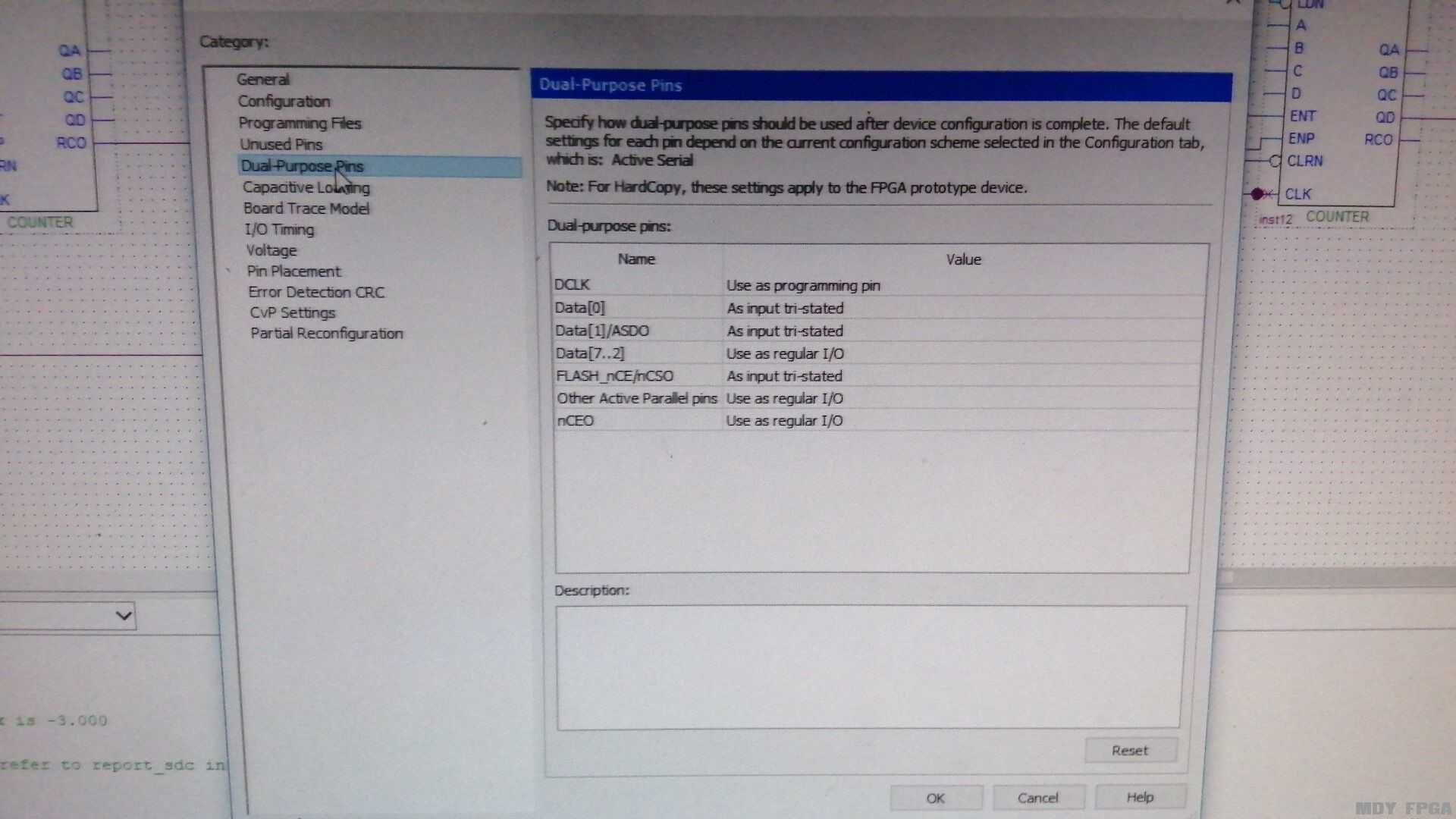

答:pin101是多用途管脚,需要设置才能使用。下面是设置方法:quartus中,assignment>>Device>>Device and pin options>>nCEO>>改为Use as aregular I/O即可解决。    【问题12】 遇到下载器驱动安装正确,设备管理器能够正确识别,但是Quartus软件就是无法检测到

关键词:无法找到下载器 【问题13】 烧录的时候,电脑就蓝屏。

关键词:烧录蓝屏

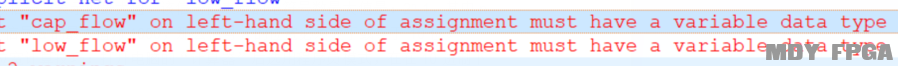

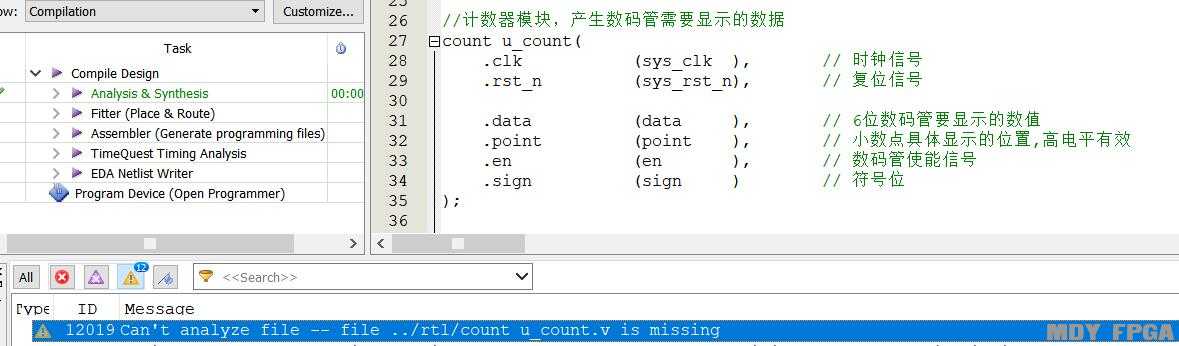

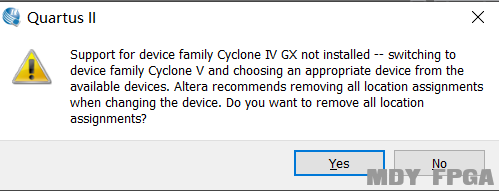

关键词:on left-hang side  答:一般都是信号类型定义出错,原来定义为wire改为reg,或者reg的改为wire,请看:http://old.mdy-edu.com/wentijieda/20210408/1196.html?1617934995 【问题15】 运行QUARTUS时,提示测试文件报错,如下图。 关键词:QUARTUS测试文件报错  答:QUARTUS是综合工具,它是把代码转成网表的。测试文件是不可综合的,它在MODELSIM中起作用。所以不要把测试文件加到QUARTUS来综合。 【问题16】综合的时候,提示文件找不到,如下图。 关键词:missing  答:一般不会错的,您需要检查文件是否直的在硬盘上,并且路径是正确的。注意,路径中的"../"表示的是当前目录的上一级目录。 【问题17】下图是什么提示? 关键词:not installed  答:QUARTUS没有安装Cyclone IV GX这个器件库。建议您去ALTERA官方下载此器件库并安装。

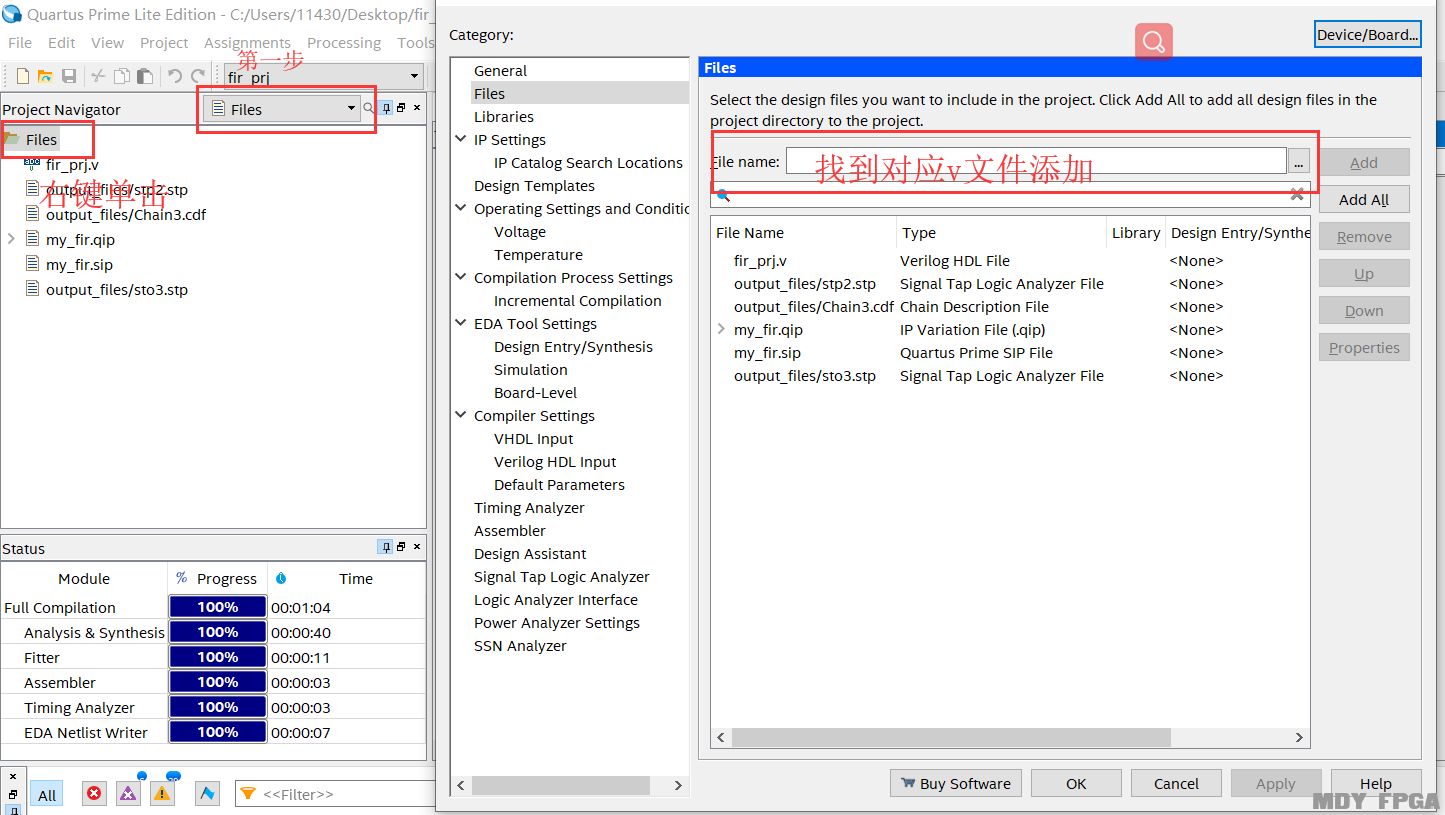

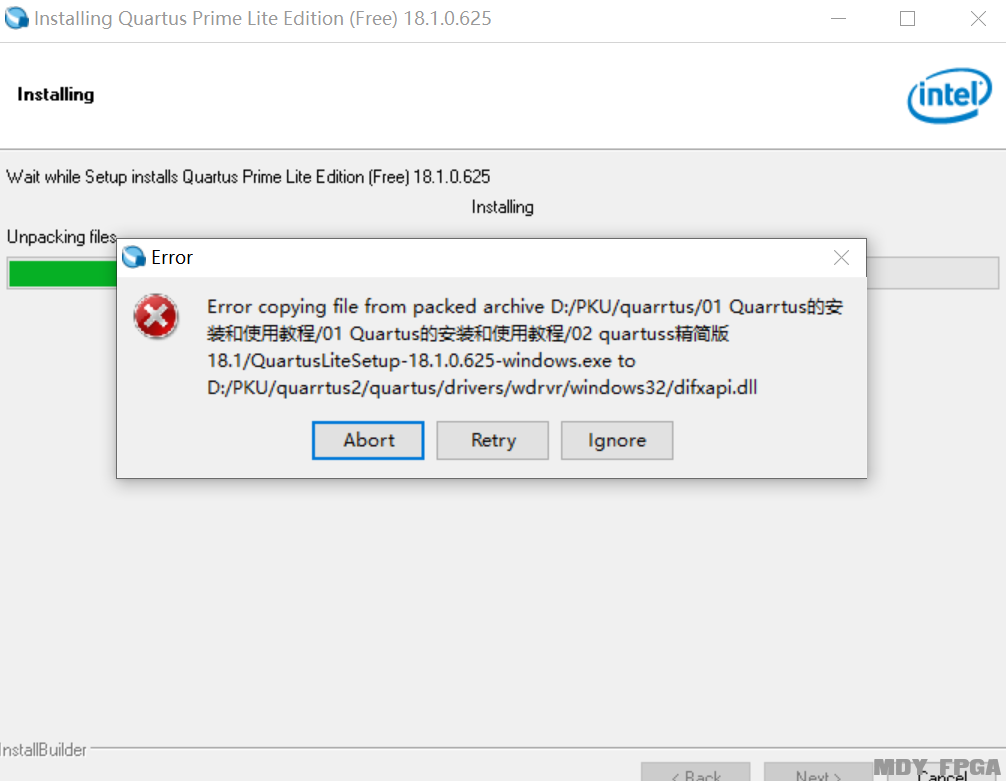

【问题18】总是出现这个问题 是什么原因:Error (262006): File "stp1.stp" is not a valid SignalTap II File -- ignoring 关键词:not a valid SignalTap II File 答:stp格式文件,是在线调试工具signaltap的文件。在开发时用来调试使用的。该文件不是设计的必要文件。MDY提供的部分工程,会将此文件删除。 因而QUARTUS在编译运行此工程的时候,如果该文件丢失,则会出现上面的提示,但该提示不影响工程的使用的,请放心。【问题19】在已经建好的工程中,增加新的功能模块,可以直接添加?如何添加? 关键词:添加模块/代码 答:只要顶层文件中已经例化这个模块,就可以添加,添加的方式请看下图 【问题20】Quartus 18.0版本在安装过程中遇到这样的错误(如下图),是什么原因? 关键词:Error:copy file from packed archive

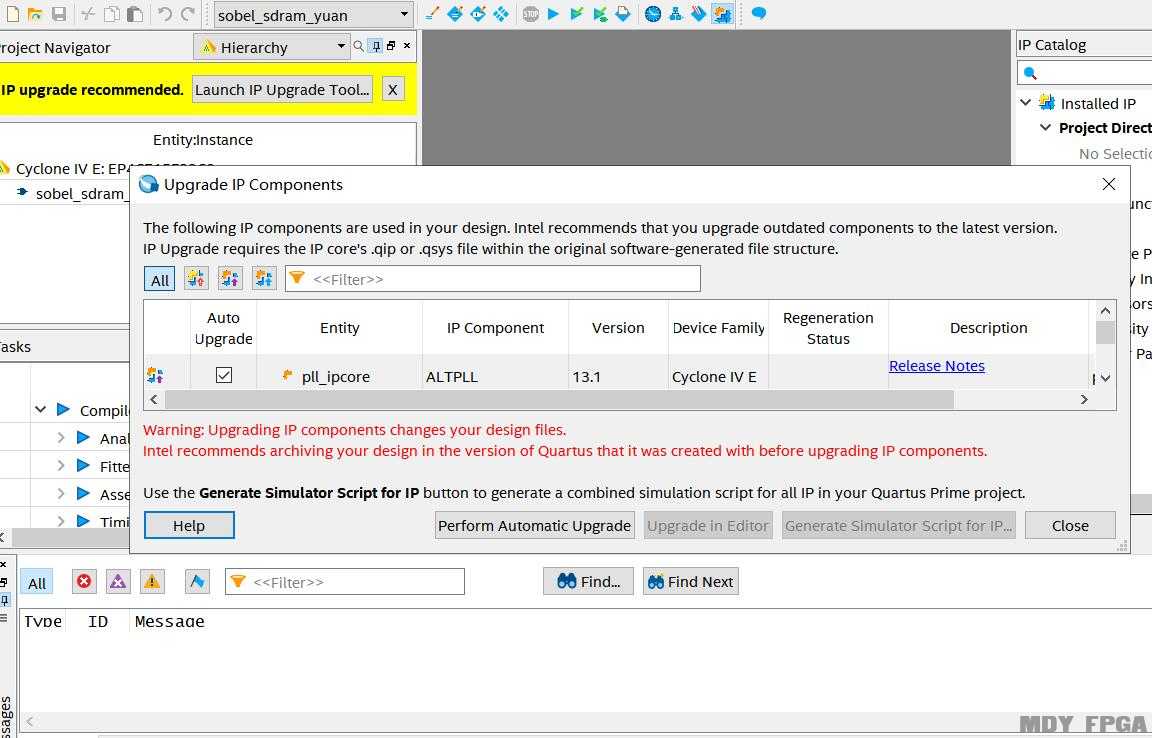

答: 【问题21】下载工程后,会提示升级IP核,但升级会报错 关键词:看到有update窗口,并有标红的文字  答:这是由于这个工程是由不同版本的QUARTUS建立的。由于官方的原因,某些IP核是升级不了的。但不升级,应该也能正常使用的。 【问题22】如何在QUARTUS查看工程的RTL视图。 关键词:查看RTL视图 答:工程编译后,在tools - Netlist_viewers - RTL viewer,可以看工程的RTL原理图。

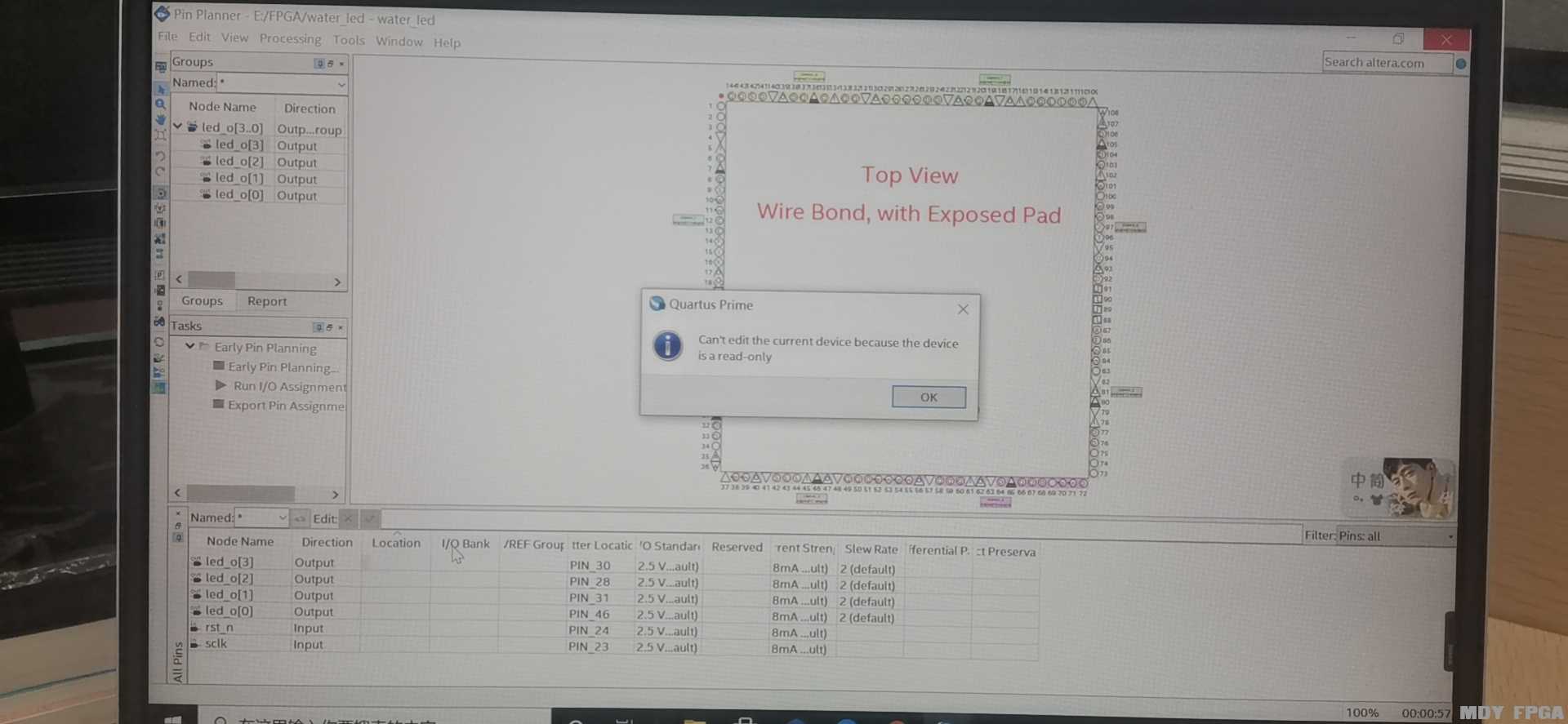

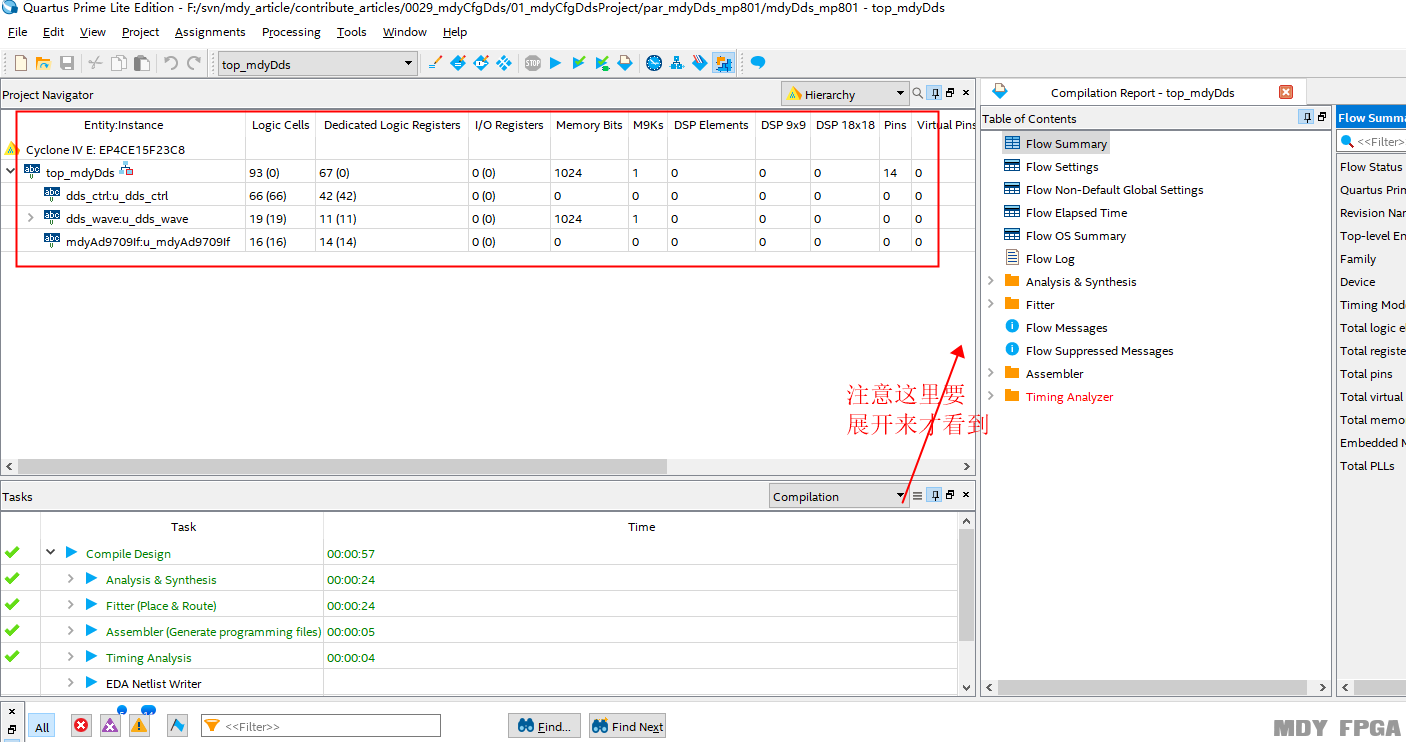

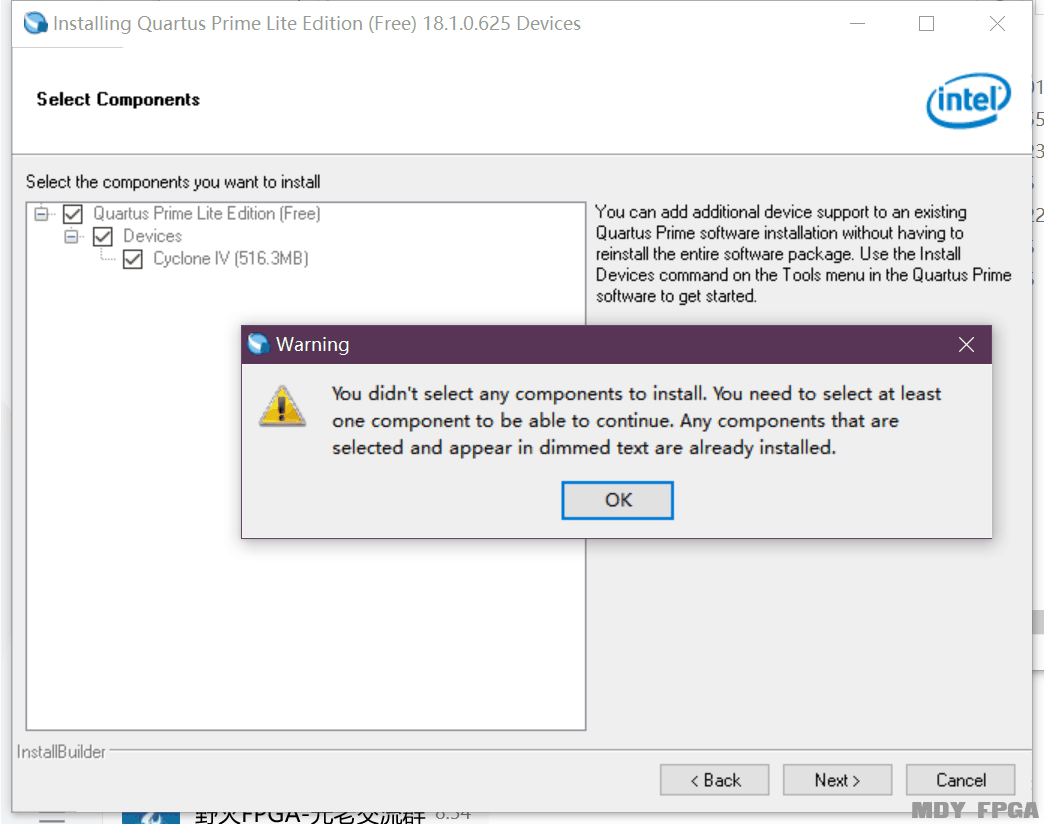

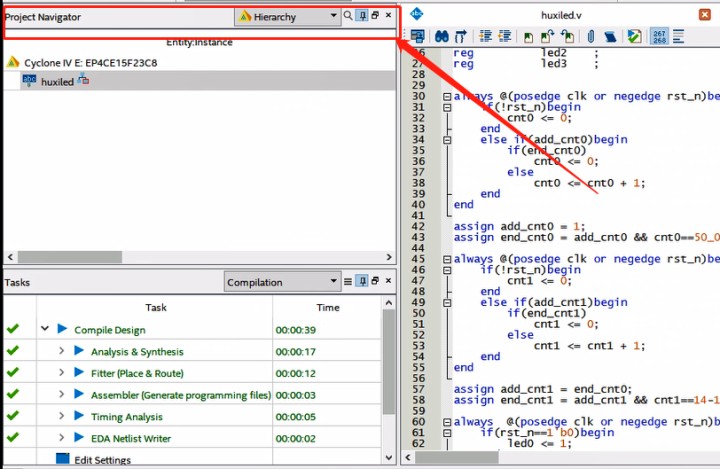

关键词:查看资源 答:对工程进行编译后,可以在如下图所示位置,查看资源情况。 【问题24】打开programmer的时候,弹出open file的窗口,是什么原因? 关键词:programmer弹出open file窗口 答:原因就是窗口重叠了,也就是programmer打开了两个【问题25】大佬们,quartusprime的精简版ip库和标准版有区别吗,三种版本除了支持的器件好像有差,没查到其他差别。 关键词:精简版/标准版区别 答:IP库是没有区分的。【问题26】要下新的19或20的prime的话,推荐下精简还是找破解的标准或专业版本? 关键词:prime/精简 破解 答:请尊重知识产权,如果没有购买的话,建议使用精简版。【问题27】安装器件库时,显示无法安装,如下图 关键词:You didn't select any components to install  答:1. 可能是该器件库已经安装,所以无须再次安装。您可以打开工程来确认。 【问题28】填写管脚时,提示只读,如下图。

关键词:this is a read-only item  答:管脚是在Loaction那一列填写,不是在Filter Location! 【问题29】在GVIM里面写的中文注释,用Quatrus打开之后,出现乱码的情况,如何解决? 关键词:Quatrus中文乱码

答:乱码是由于编码格式不匹配造成的,解决方法如下: 2、Quartus设置默认编辑器为GVIM的方法: http://old.mdy-edu.com/wentijieda/20210409/1197.html?1617938500 【问题30】Quartus如何导入器件库? 关键词:导入器件库

答:首先以管理员身份运行Quartus,然后再Tools中点击Install Devices,然后按照提示步骤导入需要安装的器件库即可。 (器件库文件.qdz不要求放在特定哪个文件夹下,直接导入接可以,器件库的下载的话直接在官网下载) 【问题31】QUARTUS无法配置管脚,或者是没有找到此管脚。 关键词:找不到管脚 答:建议检查芯片型号选择是否正确。如果您使用的是MDY MP801开发板,FPGA芯片型号是:EP4CE15F23C8。 如果您使用的是MDY MP603(点拨)开发板,FPGA芯片型号是:EP4CE6E22C8。 【问题32】Quartus中出现警告:15610 No output dependent on input pin "a" 关键词:15610 No output dependent on 答:指程序中没有任何变量的值根据输入引脚“a”而变化,也就是说这个输入引脚可有可无【问题33】下载MDY的工程后,运行QUARTUS就卡死。 关键词:MDY工程卡死

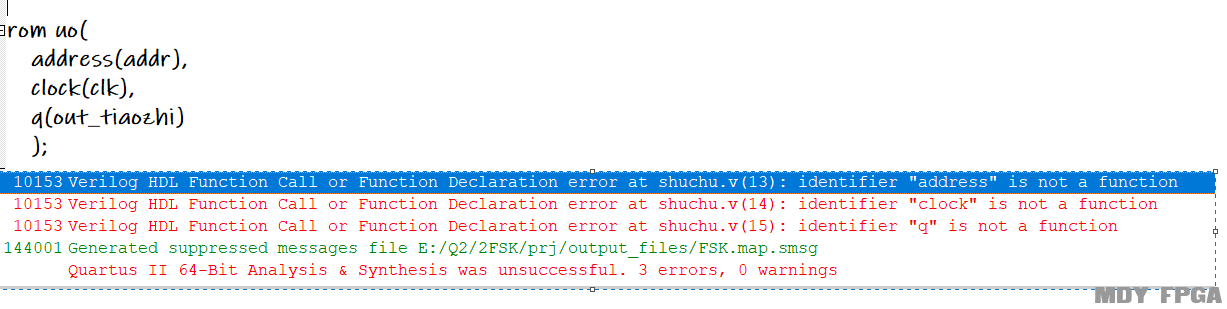

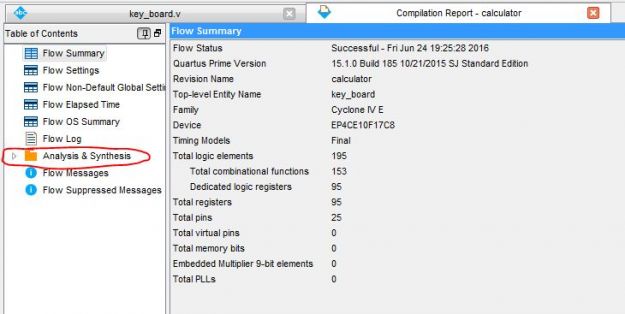

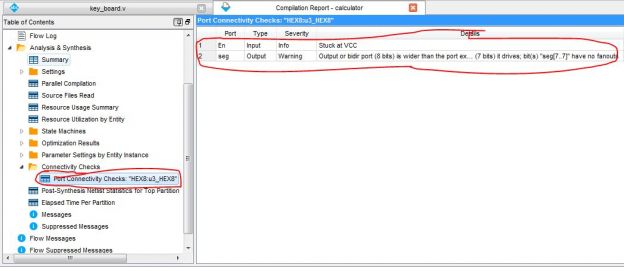

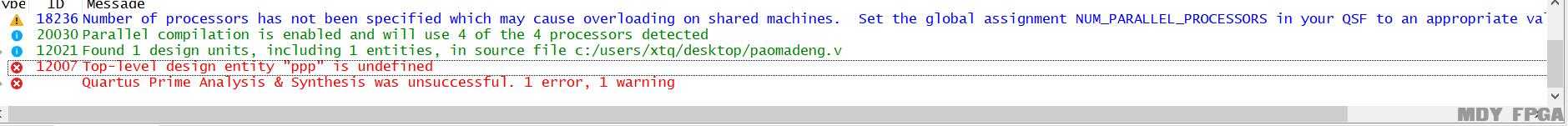

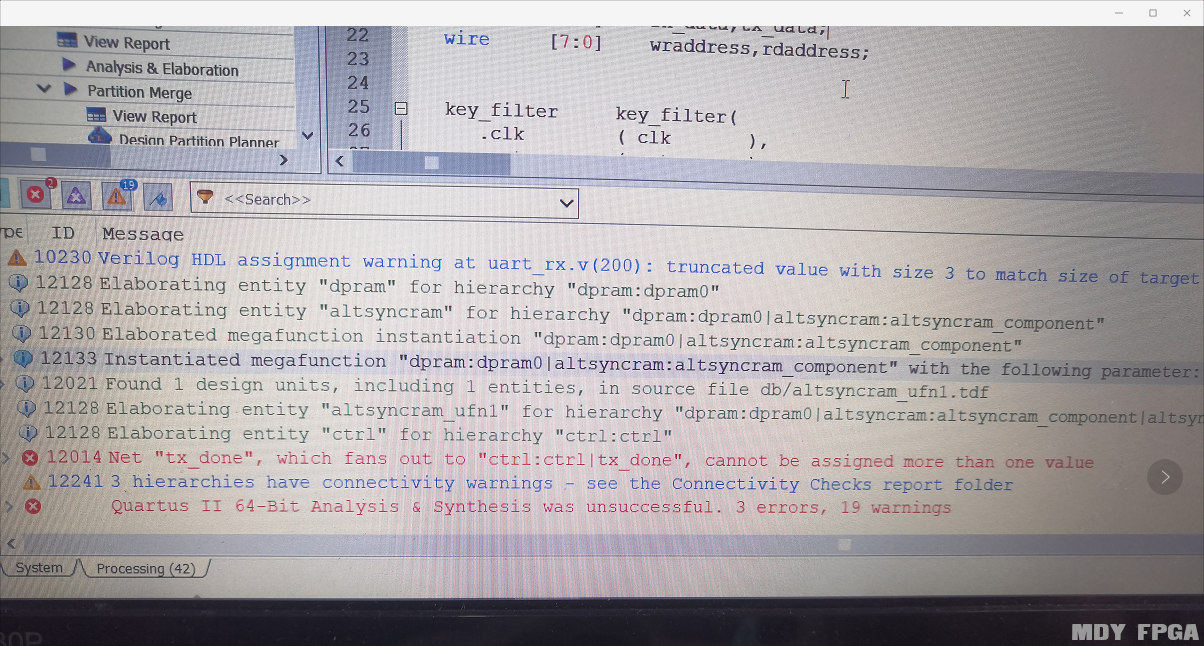

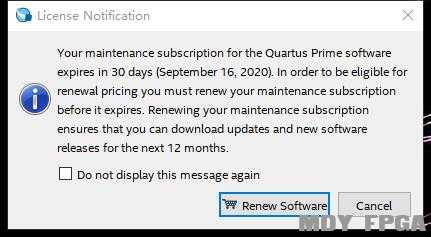

答: 2. 如果试用了方法1后仍然有问题,试综合其他工程,以便区分是软件问题还是工程问题。 a. 如果所有工程都这样,说明是软件问题,请重新安装QUARTUS,建议安装MDY推荐的版本。b. 如果其他工程没问题,说明此工程有问题,建议对比两个工程的异同。 【问题34】QUARTUS提示如下错误:Error (10207): Verilog HDL error at shuchu.v(10): can't resolve reference to object "address" 关键词:can't resolve reference to object  答:例化出错,模块的信号前面需要加 “.”号。更详细请参考例化的代码。另外,出错了,就找个OK的例子,逐个核对。 【问题35】在分析综合时出现警告Warning: 1 hierarchies have connecti vity warnings - see the Connectivity Checks report folder 关键词:Warning: 1 hierarchies have connecti vity warnings - see the Connectivity Checks report folder 答:出现这个警告,并且无法定位,可尝试以下方法:  然后就可以看到具体错误的地方了。 【问题36】出现Top-level design entity“ppp”is undefined错误提示,如下图 关键词:Top-level design entity , is undefined  答:这个是表示本工程的“顶层文件”“ppp”没有找到。请确认您的模块中,包含有"ppp"名称的模块。 (注意,此处的ppp是指模块名,非文件名。有时会粗心,模块名写错,导致模块名和文件名不一致的) 【问题37】(12014)Error: cannot be assigned more than one value 关键词:Error: cannot be assigned more than one value  答:输入的某些引脚同时给了两个值 【问题38】Quartus18.1版本在安装过之后,使用了一段时间后突然提示License Notification,这个怎么解决? 关键词:界面标题是:License Notification

答:把“Do not display this message again”选项勾选上,然后点击Cancel就可以了,不影响使用。

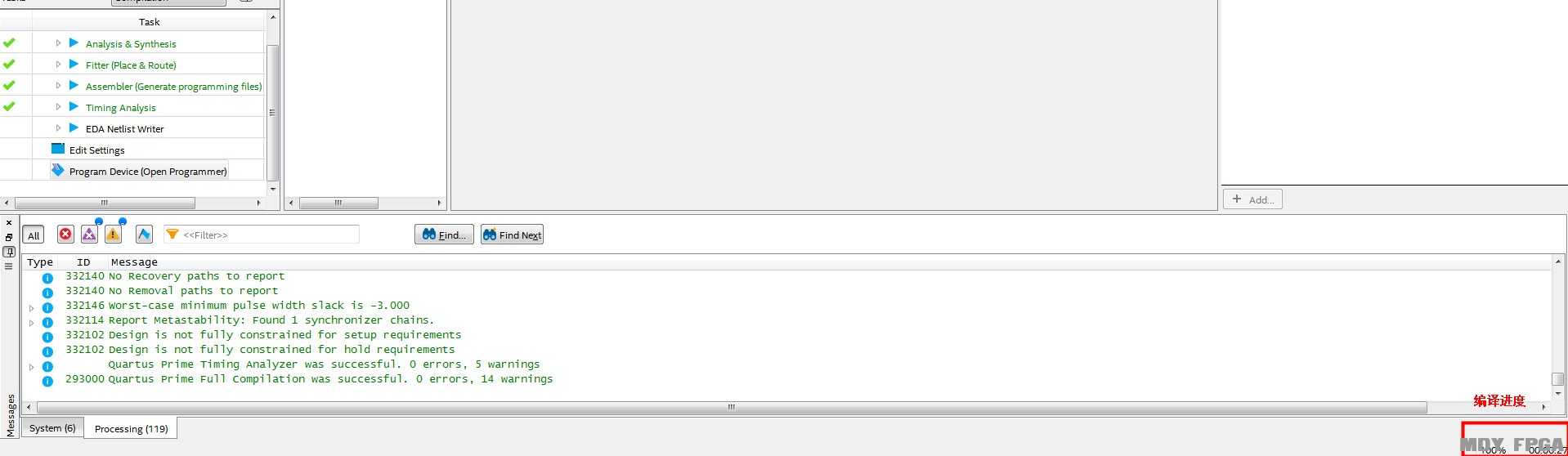

【问题39】一是我按了按键后显示如下,没有提示 程序成功的界面? 关键词:没有找到Quartus某个界面  答:编译进度100%,并且没有报错,则成功。

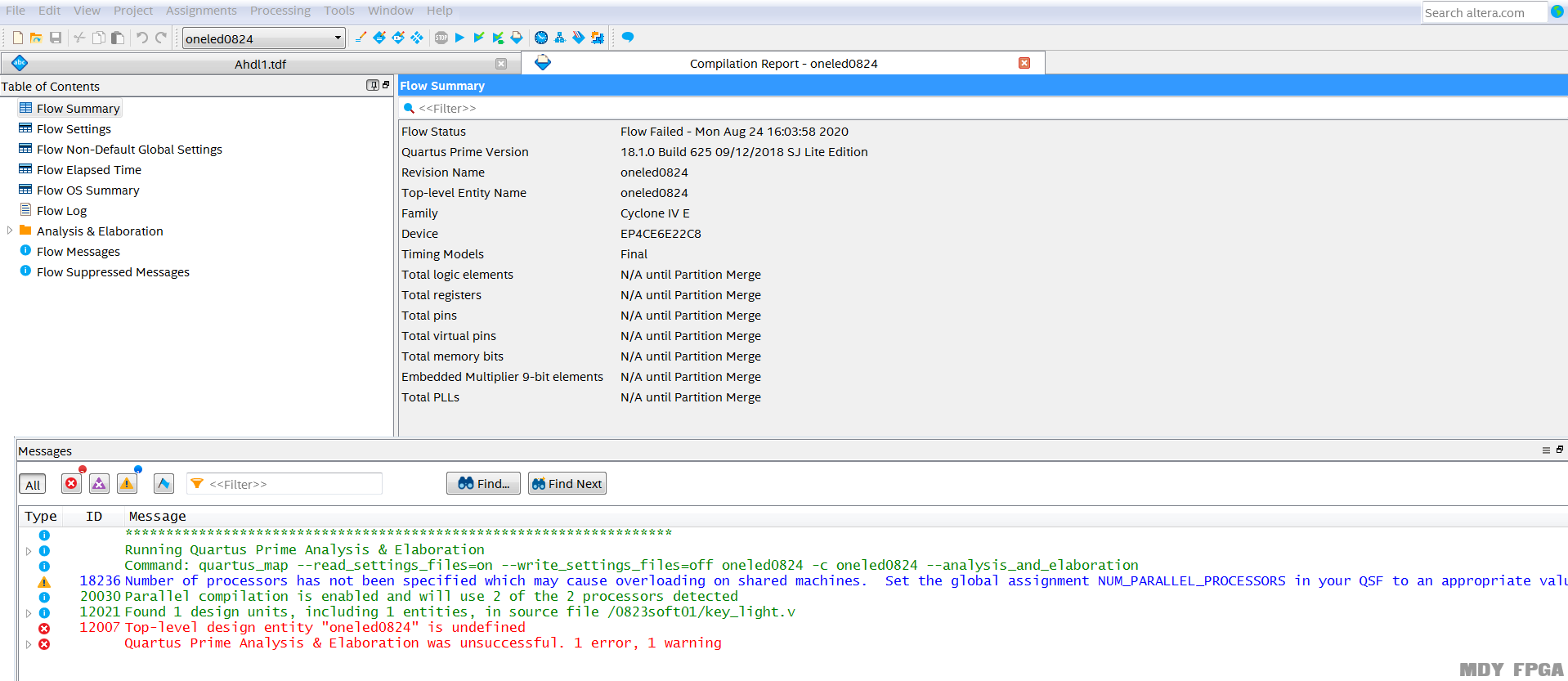

关键词:引脚的配置方法  答:引脚不能乱配,要根据原理图来,选择相应的引脚并且该引脚空闲, 可参考:通过原理图找管脚号的方法:http://www.mdy-edu.com/wentijieda/20210409/1201.html?1617938890 【问题41】quartus Error (12007): Top-level design entity "XXX" is undefined 关键词:Top-level design entity  答:问题造成的原因很简单——verilog文件(.v)里的模块名和顶层实体名(一般就是.v文件的文件名)不一致。

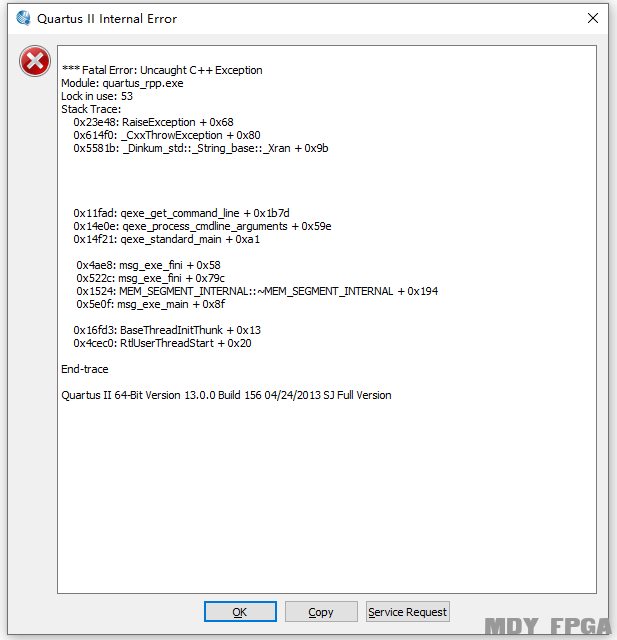

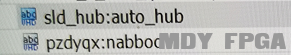

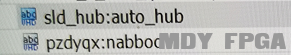

【问题42】Quartus在编译,或者其他操作的时候出现这个错误:Fatal Error:uncaught C++ exception这样的错误,如何解决? 关键词:Error:uncaught C++ exception  答:重新打开Quartus,然后Tools → options → Internet connectivity → check the Altera web site for new Quartus Ⅱ information,取消勾选 【问题43】 QUARTUS提示出下错误: Error (169282): There are 87 IO output pads in the design, but only 85 IO output pad locations available on the device. 关键词:Error (169282) 答:该提示所表达的意思是:您选用的FPGA器件有85个可用的IO管脚,但您的工程却有87个。所以管脚数不够用。该问题的解决思路如下:1. 如果您一定要使用87个管脚,那么只能换更多管脚的FPGA芯片,或其他开发板。 2. 如果您一定要使用本芯片和开发板,那么您就要想办法减少工程的管脚数。 3. 存在一种情况:该工程只是一个模块,您综合只是为了查看一下综合后的结果。那么您可以将这个模块的管脚设置为虚拟管脚, 方法可为: a. 在Quartus II中Assignments->Assignment Editor;b. 在Category栏选择logic options, c. 到列表中To列下添加要设置的引脚接口,如果需要设置的很多,可以通过在 Pin Planner中将引脚复制过来。 d. 将Assignment Name设置为Virtual Pin, e. 将Value设置为On, f. Enabled 设置为Yes。 【问题44】QUARTUS中会出现下面两个模块,是什么来的? 关键词:如图中,出现两个名字相同的模块,图中是pzdyqx,也可能是其它名字   答:这两个模块不是代码产生的,而是软件产生的,估计是有特定用途,我们可以不用关心。 【问题45】Error (209014): CONF_DONE pin failed to go high in device 1 关键词:Error (209014): CONF_DONE pin failed to go high in device 1 答:当尝试使用.sof文件通过JTAG配置器件并且已经错误的在Quartus® II工程中设置了器件时, 可能会收到"Error (209014): CONF_DONE pin failed to go high in device 1"错误。 例如,如果具有Quartus II工程,那么对Engineering Sample (ES)器件进行设置并且编译设计以及使用生成的.sof文件 来编程包含产品器件的电路板。 反过来也适用,其中电路板包含ES器件并且设计针对产品器件。

解决:确保Quartus II工程中选择的器件匹配电路板或Altera®开发板上的器

【问题46】请问下面提示如何解决了? 关键词:Top View Wire Bond,With Exposed Pad

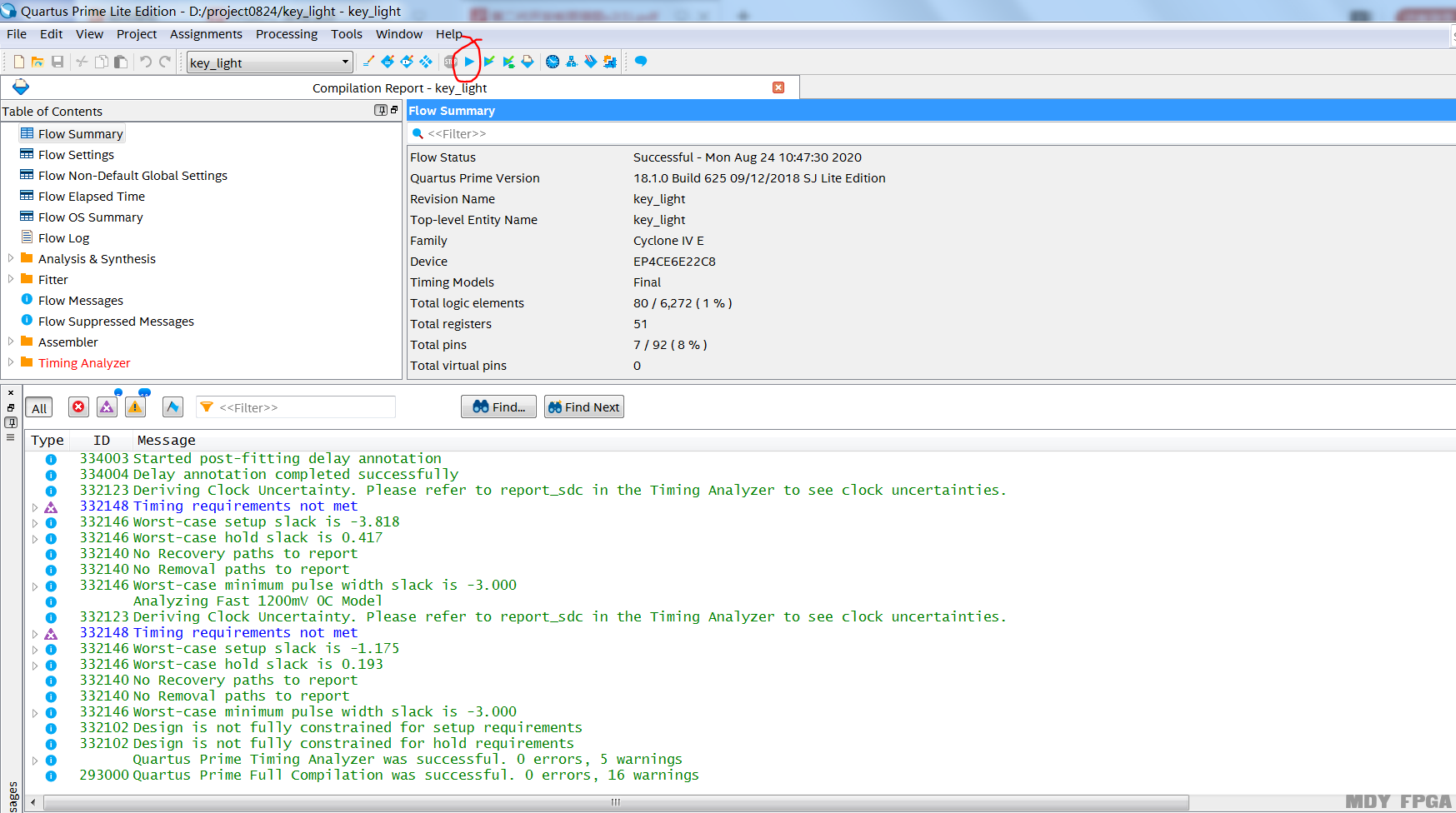

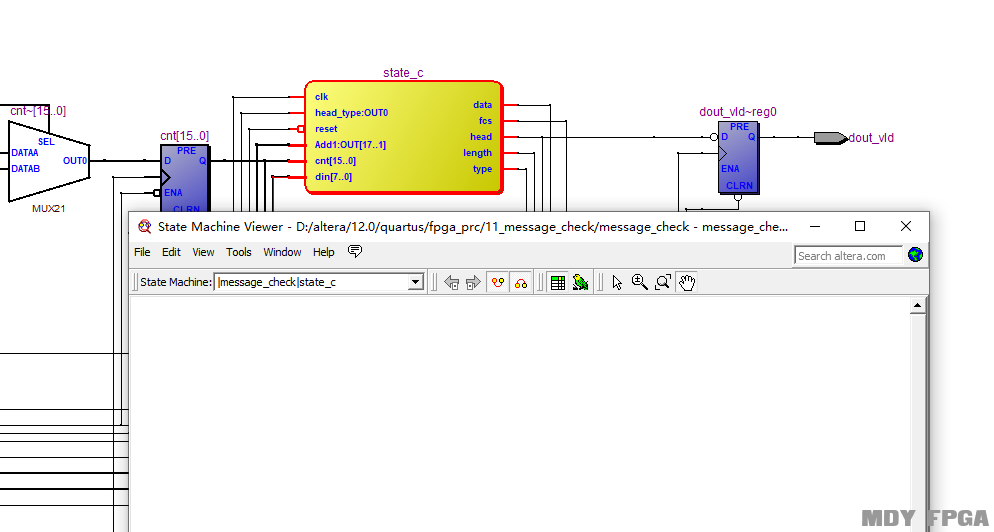

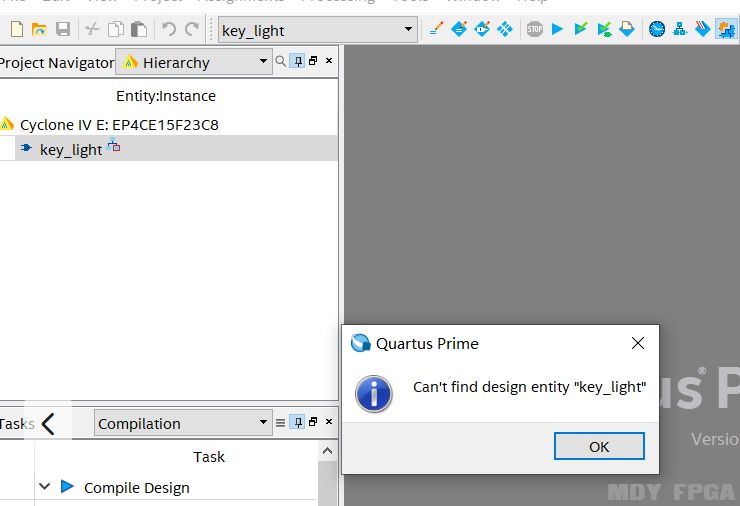

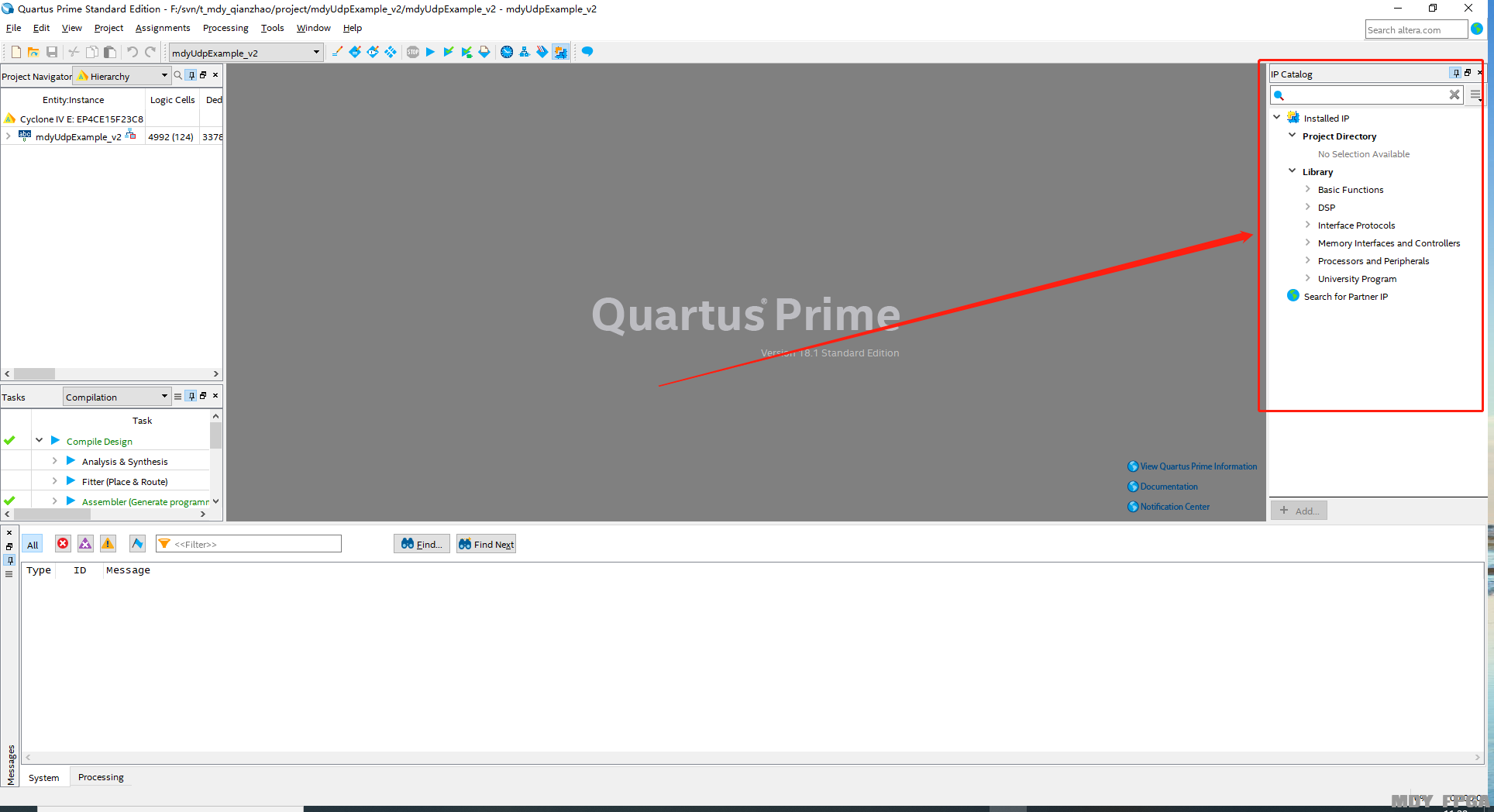

2.可能软件有问题 可以换一个正常工程试试看 【问题47】请问一下quartus状态机视图里面看不到信息是什么情况? 关键词:状态机视图  答: 1. 可能工具使用不当,可以多尝试几次; 2. 可能是写法,让综合器认为这不是一个状态机,可以检查一下自己写法(可以尝试最简单、最标准的写法试一下,再逐步改过来) 【问题48】 编译的时候,提示“Can't find design entity "xxxx"” 关键词:Can't find design entity  答:这个问题是提示,找不到名为“key_light"的模块名。 请确保你的设计有,有一个名为“key_light”的module。 如果确实有这个设计,那可能是没添加到工程里,可以按添加文件方法,将此文件添加进来。 如果你没有这个文件,那么在新建工程里,填写顶层模块名时,不要写“key_light”。如果这个工程不是你新建的,那么可以在quartus的files里,找到你所希望的顶层模块,然后右键,set as top。 【问题49】Error (332148): promoted from Critical Warning: Timing requirements not met 关键词:Timing requirements not met 答:问题原因是时序要求未满足。 综合完了以后,Timequest Timing是红色的,需要做一下时序约束。要是功能没那么复杂,不做约束也行,就别管Timing requirements not met了。 【问题50】打开一个Quartus工程,如何查看哪一个文件是顶层文件? 关键词:查看顶层文件 答:如下图所示,双击顶层模块名,就可以打开顶层文件

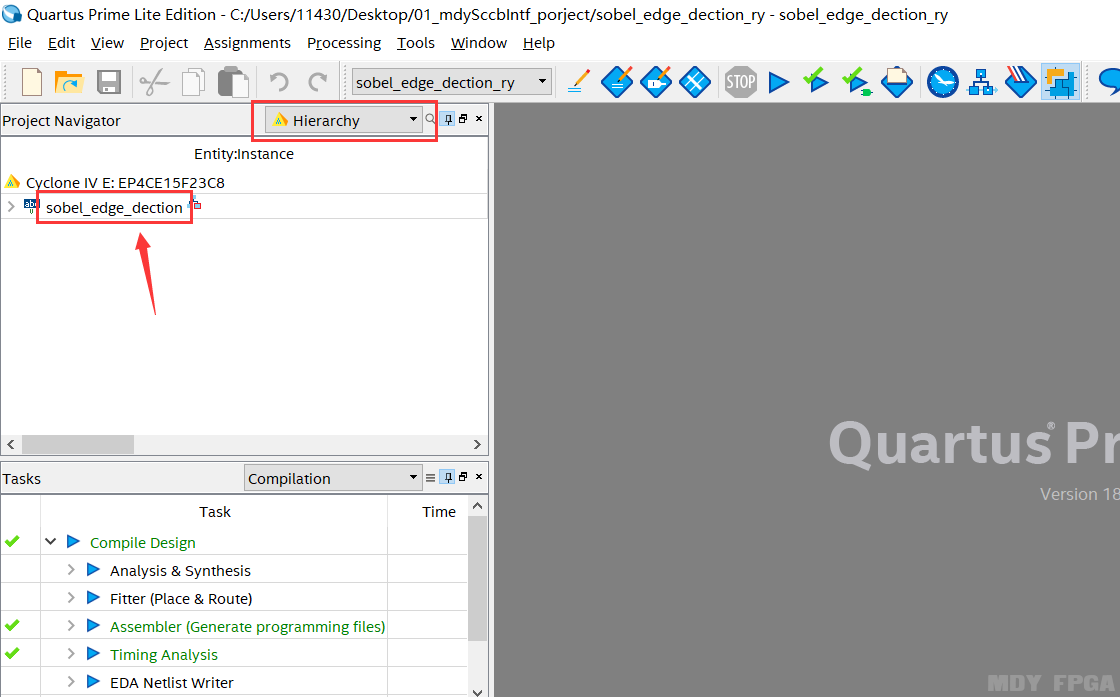

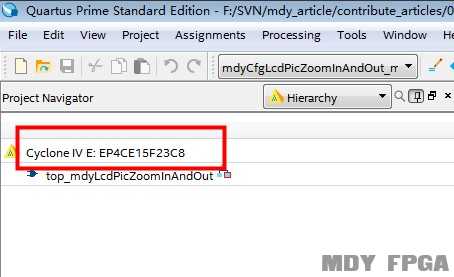

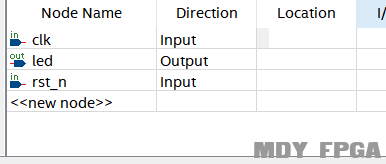

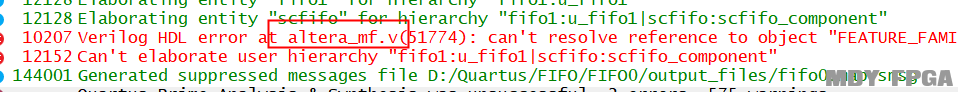

【问题51】老师, 为什么配置脚位的时候,location 和 fitter location 是不一致的呢 ? 关键词:配置管脚位不一致 答:配置完管脚后,重新编译即可。【问题52】为什么设置引脚的时候找不到led[0],led[1],led[2],led[3],只有一个led。 关键词:找不到管脚  答:请检查Led信号的位宽是否正确,led位宽为1bit,就只有一个引脚可配置。 【问题53】在QUARTUS工程中,添加了altera_mf.v文件,提示如下错误。 关键词:altera_mf.v报错  答:altera_mf.v文件,是仿真库文件,是在仿真的时候才使用到的。在QUARTUS工程里,不需要添加此文件。 【问题54】如何查看芯片型号? 关键词:查看芯片型号 答:

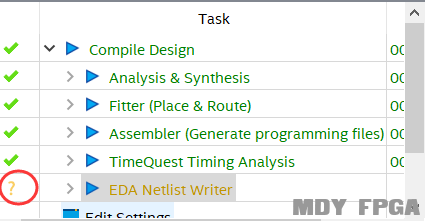

关键词:产生不了输出文件/产生不了SOF文件  答:双击?运行就可以的 。 【问题56】Quartus编译出现如下错误提示:Exception during generation:C:Users~%?…,# *'☆&℃$︿★?..........., 检查过工程没有中文路径,是什么原因? 关键词:Exception during generation:C:Users~%?…,# *'☆&℃$︿★?...........  答:这个电脑当前使用的账户名应该包含的有中文字符,需要更换为全英文的账户。 【问题57】在子模块中定义的参数,需要在顶层模块中例化吗? 关键词:子模块参数 答:不需要的。

【问题58】编译出现Error: Can't elaborate user hierarchy 关键词: Error: Can't elaborate user hierarchy 答:出现这种错误的原因一般是时序逻辑always下面的代码同时判断了多条语句,比如缺少else等,检查代码【问题59】想问一下SPI和JTAG下载的区别 下载方式是根据FPGA芯片来定义的嘛?FPGA都有那些下载方式? 关键词:SPI 和JTAG 答:不是,使用JTAG下载是属于断电会丢失的,使用spi一般是固化到外围芯片上,断电不会丢失,跟FPGA芯片没有关系下载的三种方式: 1、主动配置方式AS:由FPGA器件引导配置操作过程,EPCS系列,如EPCS1,EPCS4配置器件专供AS模式, 目前只支持Cyclone系列,断电不丢失 2、被动配置模式PS:由外部计算机或控制器控制配置过程,通过加强型配置器件(EPC16,EPC8,EPC4) 等配置器件来完成,断电不丢失 3、JTAG配置方式:直接烧到FPGA里面的,最常用的方式,由于是SRAM,断电后丢失。【问题60】QUARTUS18.1版本中,没有找到视频中的“MegaWizard Plug-in Manager..”,无法找到IP核。 关键词:找不到MegaWizard Plug-in Manager 答:见下图。 【问题61】程序下载,断电后,程序又没有了。 关键词:断电程序没有 答:一般下载SOF文件格式的程序,断电之后该程序是会丢失的。如果不想丢失,可以将其固化到FLASH芯片上。下面是教程。MP801固化教程:801开发板烧录步骤(Quartus II)——固化程序 : http://old.mdy-edu.com/wentijieda/20210408/1194.html?1617939012 MP603固化教程:点拨开发板烧录固化步骤 :http://www.mdy-edu.com/wentijieda/20210408/1193.html?1617939096

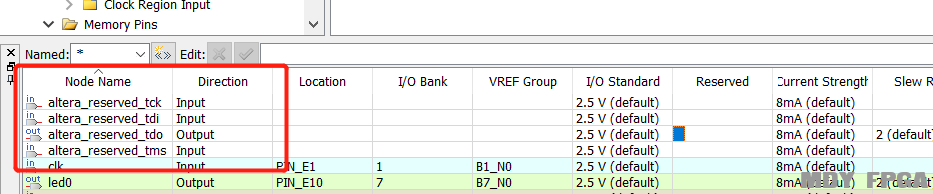

关键词:配置管脚信号名是altera_开头

答:FPGA系统自带的管脚,有专门用途,不用关心。

【问题63】QUARUTS固化程序/烧录程序出错的原因,如下提示。 关键词:烧录方法

答:上图中,其勾选的范围不正确,请仔细对比下面教程,注意要完全一致。 MP801固化教程:801开发板烧录步骤(Quartus II)——固化程序: http://old.mdy-edu.com/wentijieda/20210408/1194.html?1617939012 MP603固化教程:点拨开发板烧录固化步骤 http://www.mdy-edu.com/wentijieda/20210408/1193.html?1617939096

【问题64】下载的QUARTUS安装文件中,qdz格式文件是干什么的? 关键词:安装文件qdz

答:qdz是器件库文档,里面包含了一些FPGA芯片的信息,例如要用到EP4CE15F23C8,这个FPGA型号的芯片有多少管脚、有多少资源,都会包含在这个器件库里。

【问题65】 调用某个IP核时,在哪可以查看这个IP核生成信号的端口时序? 关键词:IP核端口时序 答:IP核的接口时序,通常要看IP核的数据手册。IP核的数据手册,通常在IP核的生成界面里可以下载到,一般都有document的选项的,请注意查看。

关键词:恢复默认窗口

答:请点击软件左上角,VIEW-Utility windows, 或者使用快捷键盘 Alt+数字(1-7)即可。

关键词:SIGNALTAP窗口,no device is selected

答: 2.如果问题依旧,是硬件没有连接好或者连接错误,请看此贴问题3,排除原因。

3.以上两个操作没有解决,请联系服务老师

关键词:The pin**has multiple drivers due to hen non_tir-state driver |

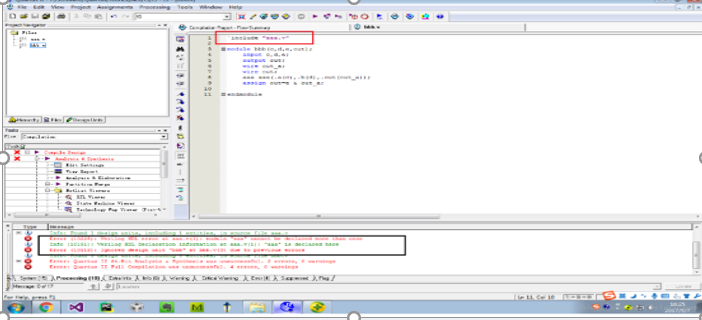

【问题69】请问Quartus II中`include的使用出错,如图:

关键词:include出错

答: 在Quartus

II中同一工程目录下,使用`include

“xxx.v”会产生重定义的错误,去掉

`include “aaa.v”

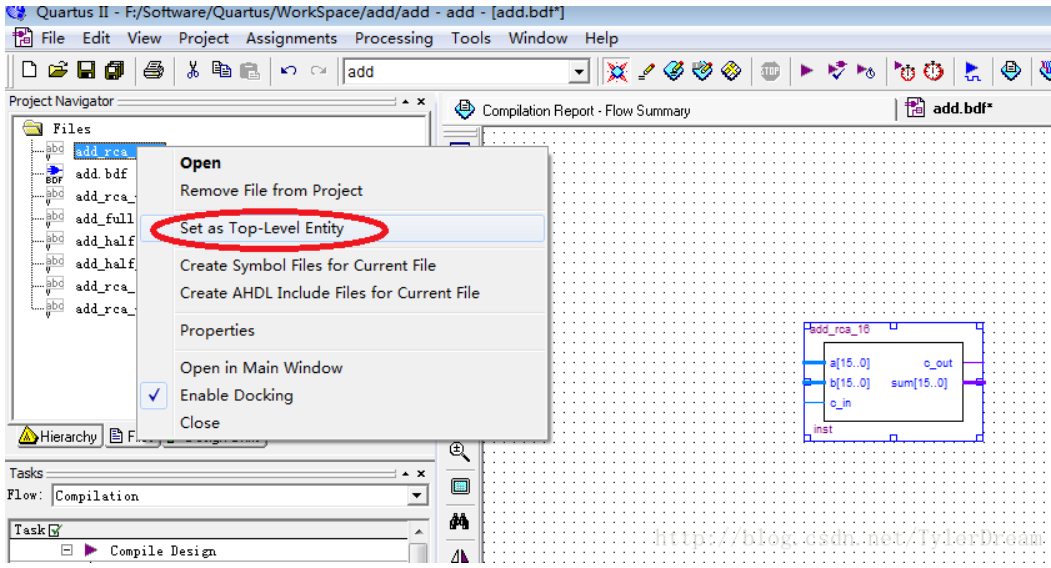

【问题70】请问如果设计16位加法器遇到的问题:Error: Can’t synthesize current design – Top partition does not contain any

logic怎么解决?

关键词:Error: Can’t synthesize current design – Top partition does not contain any logic

问题分析:

1.在程序中使用电路图为顶层文件,但是没有接上管脚,所以弹出以上错误

2.如果使用verilog文件作为顶层文件,一般不会出现这种问题

答:

解决方法1. 接上管脚:右键原理图 ->Generate Pins from Symbol Ports(如下图所示)

解决方法2. 设置add_rca_16.v为top level:

【问题71】请问quartus为什么会显示这个窗口?

关键词:显示窗口

答:在quartus菜单、VIEW选项,可以设置显示出上面窗口。VIEW的所有选项都可以尝试一下

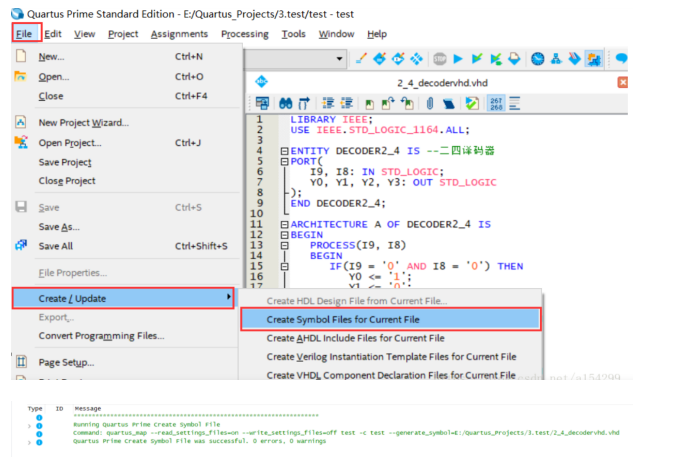

【问题72】如果你想让vhdl文件生成为部件,并用它进行画图,那么请问怎么进行?操作如下:

关键词:vhdl文件

答:点击 File->Create/Update->Create symbol files for current file,没有报错即可,这样一个部件就生成了。

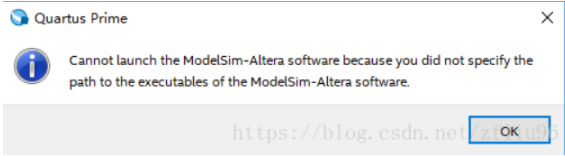

【问题73】quartus初次安装使用使用modelsim软件进行仿真时无法自动打开软件怎么办?

关键词:打开modelsim

答:这是因为modelsim软件的路径没设置。

1.点击Tool->Option

2.在option界面点击General -> EDA Tool Option设置Modelsim-Altera的路径:quartus的安装路径 modelsim_asewin32aloem

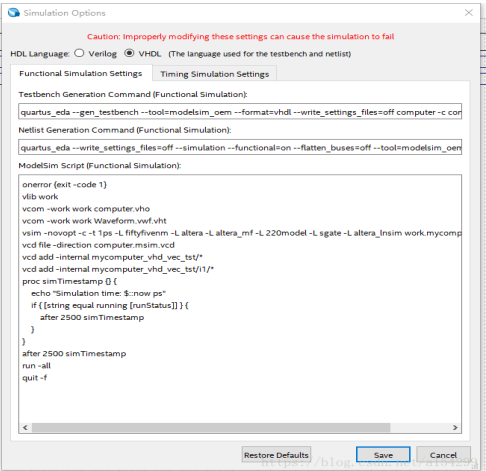

【问题74】请问建立的vwf文件,点击Simulation->Simulation Settings,会出现如下界面:

关键词:提示Caution:improperly modifying there can cause the simulation to fall

答:对Functional Simulation Settings选项卡中的内容做如下修改(注意Quartus软件中的路径分割符方向与Windows下的路径分隔符方向相反,一个是"/",一个是"")

(1)将Testbench Generation Command(Functional simulation)栏中的 "--vector_source"后的路径改成你自己的vwf文件所在路径(注意文件名也要修改成你自己文件的名称),"-- testbench_file"后的路径改成步骤3中所复制的.vht后缀文件所在的路径(注意文件名也要修改成你自己文件的名称),

(2)把Netlist Generation Command(Functional Simulation)栏中的"--output_directory"后的路径改成"工程文件夹/simulation/qsim"。

(3)将Modelsim Script(Functional simulation)栏中的vcom -work work Waveform.vwf.vht 文件名修改为你自己的文件名。

(4)如果你要进行时序仿真,则修改Timing Simulation Settings选项卡中的内容。

【问题75】我想问一下调试课中这个案例为什么会ip 报错 没办法编译?提示没有找到my_fifo这个ip

答:该工程是串口调试工程。该工程中可同时支持XILINX和ALTERA版本。如果您使用的是XILINX,在data_handle.v文件最前面加上一句:`define XILINX 1 如果您使用的是ALTERA,则记得在handle_prj.v文件中删除上面说的那一句。