Lattice MIPI D-phy 硬件设计

MIPI联盟是一家合作的全球性组织,为开发移动和受移动设备影响的行业提供服务。该组织的重点是设计和推广硬件和软件接口,以简化从天线和调制解调器到外围设备和应用处理器的设备内置组件的集成。MIPI Alliance精心设计其所有规格,以满足移动设备所需的严格操作条件:高带宽性能,低功耗和低电磁干扰(EMI)。 所有领先的芯片组供应商都使用了MIPI Alliance规范,这些规范已帮助移动行业的公司整合了集成方法,同时创建了自己的高级设计来使产品与众不同。当今市场上的每个智能手机都至少具有一个MIPI Alliance规范。

Lattice Xilinx 等FPGA芯片原厂都是其联盟成员,MIPI联盟发布了很多接口规范标准,其中MIPI CSI-2,MIPI DSI,是目前广泛应用的接口标准,主要应用在移动端,例如移动电话,平板电脑等,近些年也广泛应该于汽车领域,工业领域,主要还是ADAS ,机器学习的兴起。

MIPI CSI-2 (MIPI Camera Serial Interface 2),移动和其他市场中使用最广泛的摄像机接口。它以其易用性和支持广泛的高性能应用程序(包括1080p,4K,8K以及更高的视频和高分辨率摄影)而得到广泛采用。其由协议层,应用层,物理层构成。物理层使用的是D-phy (主要还是D-phy)跟C-phy。

MIPI DSI(MIPI Display Serial Interface)定义了主机处理器和显示模块之间的高速串行接口。该接口使制造商能够集成显示器以实现高性能,低功耗和低电磁干扰(EMI),同时减少引脚数并保持不同供应商之间的兼容性。设计人员可以使用MIPI DSI为最苛刻的图像和视频场景提供出色的色彩渲染,并支持立体内容的传输。其物理层也是采用的D-phy

D-phy 是MIPI联盟的物理层小组所发布的物理层标准,该小组还发布其他物理层标准, A-phy , C-phy , M-phy。

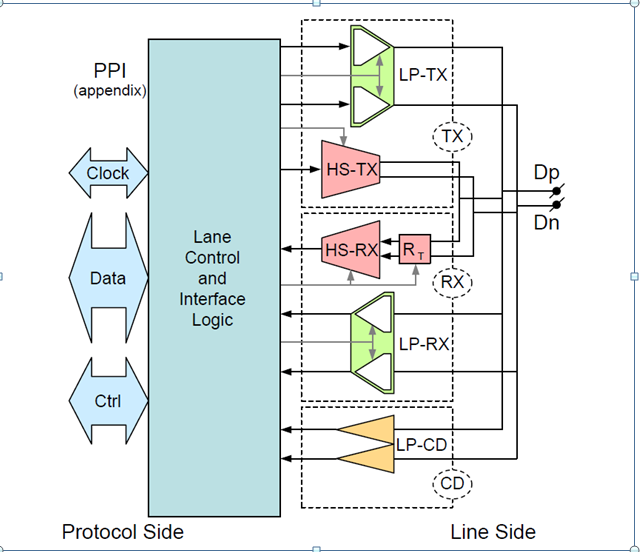

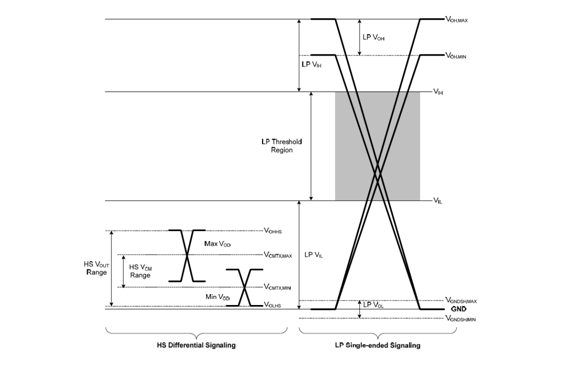

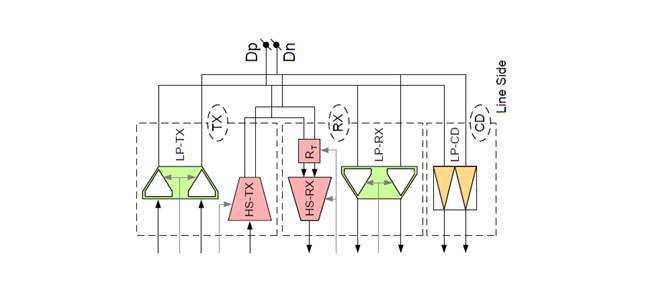

D-phy V1.0 标准指出,其使用了两种传输数据的模式,高速模式(High Speed,HS)和低功耗模式(Low Power,LP),两种模式使用不同的传输电平和传输机制。D-phy每个数据通道使用两条线(HS跟LP在每个通道下是共用的传输线),时钟通道使用两条线。这说明了用于最低配置的时候需要四根线。 在高速模式下,每个通道在两侧均终止,并由低摆幅差分信号(SLVS)驱动。 在低功耗模式下,所有电线均采用单端和非终端方式操作。

在HS模式下其速率可达到500Mbps,DDR(dual-edged data transmission)模式。通过采用突发模式通信,可以降低有效数据吞吐量。 低功耗模式下的最大数据速率为10Mbps。

D-PHY电气子层指出高速信号(HS)采用的差分电平传输的摆幅较低,一般为200 mV,而低功耗信号(LP)单端电平传输的摆幅较大,一般为1.2V。

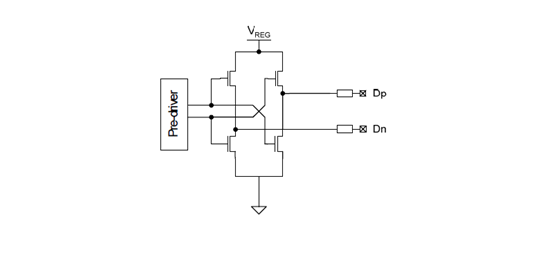

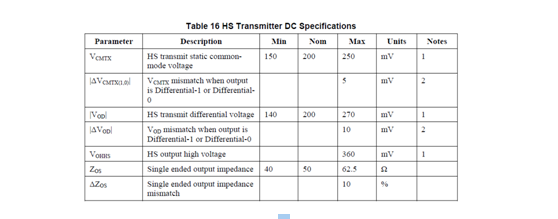

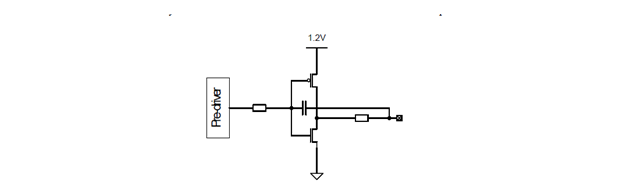

HS的发送端的电路结构如图,是由两个CMOS组成的差分输出电路,由其DC参数可以得到,其差分压摆幅度是140~270mV,一般值为200mV,单端输出阻抗为40~62.5 ohm,这个参数可以帮助我们设计接收端电路板时做好阻抗控制与匹配,以保证信号完整型。Lattice FPGA内部并没有这样的IO buffer,所以只能通过使用其他的IO buffer 做电平转换,以满足这样的要求。

LP的发送端电路图,其为LVCOMS12结构输出,Lattice FPGA 拥有LVCOMS12 IO buffer,加上外部端接电阻,可以满足输出阻抗110 Ohm的要求。

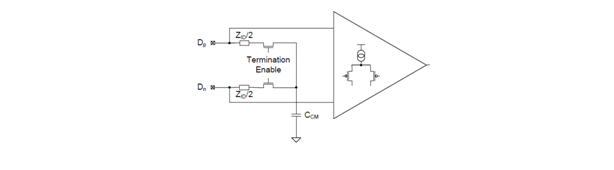

HS与LP的接收端与普通的LVDS,CMOS接收端并无多大区别。由于Lattice 可以接收200mV的SLVS,只要选择固定的IO bank就行,值得一提的是Lattice 器件的tureLVDS 管脚有限,使用LVDS25E需要外接端接电阻,端接电阻Zid一般为100 ohm,与LVDS外部端接保持一致。当然,LVDS 跟LVDS25E所能接收的速率是不一样的,这一点需要注意。

Lattice MIPI csi-2与 DSI 除了使用crosslink器件解决方案,其他器件都需要自己添加与设计D-phy的电气子层,因为crosslink器件更像一个可编程的ASIC,普通的FPGA是没有下图这样的物理资源。

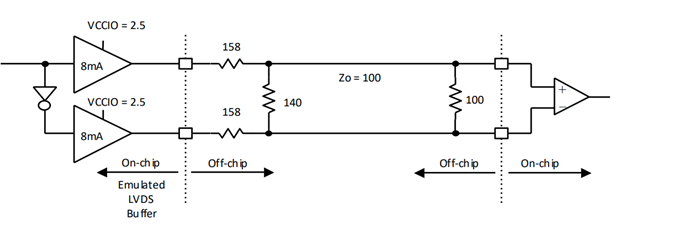

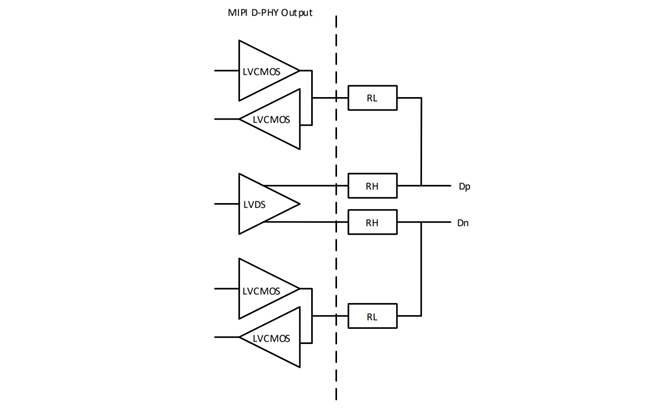

MIPI D-phy 发送端的设计需要使用到LVDS25E的资源,LVDS25E是通过 Lattice 的8mA CMOS输出buffer,构成的桥式电路。通过外部电阻构成的分流网络,可以模拟出LVDS 的输出。

改变这个电阻网络,可以模拟出D-phy HS 输出电平与LP电平,LP电平使用的 IO buffer 为LVCMOS12。Lattice官方给好的数据是RH=330 ohm ,RL =50 ohm,当然该bank的电源要使用2.5V,若使用3.3V,则需要根据速率与信号完整性自己进行设计。

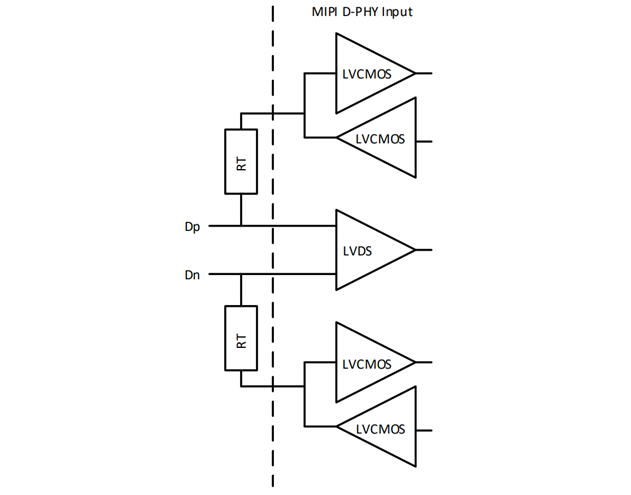

对于接收端,由于Lattice 的LVDS IO buffer 支持SLVS 电平,只需要在LP接收端使用LVCMOS12 的 IO buffer,且外部添加RT=50 ohm的端接电阻即可。当LVDS IO资源不够时,可以采用LVDS25E,这将需要外端接100 ohm电阻,并且MIPI CSI-2跟MIPI DSI 的工程综合后,布局布线会报错,这时则需要自己优化好FPGA内部布局布线等。

目前明德扬公司已经使用Lattice MachXO3系列与ECP5系列完成了4路sensor 通过MIPI csi-2 输入,拼接成一路MIPI CSI-2输出的工程,该工程也应用于无人机,工业机器视觉等开发。想要合作的朋友可以联系明德扬!

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 前端模拟采集、射频、电荷灵敏前置放大器

明德扬科技教育

明德扬科技教育