Diamond FIFO生成和例化教程

本文为明德扬原创文章,转载请注明出处!作者:鱼丸粗面

在MIPI多路摄像头拼接项目中,需要使用到FIFO的IP核来进行数据的缓存与时钟域的交互,下面我来介绍一下Diamond FIFO IP核生成与例化的步骤。

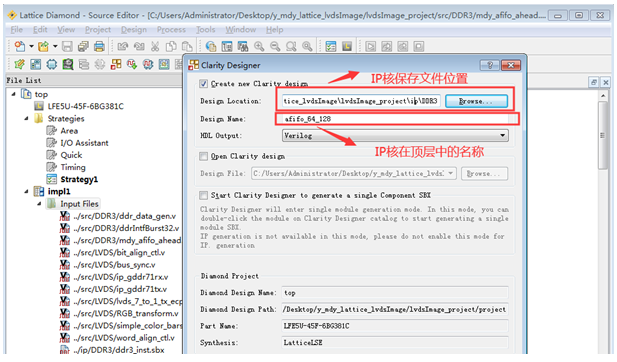

首先,找到生成IP核的窗口,如下图1中红框标注所示:

点击后进入Clarity Designer,创建一个IP核。需要注意的是Design Name中输入的名称即是在顶层文件中需要例化的IP核模块名。

图2 Clarity Designer

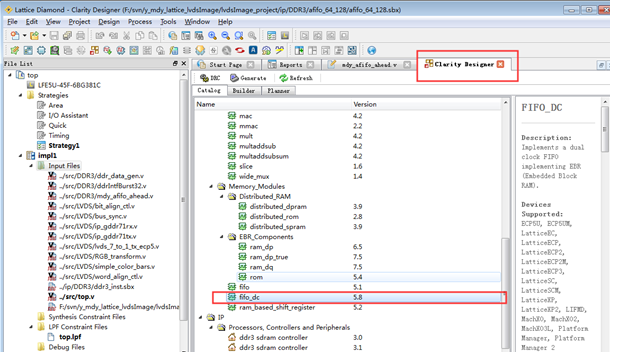

点击下方的“create”进行创建,找到双端口“FIFO(fifo_dc)”:

图3 Diamond IP核列表

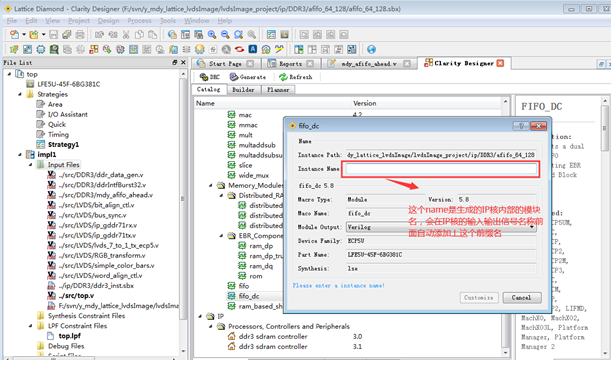

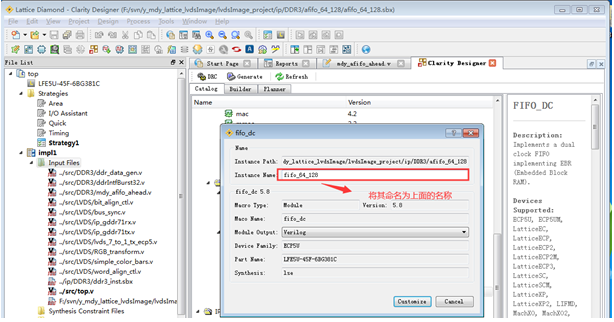

设置fifo的实体化保存路径及实体化名称。需要注意的是,“Instance Name“中输入的名称不是FIFO在顶层模块中例化的模块名,而是生成fifo后IP核内部的信号名前缀。

图4 生成FIFO IP核文件设置

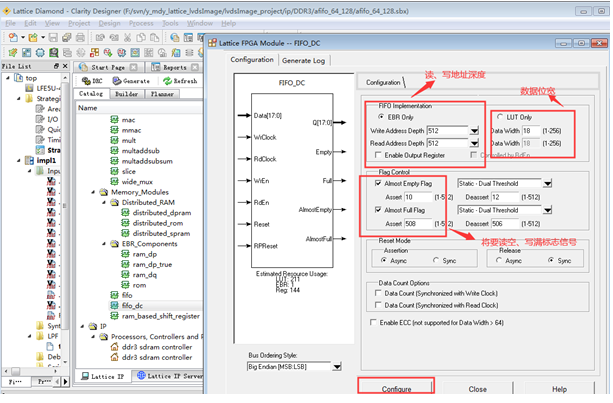

点击“customize“,进入FIFO IP核设置界面,设置FIFO的深度、数据位宽以及标志信号,设置好后点击”Configure”:

图5 FIFO IP核设置界面

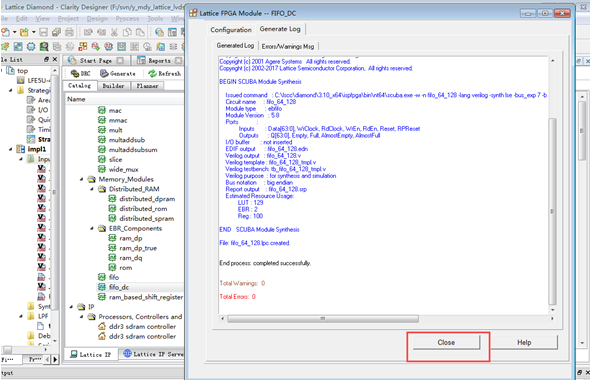

IP核生成成功,点击“Close“关闭窗口:

图6 IP核生成成功

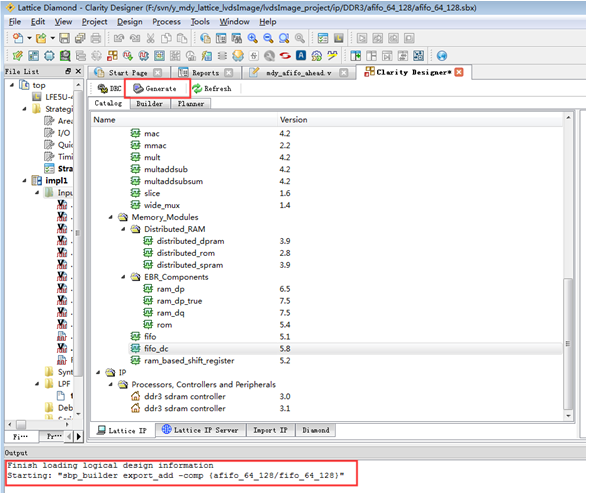

点击“Generate”,将生成的IP核添加进工程中:

图7 IP核添加进工程

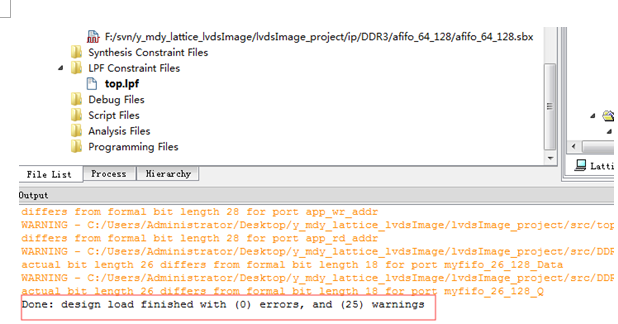

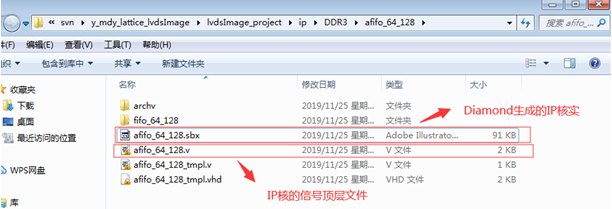

FIFO IP核生成的文件夹及生成的IP核信息,其中“.sbx”文件是IP核的实体,需要添加进工程中去,“.v”文件中包含IP核的顶层信号。

图8 IP核文件

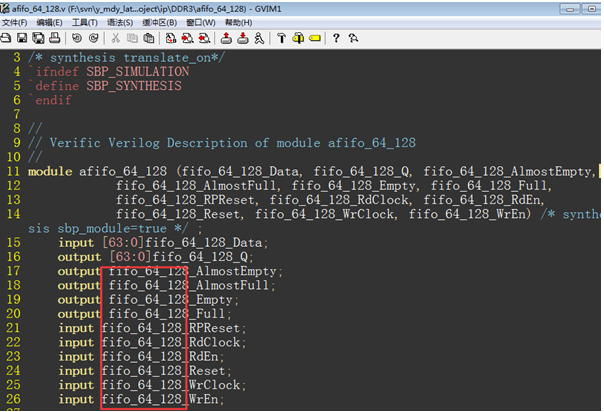

打开生成的IP核V文件,可以看到IP核内部的信号名前缀加上了设置的名称前缀。

图9 IP核V文件内部信号

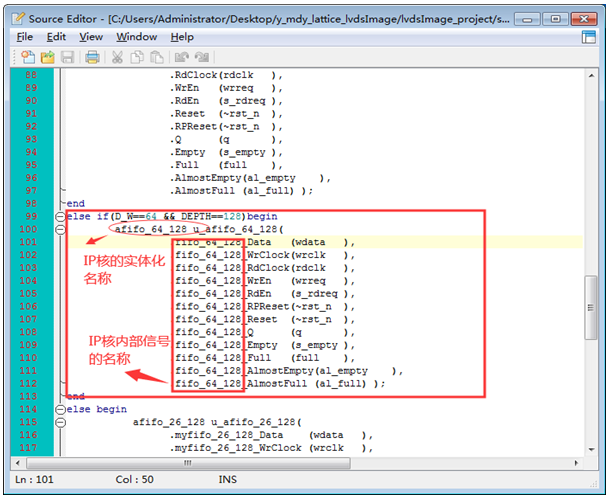

在顶层中将V文件中的信号进行例化:

图10 顶层例化IP核

例化进顶层中后,FIFO IP核即可用于工程接下来的设计。如有不明白的地方可以加我的QQ:3358622769,我将会具体的向有需要的同学进行指导。期待与大家一起探讨进步!