|

阻塞与非阻塞

作者:小黑同学

【总结1】规范用法:时序逻辑使用非阻塞赋值,组合逻辑使用阻塞赋值。

【总结2】按照规范用法,不会产生任何问题。

【总结3】非规范用法,纯粹是为了学术探讨的目的,而不是应用目的。 为学术探讨,可以看下面的内容。

关于阻塞赋值和非阻塞赋值的讨论

1. FPGA里只要总结出一个规范用法:时序逻辑使用非阻塞赋值,组合逻辑使用阻塞赋值,就不会产生任何问题,即使你不懂阻塞和非阻塞的区别都可以。 2. 有关于阻塞赋值和非阻塞赋值,纯粹是国内的学者,无聊、咬文嚼字、卖弄语法才整出来的问题,更多地去解析语法,玩不同语法情况下的理解。 3. 经常会问到:不按“规范用法”去做,会产生什么样现象的问题!这种问题实在是太多太多,各种角度提问的方式都有,防不胜防。为此,特提供一个思路,请按这个思路来去理解。 a. 首先一定要理解,VERILOG是硬件描述语言这个大前提!请深刻理解!VERILOG就是用来描述功能,然后综合器按照功能描述,去产生一个电路,来跟这个功能对应! b. 阻塞赋值是一行一行“执行”,非阻塞赋值是“同时执行”。这是第二前提。请仔细思考在这前提下,这个功能会如何变,必要时结合CLK一起理解!!!(如果实在理解不了,那就用MODELSIM仿真,仿真结果就是功能) c. 综合器根据“描述的功能”来生成电路,这是第三前提。综合器生成的电路,一定是与“功能描述一样”,即使这个电路看起来跟设想的完全不一样。

d. 请按上面三步,逐个确认。参考的视频:https://www.bilibili.com/video/BV1yf4y1R7gH?p=26

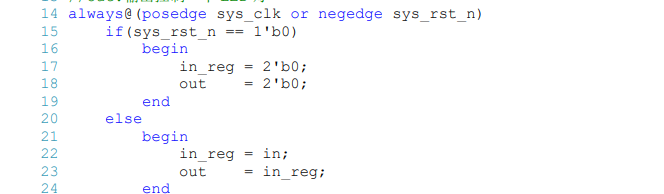

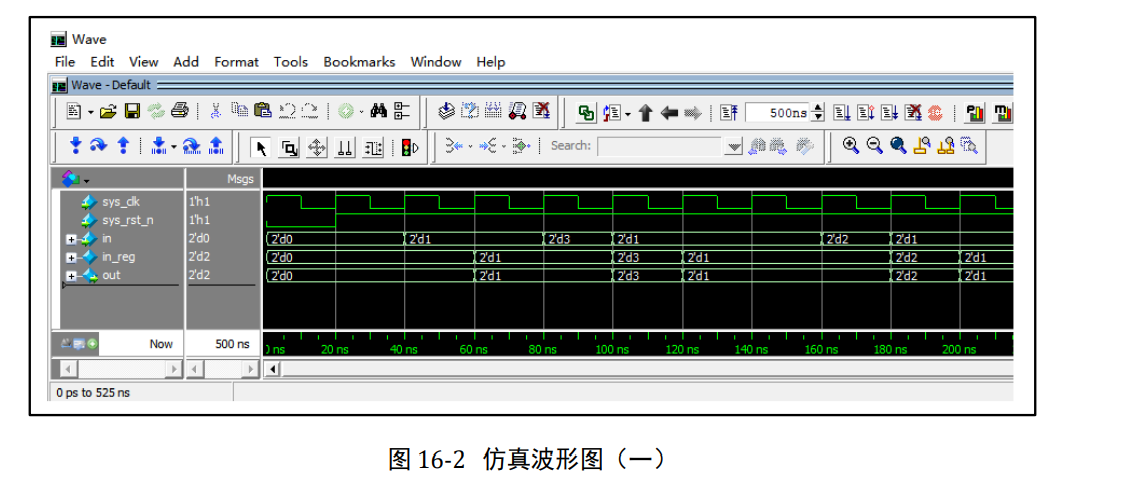

【问题1】为什么使用“阻塞赋值”,in_reg和out的值是一样的?

答:理解“阻塞”这含义,阻塞是一行一行先后执行。所以在时钟上升沿来的时候,先有in给了in_reg,再有in_reg给了out。所以在时钟上升沿的时候,in为1的话,那就是先in给了in_reg,此时in_reg等于1;然后再in_reg给了out,此时out也为1。所以最终的结果,就是一个时钟上升沿后,in_reg和out都为1,即两个值相同。 |