本文为明德扬原创文章,转载请注明出处!

今天分享基于Altera的光纤口通讯工程的IP核配置,本工程实现了四个速率都是3.125Gbps的光纤口通讯。

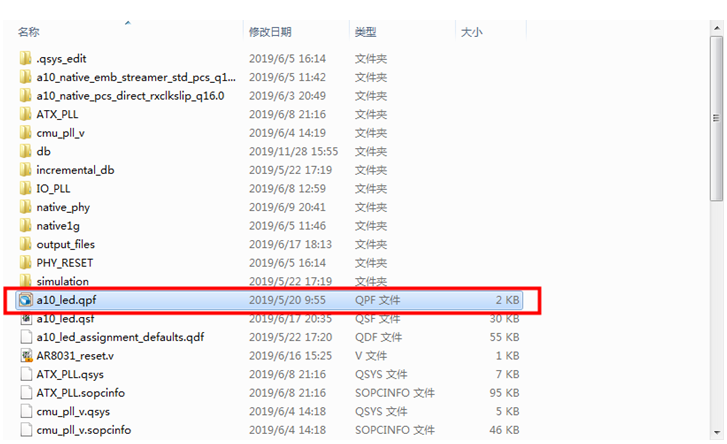

一、打开或新建工程

使用软件“Quartus 18版本”打开光纤工程,这里我选择的是明德扬的工程,芯片型号是10AX027H4F34I3SG,大家做的时候可以新建任意工程。

二、配置IP核

在本工程里,我们需要给工程配置三个IP核,分别是:ATX_PLL、PHY_RESET以及光纤的IP核native_phy。

1. 配置IP核ATX_PLL

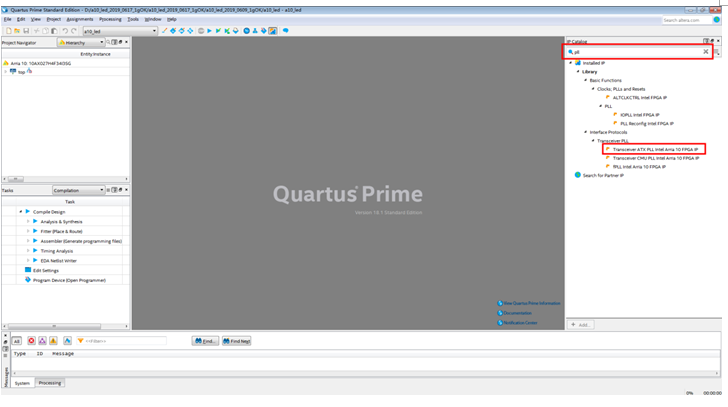

在工程界面的右边搜索“pll”,双击选择“Transceiver ATX PLL Intel Arria 10 FPGA IP”(如下图所示)。

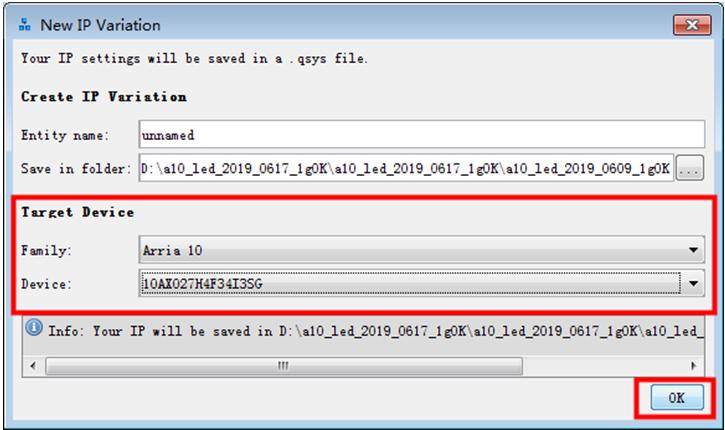

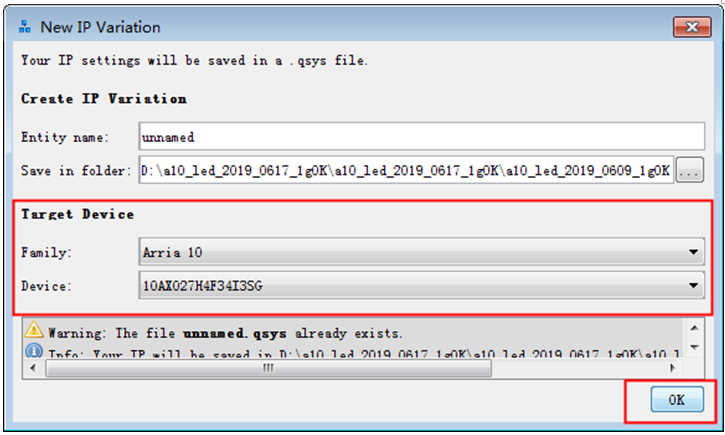

然后出现如下界面,检查一下芯片的系列和型号是否正确,点击“OK”确认。

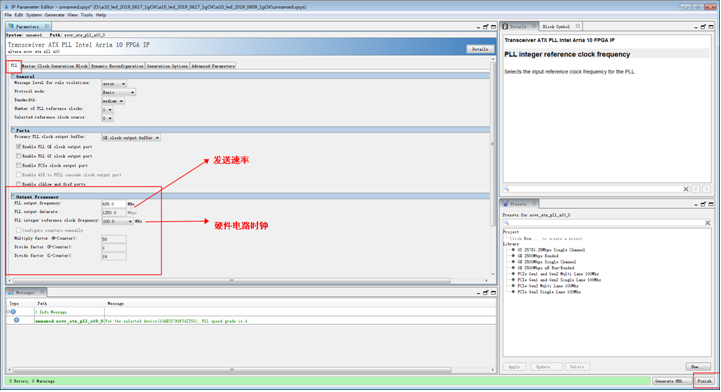

在ATX_PLL IP核配置界面,选择页面“PLL”,在“Output Frequency”选项下的“PLL integer reference clock frequency”选择为“100.0”;并且配置“PLL output frequency”和“PLL output datarate”相关参数,然后点击“Finish”。

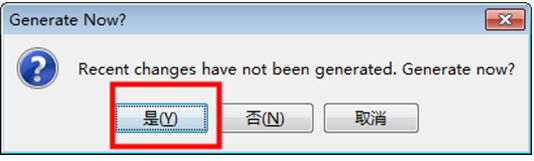

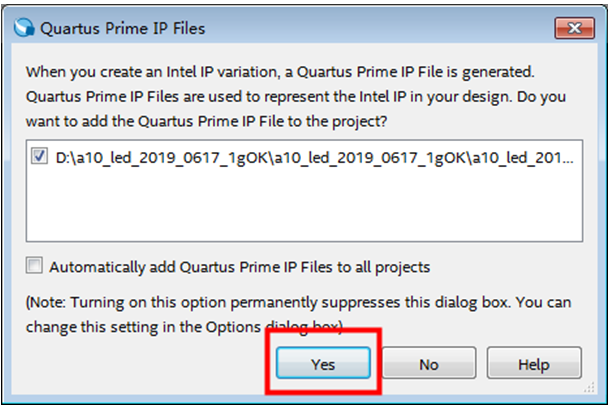

弹出确认的界面如下,点击“Yes” 添加进工程:

2. 配置IP核PHY_RESET

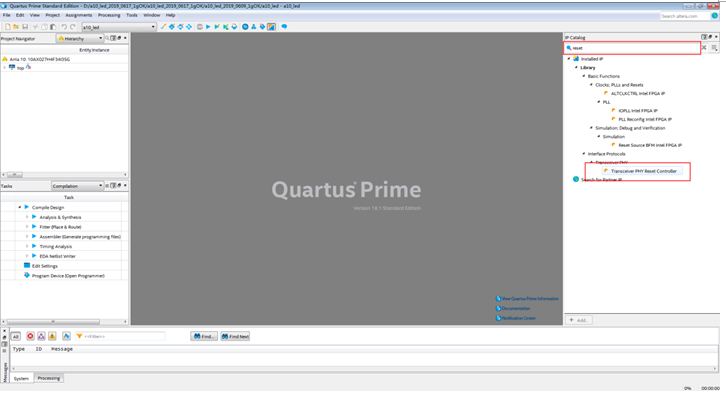

关于IP核PHY_RESET的配置:在工程界面的右边搜索“reset”,双击选择“Transceiver PHY Reset Controller”(如下图所示)。

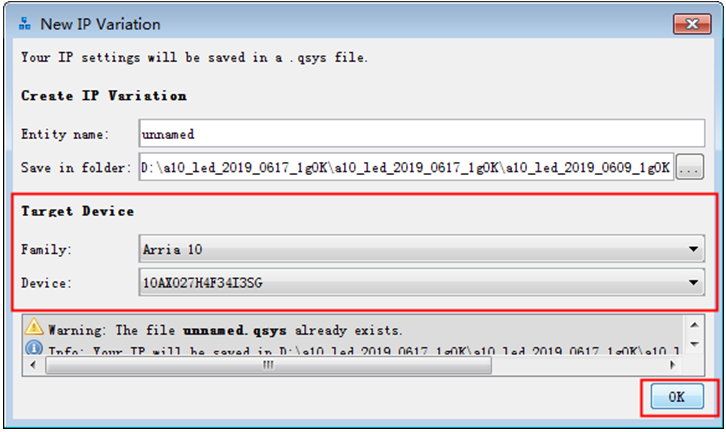

然后出现如下界面,检查一下芯片的系列和型号是否正确,点击“OK”确认。

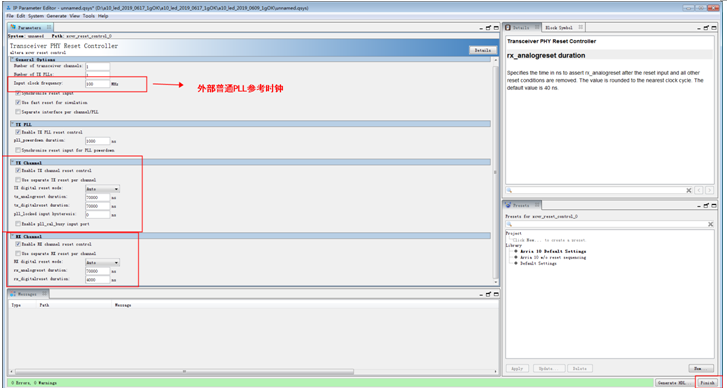

在PHY_RESET IP核配置界面,在“General Options”选项“Input clock frequency”配置为“100.0”;在“TX Channel”选项下“tx_analogreset duration”和“tx_digitalreset duration”都配置为“70000”;在在“RX Channel”选项下“rx_analogreset duration”配置为“70000”,然后点击“Finish”。

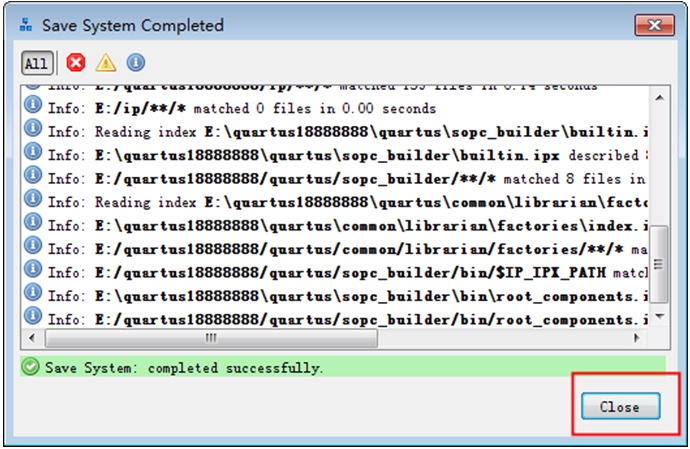

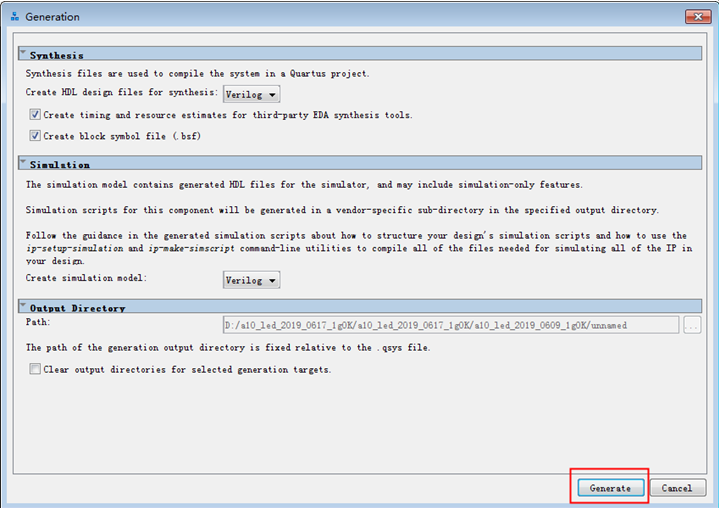

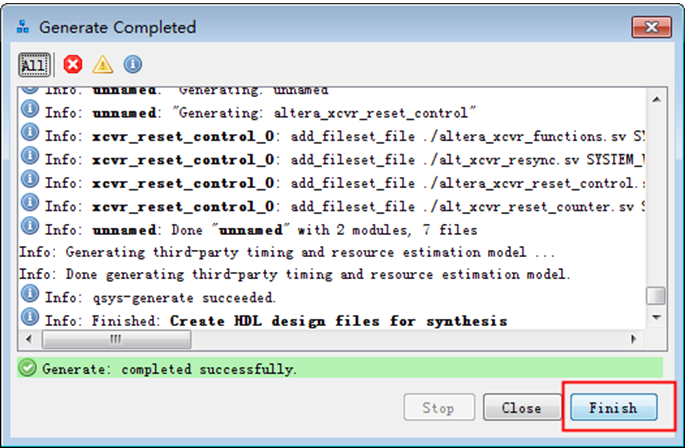

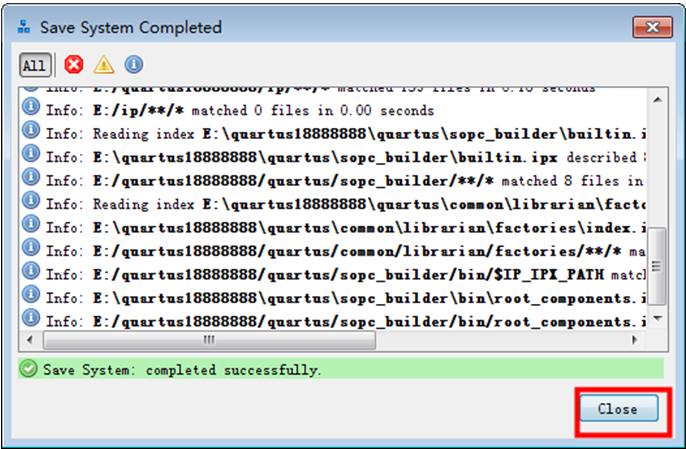

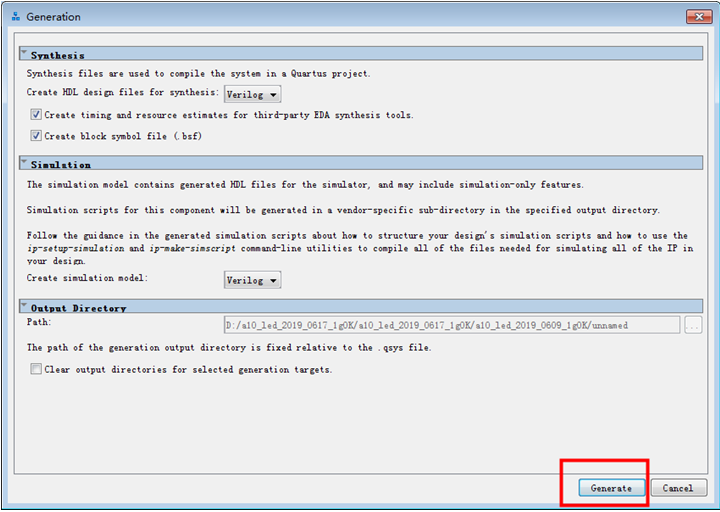

弹出界面如下,点击“Close”à“是”à“Generate”à“Finish”确认。

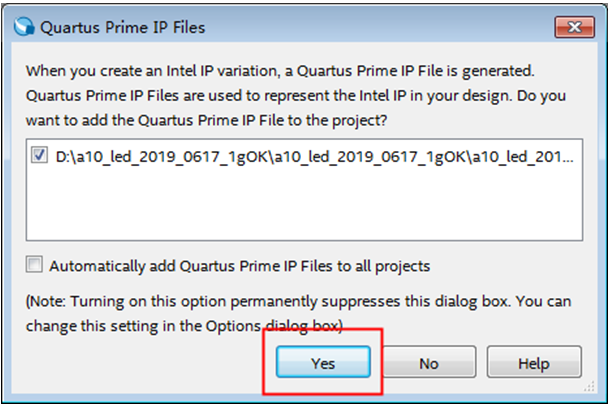

弹出确认的界面如下,点击“Yes” 添加进工程:

3. 配置IP核native_phy

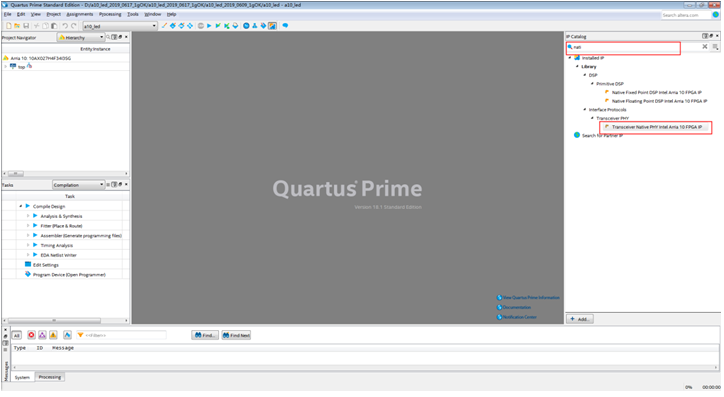

关于光纤IP核native_phy的配置:在工程界面的右边搜索“nati”,双击选择“Transceiver Native PHY Intel Arria 10 FPGA IP”(如下图所示)。

然后出现如下界面,检查一下芯片的系列和型号是否正确,点击“OK”确认。

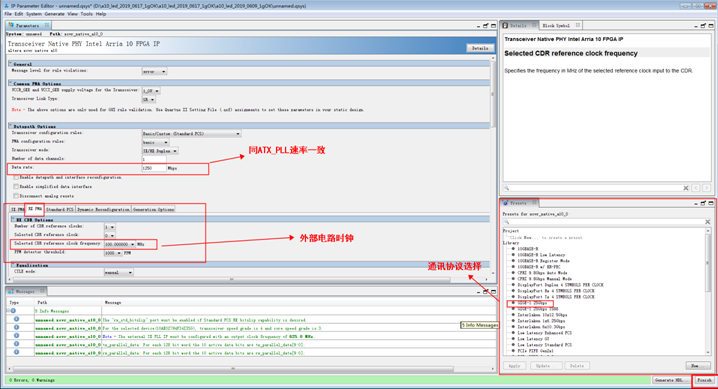

在Native PHY IP核配置界面,在“Datapath Options”à “Data rate”配置为“1250”,与ATX_PLL配置的速率一致;选择“RX PMA”页面 à“Selected CDR reference clock frequency”选择为“100.000000”,与外部电路时钟一致;在右下角“Presets”页面 à“Library”à选择通讯协议“GIGE-1.25Gbps”,然后点击“Finish”。

弹出界面如下,点击“Close”à“是”à“Generate”à“Close”确认。

弹出确认的界面如下,点击“Yes” 添加进工程:

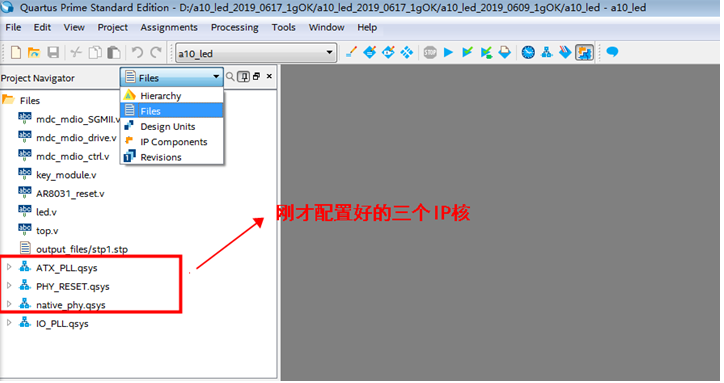

三、确认是否成功

返回“Project Navigator”界面 à 选择“Files”,能够清楚的看到刚刚配置好的IP核都添加进工程里了(如下图所示)。

以上就是基于Altera的IP核配置的具体操作,如有不明白的地方可以加我的QQ:1479512800,共同讨论,期待与大家一起探讨进步!