本文为明德扬原创文章,转载请注明出处!

LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。由于其可使系统供电电压低至 2V,因此它还能满足未来应用的需要。此技术基于ANSI/TIA/EIA-644 LVDS 接口标准。LVDS 技术拥有 330mV 的低压差分信号 (250mV MIN and 450mV

MAX) 和快速过渡时间。 这可以让产品达到自 100 Mbps 至超过 1 Gbps 的高数据速率。此外,这种低压摆幅可以降低功耗消散,同时具备差分传输的优点。

由多个数据位和时钟组成的源同步接口已成为电子系统中移动图像数据的一种常用方法。比较流行的标准是7:1LVDS接口(用于通道链路、平面链路和摄像机链路),它已经成为许多电子产品的通用标准,包括消费设备、工业控制、医疗和汽车远程信息处理。在这些应用中,使用低成本FPGA进行图像处理的做法已经变得相当普遍。

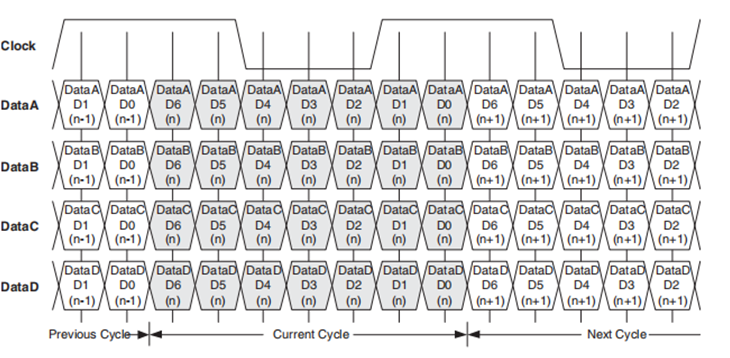

7:1 LVDS接口是一个源同步LVDS接口。如图1所示,为低速时钟的每个周期序列化7个数据位。通常,接口由四个(三个数据,一个时钟)或五个(四个数据,一个时钟)LVDS差分对组成。四对转换为21个并行数据位,五对转换为28个并行数据位。注意,在时钟上升沿和字边界之间有一个2位偏移。每个字节有7位长。

每个通道包括一个串行LVDS数据对和一个源同步LVDS时钟对。接收方接收到该串行LVDS数据,对其进行反序列化,并将其对齐到原始单词边界,生成7个并行LVTTL数据位。7:1发送器将7个LVTTL并行数据位串行化为一个LVDS数据位,并将该串行数据通道与LVDS时钟一起传输。

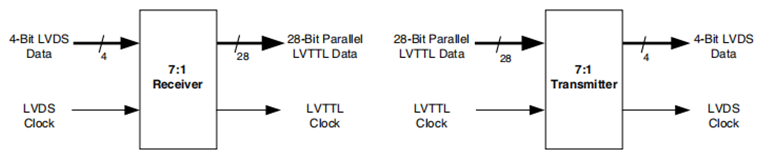

图2显示7:1接收方接收4个LVDS数据通道。当反序列化时,它生成28位宽的并行数据。类似地,7:1发送器序列化28位并行数据,生成4个LVDS数据通道。

图2 7:1接收方与发送方

基于FPGA的通道链接和平面链接样式接口的需求包括四个关键组件:高速LVDS缓冲区、用于生成反序列化时钟的锁相环、输入数据捕获和传动装置以及数据格式化。数据和时钟以LVDS格式接收或发送到FPGA或从FPGA发送,数据速度相对较快。准确的速度取决于分辨率、帧速率和显示器使用的颜色深度。例如,800x600到1024x768显示器要求LVDS数据在60 Hz到75 Hz的刷新率下从40 MHz传输到78.5 MHz。这意味着LVDS的数据速率为280 Mbps到549 Mbps。更高分辨率的显示器,如1280x1024 60 Hz,则需要使用108 MHz LVDS时钟传输数据。对于这个系统,数据传输速率为756mbps。

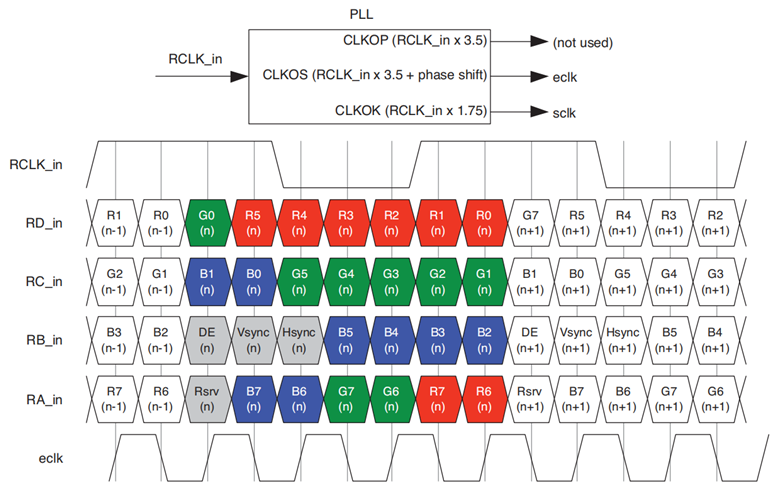

在LATTICE ecp3、LATTICE ecp2 /M或LATTICE exp2实现中,输入捕获电路使用双数据速率(DDR)寄存器,在时钟的上升和下降沿捕获数据。当作为接收器工作时,所提供的低速时钟必须乘以3.5倍,以便在两个时钟边缘捕获数据。如果输入捕获电路只在时钟的一侧工作,则必须使用7的倍数。

理论上可以有这么一种替代方案:可以通过生成7个相移形式的低速时钟,并使用7个不同的寄存器捕获输入数据。然而,时钟生成和分发的挑战使得这种方法在FPGA实现中难以应用。低速时钟必须具有相对较低的抖动,因为它的抖动必须在总体定时预算中考虑。类似地,用于将时钟提供给输入或输出寄存器的时钟分布网络偏差必须在任何时序分析中考虑在内。

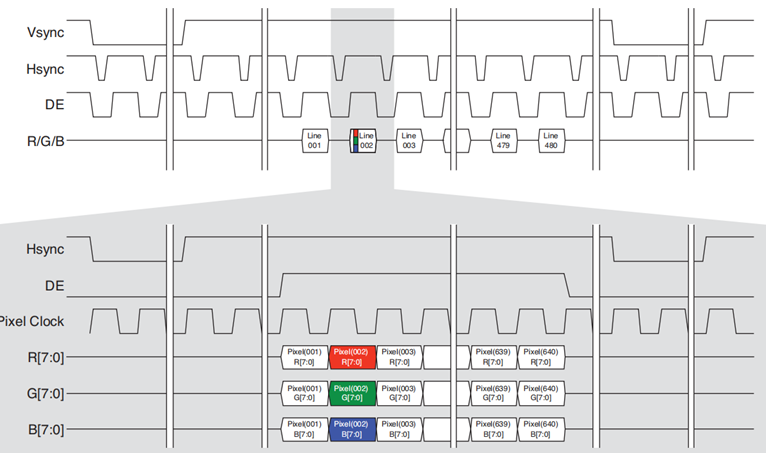

为了传输高速数据,发射机必须将用于传输低速并行数据的时钟倍频3.5倍(在DDR模式下)。同样,时钟的抖动及其分布的偏差也很重要,因为它们影响接口的时间预算。图3显示了锁相环时钟的生成,以及如何将视频帧第2行的一个像素的R、G、B位、Vsync、Hsync和DE分配给4个LVDS数据对。数据位在eclk时钟上升和下降的边缘上采样。

图3 视频信号时序和7:1 LVDS通道链路接口

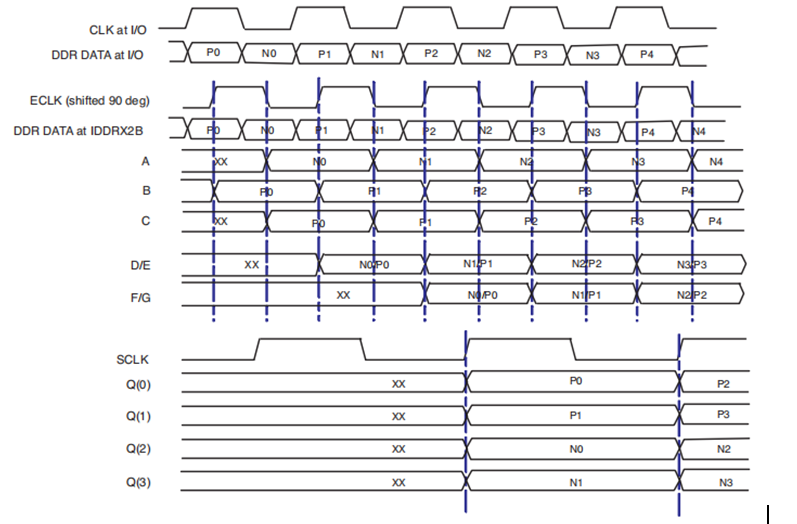

输入端双数据速率采样如图4:

图4 接收端使用DDR采样

我们的LVDS视频开发项目使用的便是这种模式,内部eclk是输入时钟的3.5倍频时钟,中间经过解串、RGB映射后与摄像头采集的数据进行拼接,最后再将并行数据转换为串行数据输出。如有不明白的地方可以加我的QQ:3358622769,我将会具体的向有需要的同学进行指导。期待与大家一起探讨进步!