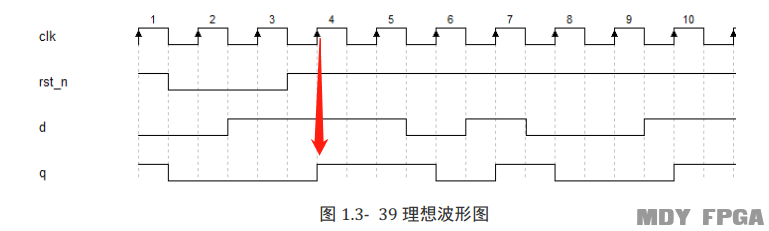

答:FPGA在做功能仿真的时候,通常是如下理想的波形:数据变化和时钟上升沿是对齐的。

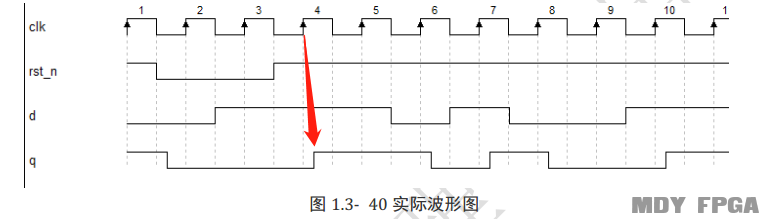

上面是理想的波形。但实际上,FPGA是硬件电路来的,信号是在时钟上升沿的触发下变化的,即先有时钟上升沿,再有信号的变化。信号的变化,是稍微延迟于时钟的。因此更实际一点的波形如下图。

我们编写测试文件的时候,是模拟数字电路的情况,因此在给激励的时候,就应该模拟上图那样给信号,比较理想的情况,是信号稍微延迟于时钟上升沿一点点,例如延迟1个单位:#1。(这个时候时钟波形就是“1个周期-1ns”,总之不是一个完整时钟周期)

但是很多情况下,有没有必要延迟上升沿一点点呢?延时多一点点(例如改为#5)也无所谓嘛,这个时候波形就像是“1个周期-5ns”(也不是一个完整周期)。反正你看代码的时候,只看时钟上升沿有效的时刻就可以了。

如果你有强迫症,那您就把那个#5改为#1,甚至改为#0.01都行,越小,越像是一个完整的周期。

BY THE WAY,其实纠结于上面问题,最根本原因,是“凭感觉来做设计”,因为觉得“看起来不是一个完整周期”(差5ns和差1ns其实都不是一个完整周期)。其实只要做过仿真,对着代码和波形多对比,是很容易找到问题所在的。