如果同学们的问题我们帖子里面没有的请第一时间联系我微信同步:18022859964江老师,我们对新问题进行补充!

通过平时同学们反馈学习中经常用到的学习点,因此明德扬最近做了抖音系列短视频,都是一些FPGA学习技巧分享,

大家感兴趣可以关注明德扬抖音号:87481069842.内容不断更新!记得关注点赞学习不迷路!

【问题1】FIFO总共128个数据,都读到128个数据后,usedw对应还是1,而不是预期的0。

总结:对于FIFO出现了”莫名其妙问题“时,需要严谨检查和确认。

建议的方法:

a. 直接看FIFO这个IP核的输入输出信号,例如读使能、写使能、写数据、空信号、满信号等。写一个,确认;读一个,再确认。

b. 注意FIFO满时不要再写,FIFO空的时候不要再读,否则会出现意想不到的错误。

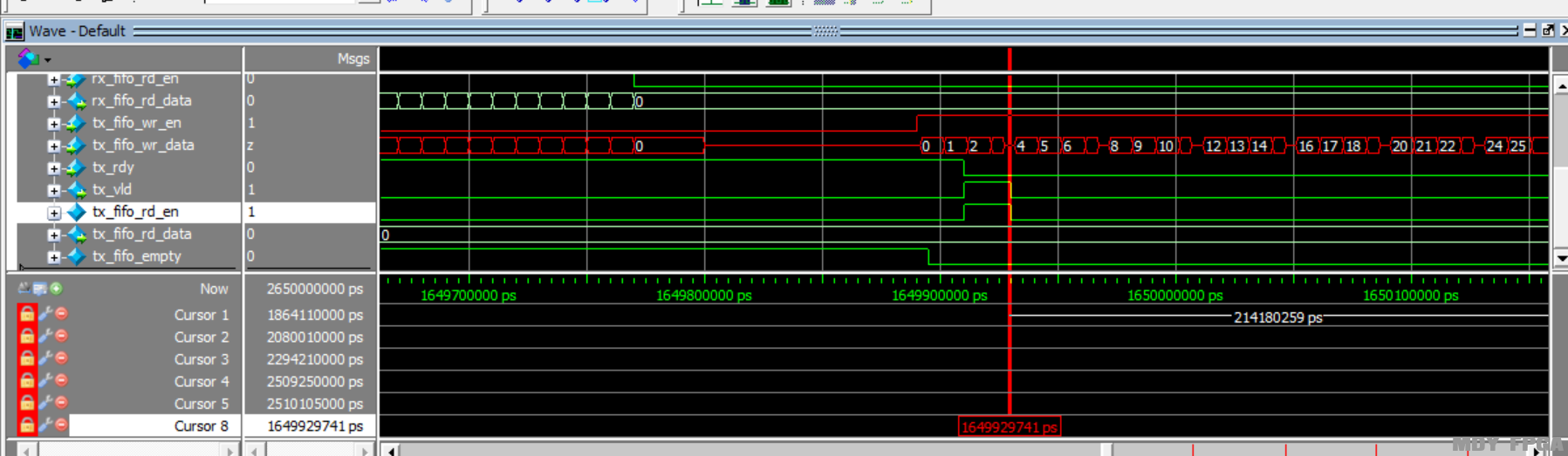

【问题2】对于双时钟 show ahead 模式,给出第一个读使能为啥读出数据不对呢?

答:首先,从波形图看到的信息,数据为“0”,而不是“没有数据”。

其次,假如第一个数据不对,需要看前面的第一个写使能有效的时候,写数据是多少。即检查第一个写数据和第一个读到的数据正不正确。

【问题3】FIFO中的空信号有延迟怎么办?

答:1.写数据之后,过一段时间empty信号才变低,这个延时是FIFO的特性,是固有的;

2.其次,这个空指示信号的延时不会对设计有影响:空信号一般用于读侧,有数据就读,没数据就不读,是不关心延时的。

3.FIFO里空信号和满信号都是绝对是准确的,但是usedw信号的延时是不确定的,所有要严格要求时序对齐的就不要用usedw这个信号。

【问题4】关于用寄存器矩阵搭建一个8x32的fifo,用6位的计数器指示读写指针和表示空满,但是跨时钟域需要打拍,那该如何准确的判断空满信号呢?

答:该问题应该是有一个认识误区,认为“准确判断”指的是“立刻实时指示”,也就是误以为,写一个数据进去,空信号立刻变成非空状态。这“立刻”其实是没有必要的。 正确的做法是,写一个数据进去,然后内部做跨时钟域处理,隔几个时钟后,空信号才变成非空。虽然有延时,但不影响状态的判断。【问题5】vivado fifo(深度为32),almost_full是不是在写了31个后为1,此时full为0?同理almost_empty是不是在读剩下1个深度数据的时候为1,并且此时emtpy为0?

答:almost_full是指将要满,almost_empty是指将要空,至于什么是“将要”,一般可由用户来定义。建议看数据手册。

【问题6】FIFO仿真的时候,读数据和写数据个数对应不上,如写5读,只读出2个;如写了5个,读出6个等。

答:经常收到学员反映,FIFO仿真的时候读写的个数不正确。经过远程协助过多位学员后,均发现是学员自己没有认真看波形而误解的。

当FIFO与预期不正确时,应该要仔细看波形,具体怎么做?

1. 只看FIFO这一模块的接口的信号,不要外部的信号。(避免例化出错的情况)

2.查看写时钟、写使能和写数据,以写时钟上升沿为界,一个一个时钟去看写进去的数据,用笔记下来。

3.查看读时钟、读使能和读数据,以读时钟上升沿为界,一个一个时钟去看读出来的数据,与写数据逐个核对。

4. 认真仔细核对,不要马虎。

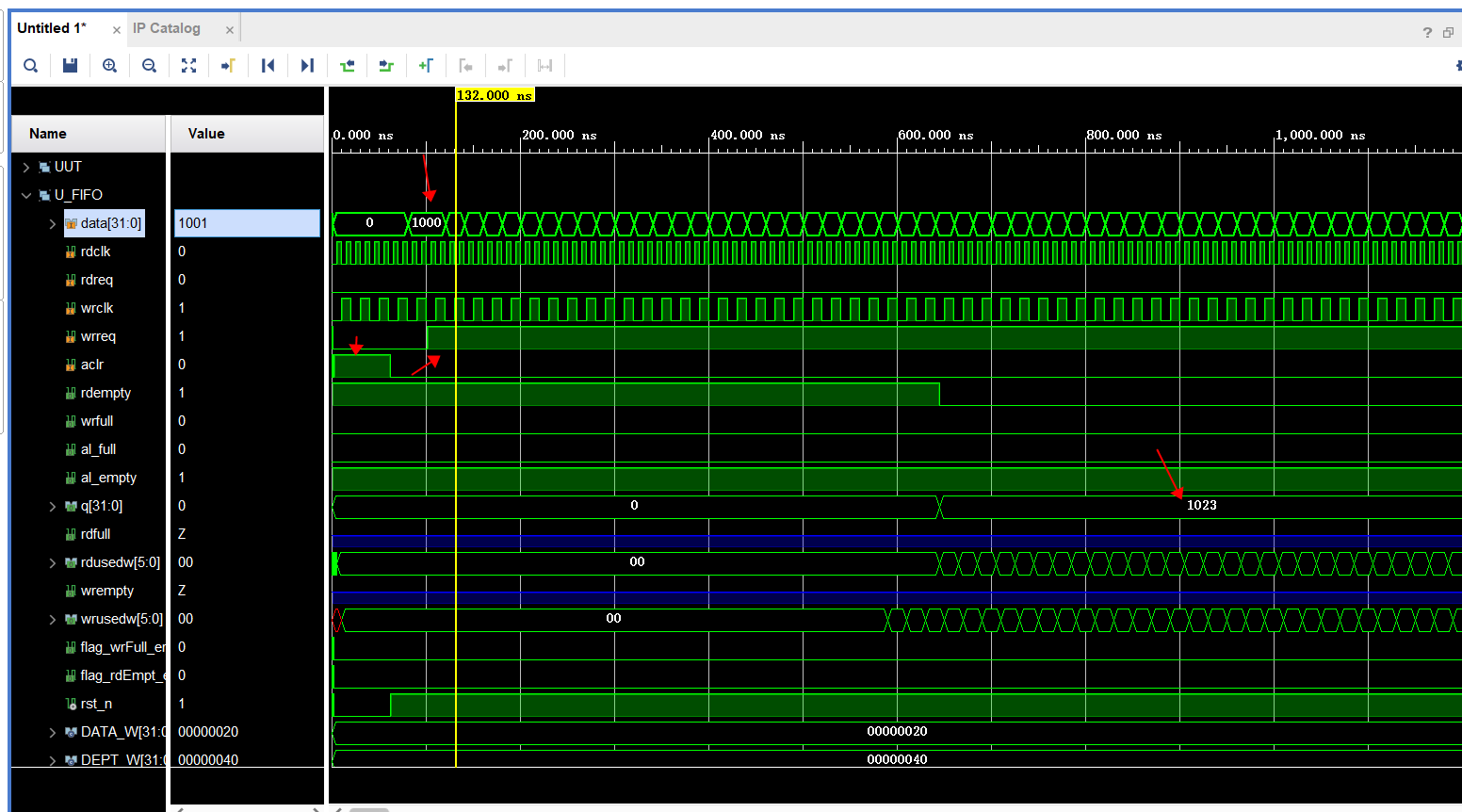

【问题7】在仿真Vivado生成的fifo的时候,发现复位之后,没有往fifo里面写入数据,仿真图如下图所示:写入的数据依次为1000、1001、1002一直按顺序往后,

仿真发现实际写入的第一个数据为1023,写使能、写时钟、复位都没有问题,这是什么原因造成的?

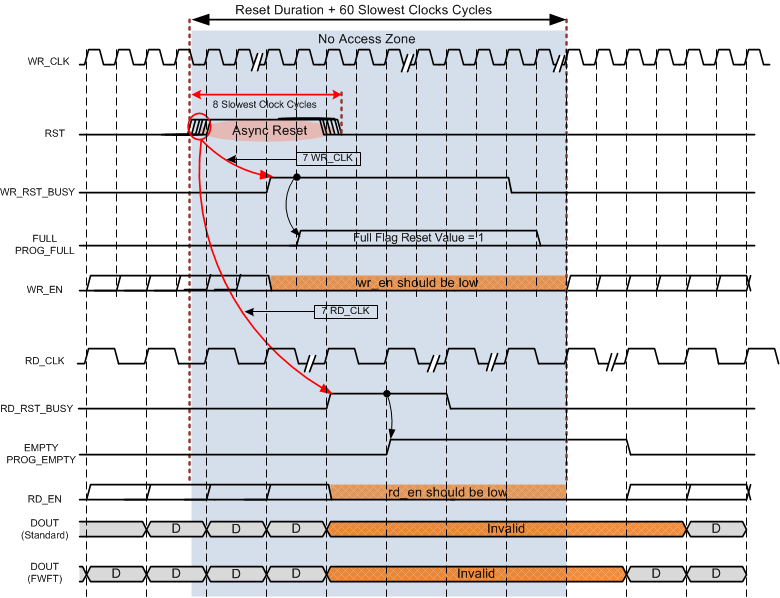

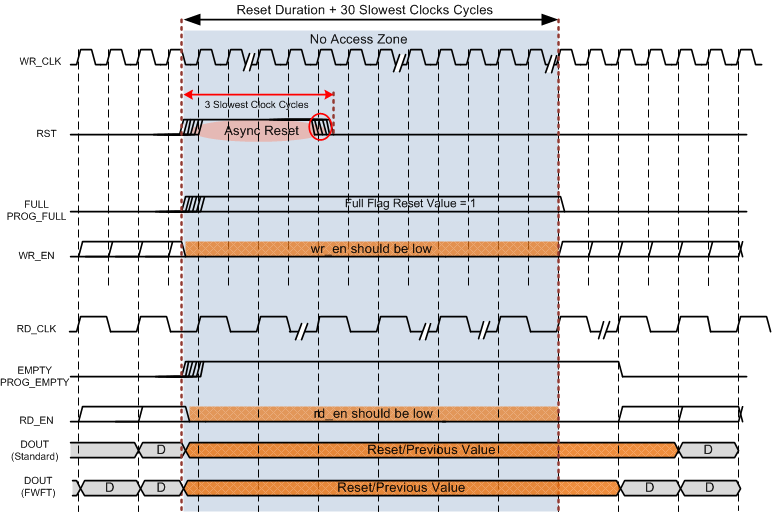

答:该问题是由于使用了Vivado中FIFO的”异步复位“导致的,数据手册有说明,当使用异步复位时,分为两种情况,当具有安全电路时,复位后需要有60个时钟周期的缓冲时间;

答:该问题是由于使用了Vivado中FIFO的”异步复位“导致的,数据手册有说明,当使用异步复位时,分为两种情况,当具有安全电路时,复位后需要有60个时钟周期的缓冲时间;

没有安全电路时,复位后需要有30个时钟周期的缓冲时间。这一操作的目的是为了避免故障和亚稳态的出现。时序图如下图所示:

若使用同步复位,则不会出现上述的情况。

【问题8】 异步FIFO的空和满都不是绝对的,有时候异步FIFO中已经有几个数据了,也不会显示非空,同样,快满的时候有时候就会显示已经满了,是这样的么?

要是这样子的话,那么问题来了,我现在如何能将异步FIFO读空呢?

答:请看本贴的【问题4】

【问题9】请问VIVADO使用教程中,FIFO模板在哪里可以下载?

答:  mdyFifoAsyVivado.v

mdyFifoAsyVivado.v

mdyFifoSynVivado.v

mdyFifoSynVivado.v

FIFO在FPGA开发中经常使用,围绕着FIFO,可以完成很多功能开发,如想学习,可以购买FIFO专题课。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 前端模拟采集、射频、电荷灵敏前置放大器

明德扬科技教育

明德扬科技教育