|

通过平时同学们反馈学习中经常用到的学习点,因此明德扬最近做了抖音系列短视频,都是一些FPGA学习技巧分享,

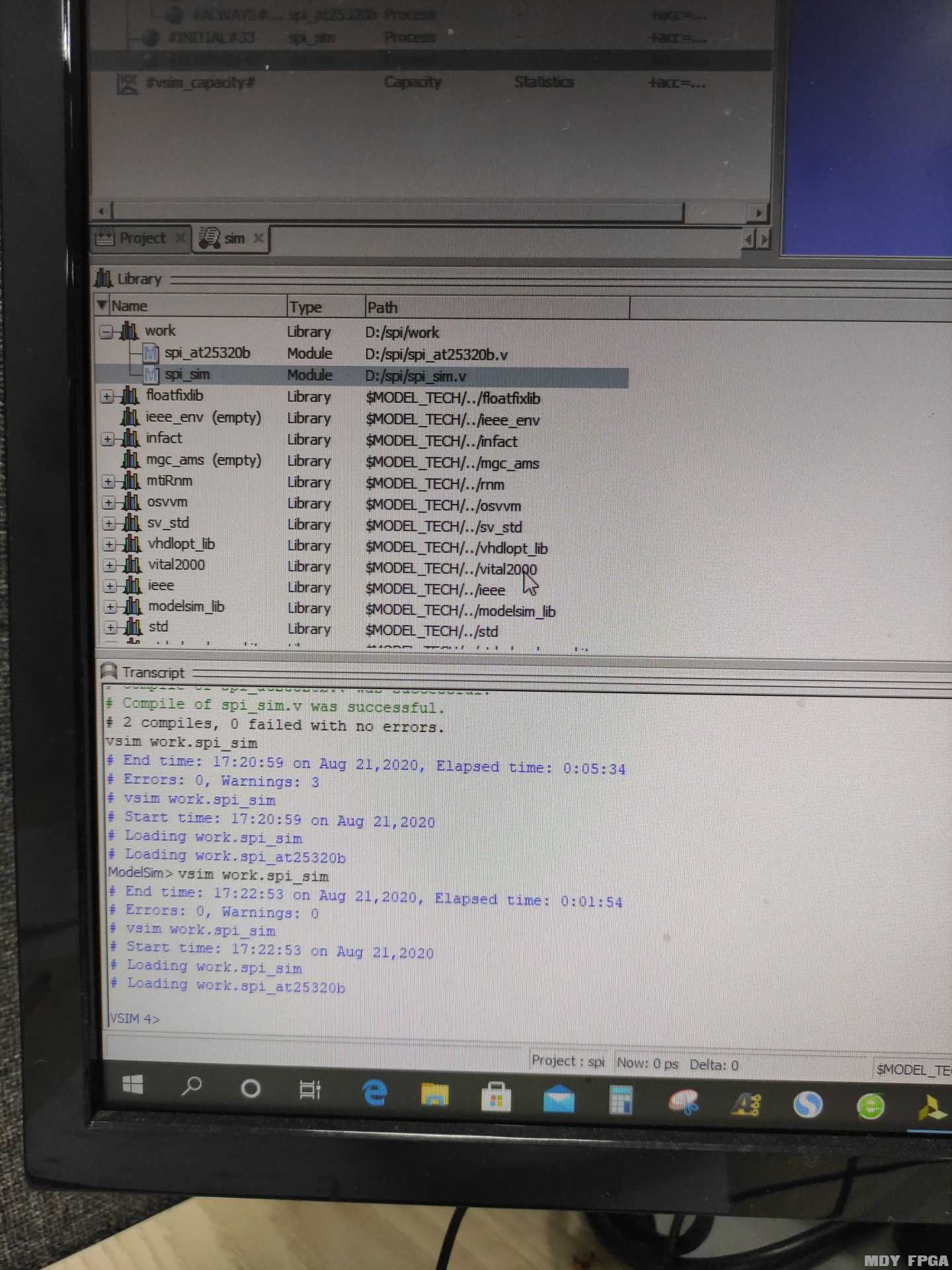

【教程1】看波形图的方法,请看B站视频,一共才8分钟:https://www.bilibili.com/video/BV1yf4y1R7gH?p=44

【教程2】如果还想了解项目中是如何看波形的,可以看这个案例(要仔细看,要看细节,特别是老师如何对着代码和波形来看的)

https://www.bilibili.com/video/BV1yf4y1R7gH?p=51

答:modelsim中的各个界面都可以再上方的View中找到, 如果某个窗口不小心关掉,可以再view中找到,重新打开。

答:定义一个xxx

显示效果是

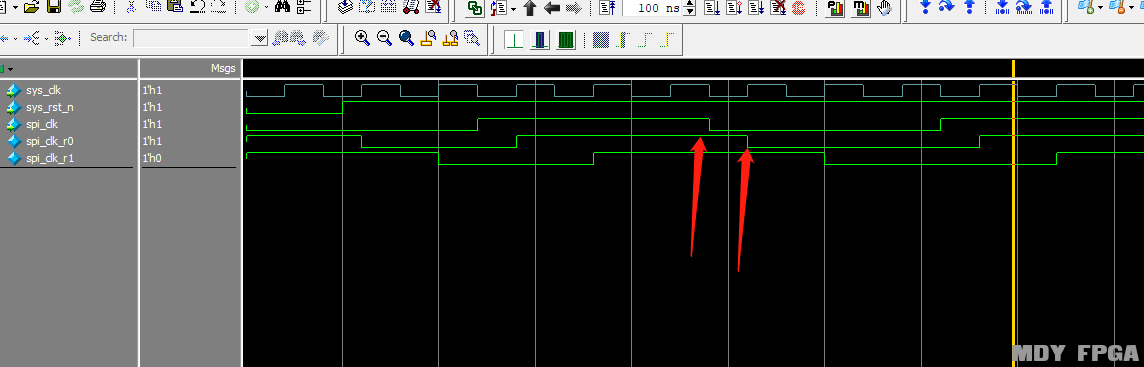

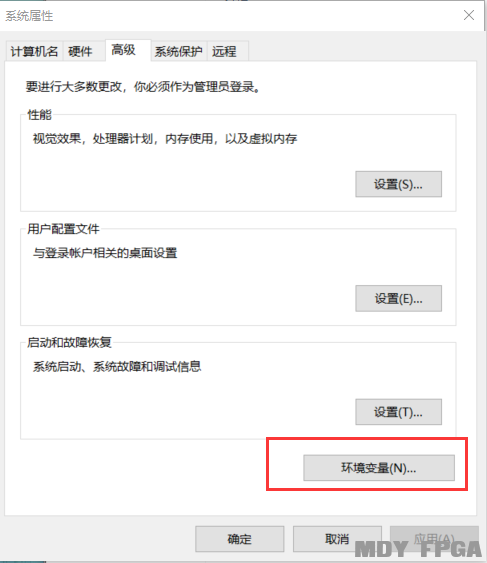

【问题3】当用modelsim在观察波形的时候,添加新的波形进去,发现没有数据,代码无改动,新添加的信号之前是有波形的,是什么原因? 【问题4】软件安装是,有一个步骤是设置环境变量,如何做? 答:在控制面板中找到“编辑系统环境变量”,  然后再“变量名”中填入如图所示内容,再变量值中写入LICENSE.TXT文件(破解器生成的)存放的位置  【问题5】按照MDY看波形的技巧:时钟上升沿前看输入信号,即信号等于1后,下一个时钟沿才检查到该信号为1。 但我在仿真的时候,发现是信号变1的瞬间就检查到了。 答:该问题的解答,请看如下贴子:关于在仿真软件中计数器提前计数的问题 http://www.mdy-edu.com/wentijieda/20210409/1211.html?1617952276

【问题6】仿真的时候,一些信号出现红线,是怎么回事? 【问题6.2】时钟为什么是红色的,没有变化? 答:这个问题跟【问题6.1】是相似的,本问题是上图中的信号clk为什么是红色的。 基本的思路是:找到这个clk的代码,看这代码执行了没有。由上图中的信号列表可以看到,clk是UART模块的输入,它本应来自测试文件,但测试文件有执行吗? 所以根本原因是:仿真时调用的顶层模块有问题,要调用测试文件那个模块,不是设计模块。 更多思路,请参考如下帖子:08 定位问题能力http://www.mdy-edu.com/wentijieda/20210408/1190.html?1617952333【问题7】编写测试文件的时候,要严格模拟真实的外设情况设计激励吗?例如说,外设输出信号dout,

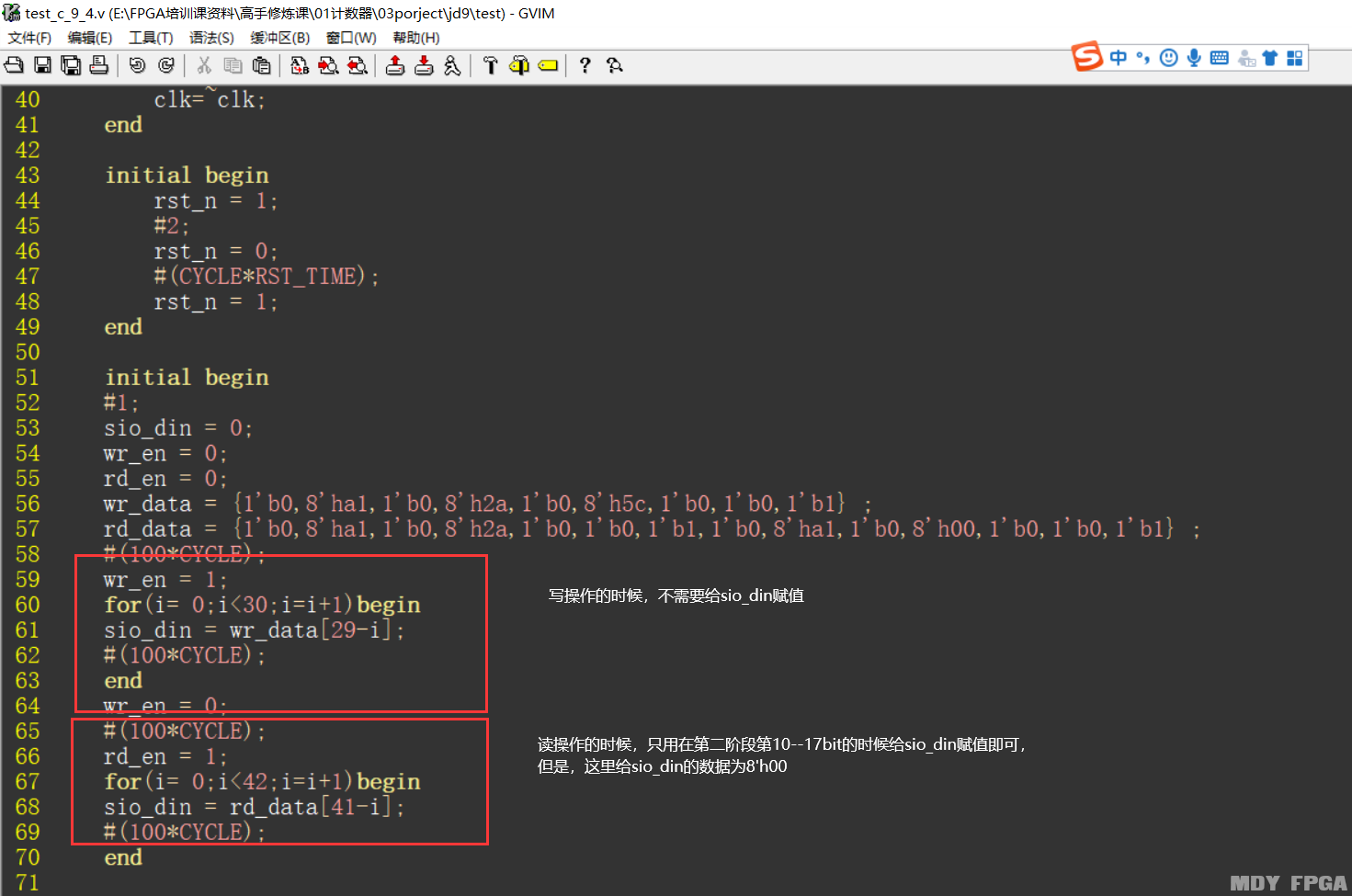

按照时序要求是每1us变化一次,是不是意味着仿真时也要这样做?或者是下面图片的例子 例如上图中的问题,按照时序图要求,sio_din不用“赋值”。但问题是,“不用赋值”和给“0”,到底有什么不同?我们更关心的是,设计代码不要在此期间get这个值就好了。 也就是说,这一段区域,是大家都不关心的,就没有必要去设计得复杂。还有一个例子:dout每1us变化一次,这是真实情况。

但我在编写文件时,每个时钟都给不同的值,然后确认在我需要的时候,能不能获得到当前值,这样更能保证设计要求。

【问题8】带有ip核的仿真中,会提出如下图的错误?(module "dcfifo" is not define)?

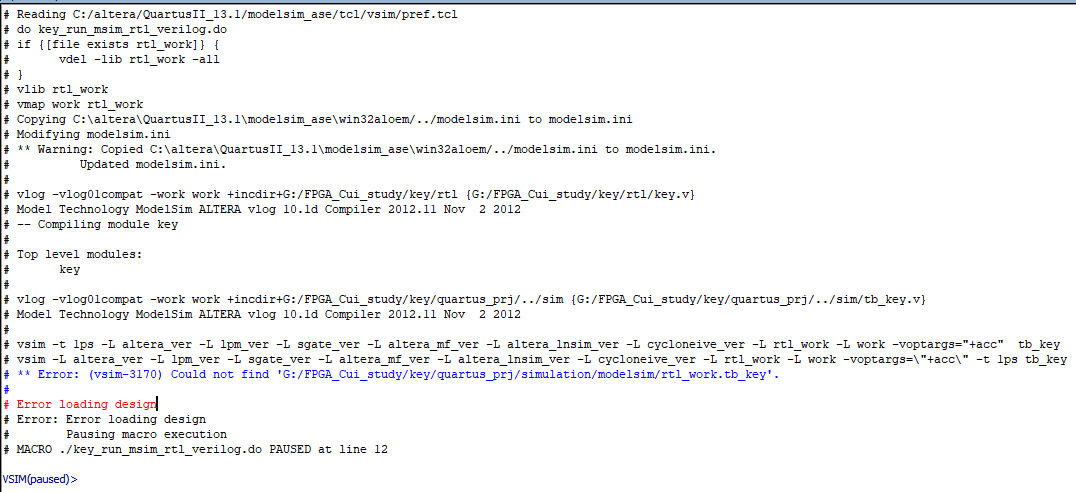

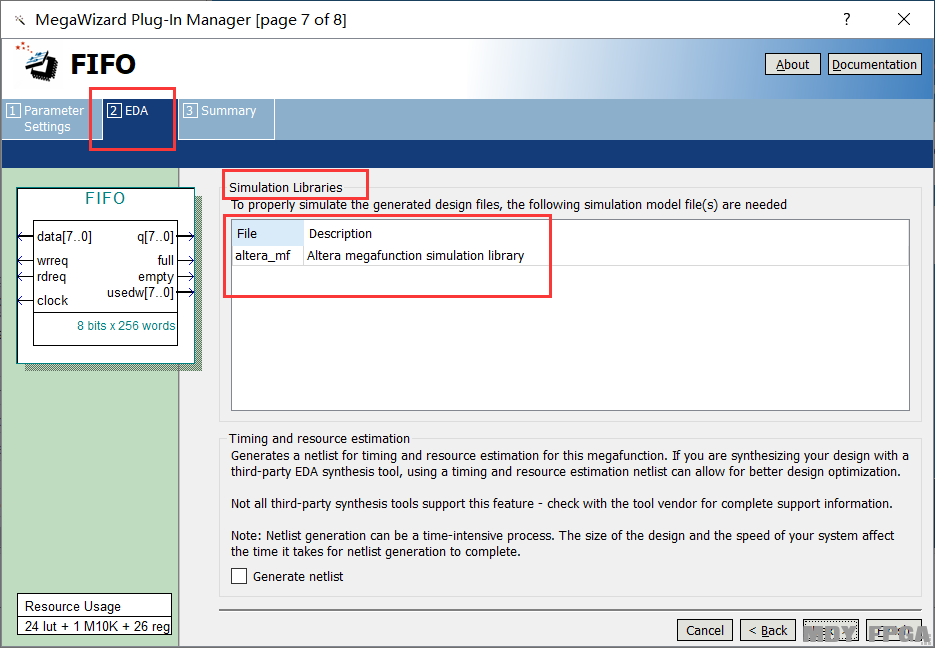

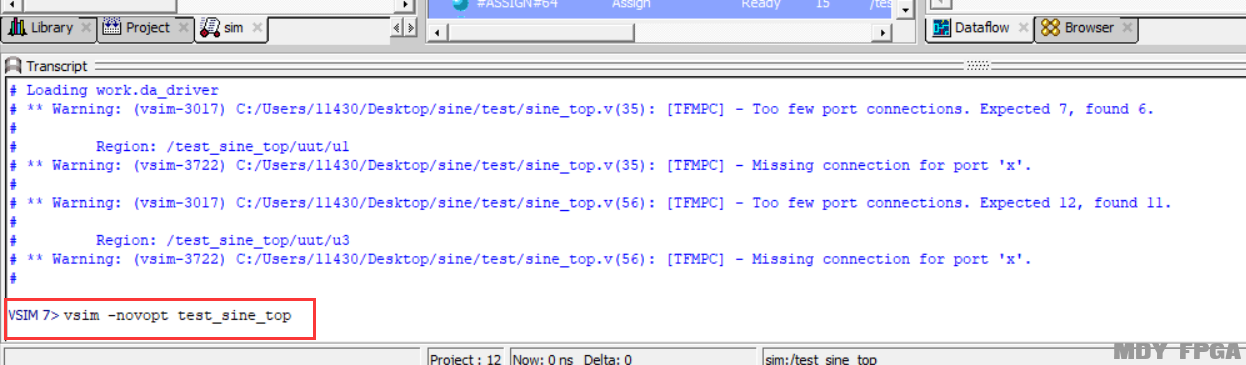

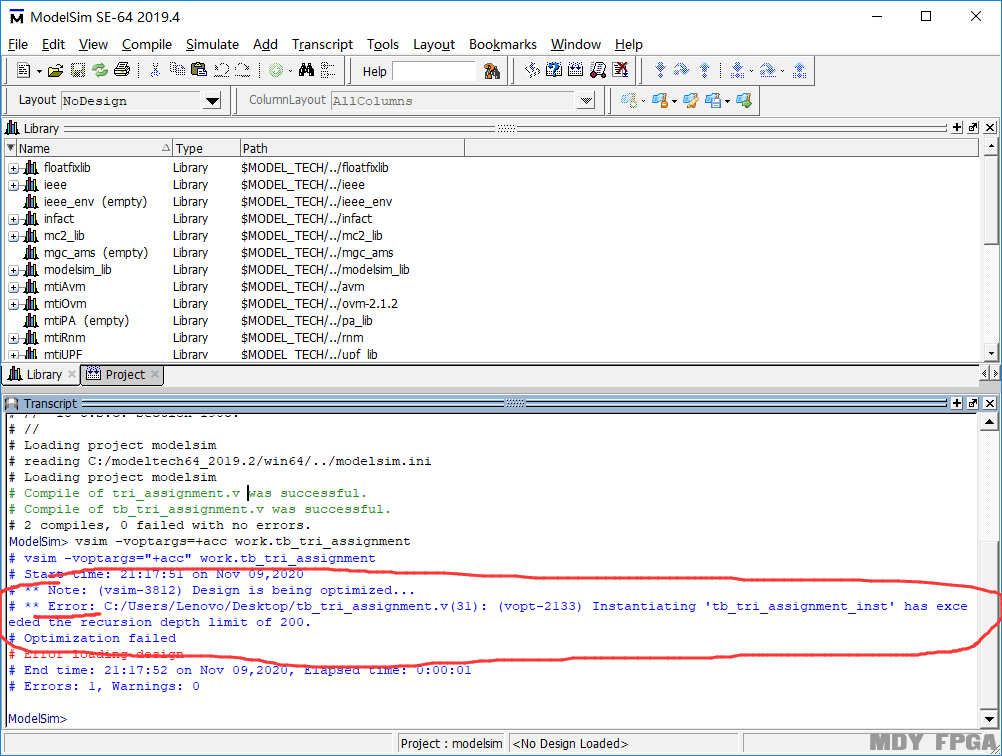

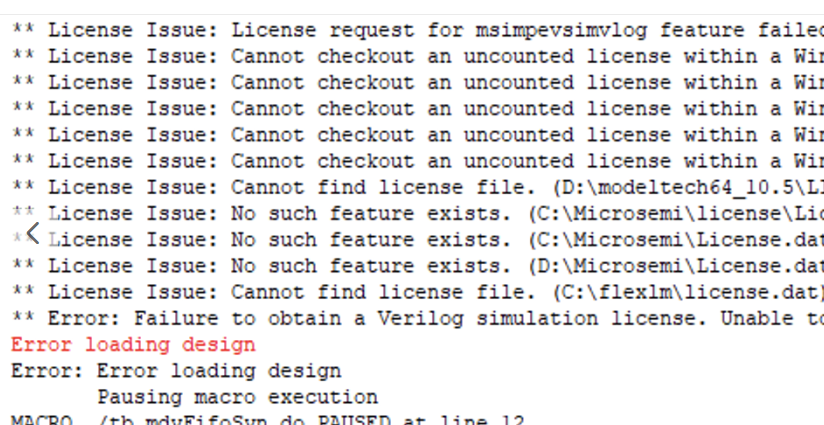

答:在Quartus生成ip核的界面中,一般倒数第二页会说明本ip核涉及到的库文件,大部分常用ip核都只涉及到altera_mf.v这个库文件。 这个库文件应该在Quartus的安装路径下xxxx/quartus/eda/sim_lib这个路径下。 特别需要注意的是,ip核是由哪个Quartus生成的,仿真时就要添加对应Quartus的仿真库文件。【问题9】在仿真的时候,编译全部都是通过的,但是一点击simulat,就会出现“Error loading design”这样的错误,怎么办? 答:出现这个错误的时候,一定要往上找错误的信息,不要盯着“Error loading design”看,比如下面:

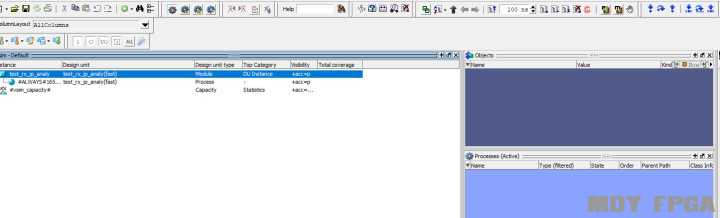

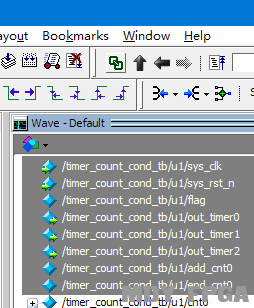

红框部分才是真正需要关注的报错信息。 【问题10】如果修改modelsim显示的进制数?例如将数据以16进制显示。 答:选中该信号,右键,有一个radix选项,在该选项里可以选择要显示的方式。 【问题11】MODELSIM加载程序的时候提示:increasing limit to 75  答:注意看图中的U1,是有很多级的U1。这个U1就是模块名或者例化名,这是因为多级嵌套调用才会出现的问题。 例如,当模块ABC里面,例化了一个模块ABC,这就是自己例化了自己,就会出现问题。 所以,需要检查模块名的正确性。

【问题12】modelsim仿真的波形前面有的是0或1,有的是st0或st1。有什么区别? 答:0和1只表示高低电平,加上st还可以表示强度,也就是表示信号的驱动能力,定义为线网类型的, 比如wire,都有默认的强度,一般是(st0,st1) 【问题13】编译出现:Error: D:/shumaguan/shumaguan_test.v(20):near“initial”;syntax error ,unexpected initial,expecting ' ; ' or ' , ' 答:已经提示了错误的原因,以及位置,请在第20行前后去找,一般是缺少分号或者逗号,或者是写错了

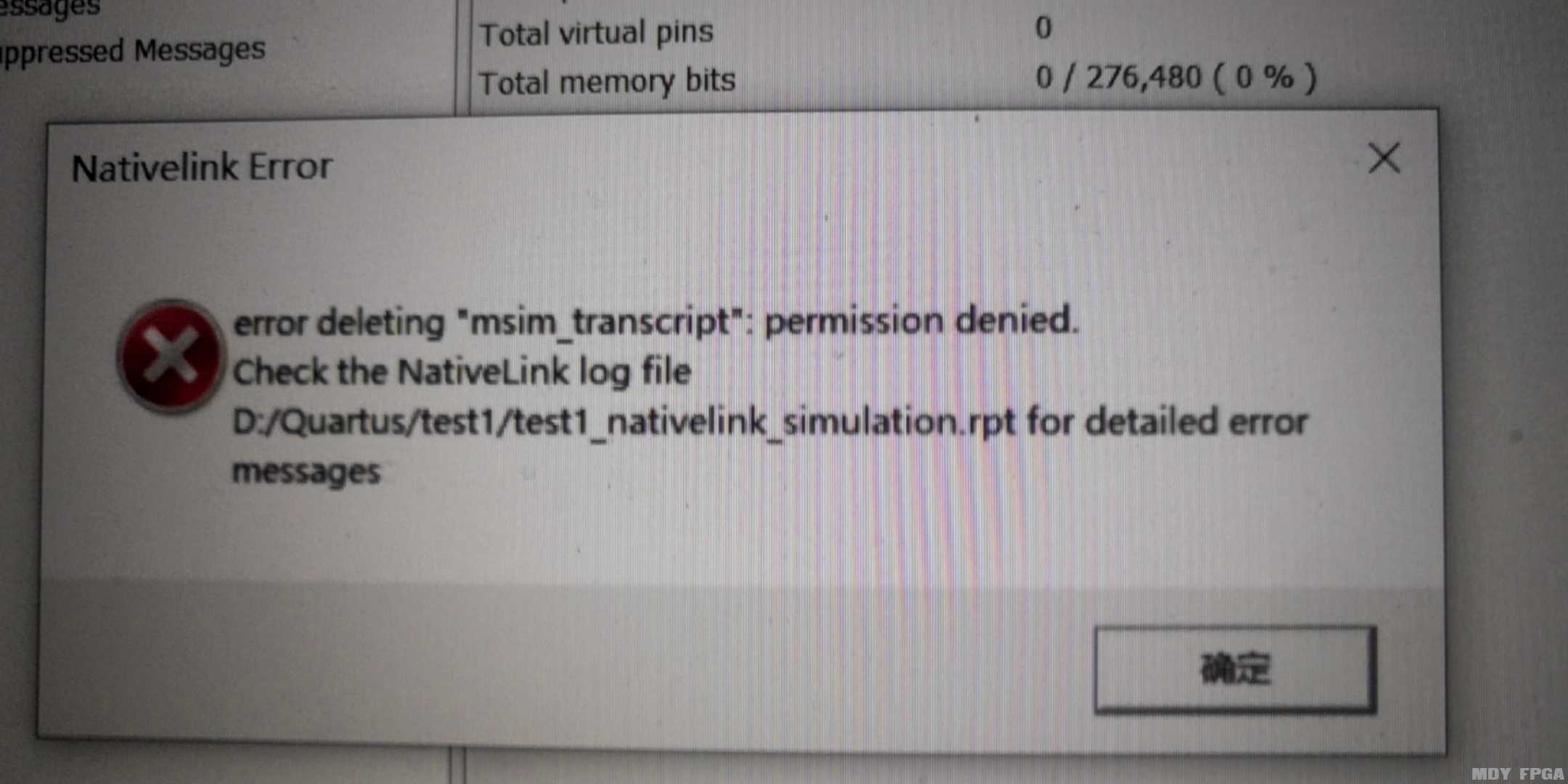

【问题14】出现:Error deleting “msim_transcript”:permission denied.

答:问题原因: 同一工程Modelsim窗口多开。

解决方法: 关闭正在运行的modelsim软件,再启动仿真。

【问题15】想请问下为什么新创建的modelsim工程打不开modelsim显示 : # wrong # args: should be "load file ?pkg? ?interp?"

答:解决办法:检查三个方面。

第一:Modelsim是不是真的破解好了 还有tools---option 那里选择modelsim.exe的路径,modelsim安装在根目录下就不会出现这种问题了。。 【问题16】在使用modelsim进行仿真的时候,如果包含有ip核,都需要添加那些文件? 答:需要添加测试文件、待仿真文件,还有ip核的仿真库文件。 【问题17】ip核如何仿真?仿真库文件在哪里?仿真的时候怎么用? 答:一般ip核仿真需要那些库文件,在生成的时候都会有说明,如下图所示,altera_mf就是这个ip核的仿真库, 直接在Quartus的安装目录下搜索即可,然后添加到modelsim进行编译。 (需要注意的是,altera_mf必须是在生成该ip核的Quartus软件下去找,搜索的时候可能会出现几个,要最大的)  或者直接使用联合仿真,具体操作看视频:https://www.bilibili.com/video/av371751446 另外,对于大型的IP核,例如MAC IP核,仅使用altera_mf.v是不够的, 在生成IP的时候,会同时生成对应的仿真文件,要注意阅读数据手册的说明。 【问题18】仿真时出现这样的提示:Error:E:/rtl/bcd_counter.v(19): (vlog-2163) Macro`d0 is undefind 答:该提示一般是由于信号没有定义引起的,请到指定的错误行, 找到相关的信号,然后再找到信号的定义,检查是否、类型定义是否正确、位宽是否正确。

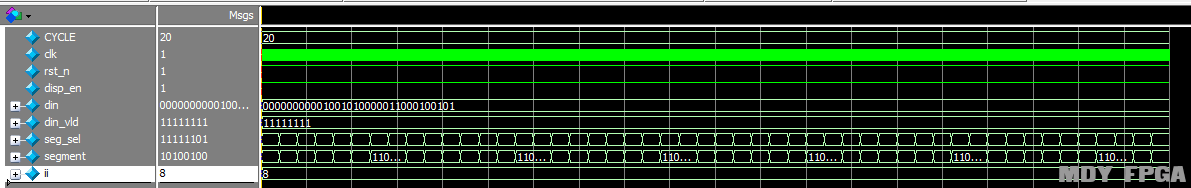

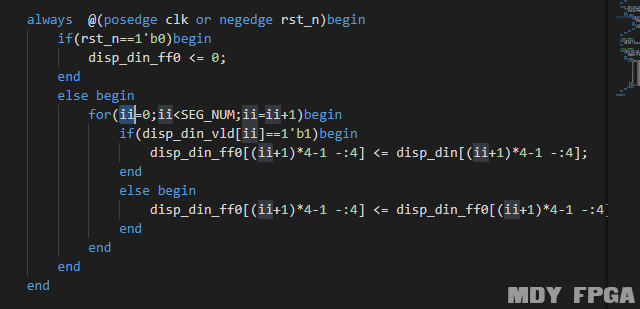

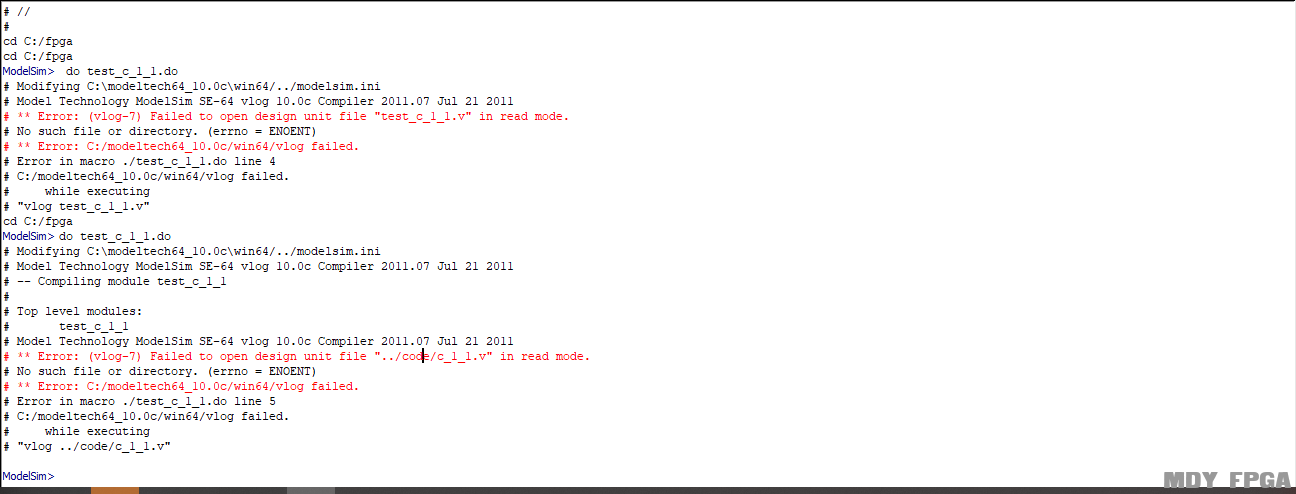

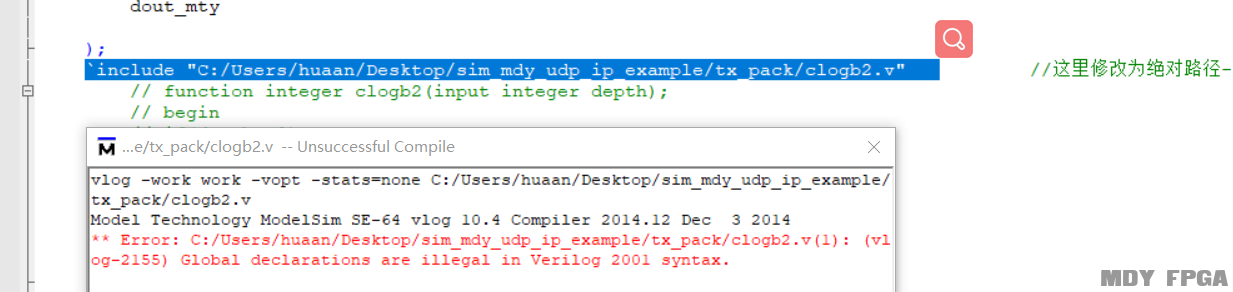

http://www.mdy-edu.com/wentijieda/20210409/1210.html?1617952527(出处: 明德扬论坛) 2、检查测试文件中是否有模块例化 3、可能因为vopt的缘故使得一些不重要的信号被modelsim自动忽略,需要添加选项-novopt, 即vsim -novopt module_name也就是是再modelsim下面输入vsim -novopt module_name,然后回车即可,其中module_name为测试文件模块名     答:因为for语句 其实就是简化操作 等于你把ii分别带入 模块 然后展开写这样。 而不是真正的循环。 【问题21】xilinx联合modelsim仿真时 修改比较少的时候有没有像altera里面的work restart run-all 我在library里面没有找到work选项。 答:在altera平台,默认使用的是work库,所以使用work restart run - all;在XILINX平台, 默认使用的是xil_defaultlib库,所以使用 xil_defaultlib restart run - all。 【问题22】modelsim仿真带有include的.V文件时提示找不到包含的文件,我的所有文件都放在同一个路径下,并且使用的绝对路径依然报错   答:1. 注意看报错的路径里的“/”没有了,所以根本原因,是要用“/”,而不是“”。 2. 如果提示文件找不到,请特别注意路径的格式,您可以尝试用绝对路径就试试。这里容易出错,请自己多去尝试。 【问题23】没有信号就没办法添加,看波形  答:右键addwave添加 【问题24】modelsim10.4仿真错误Error: (vlog-7) Failed to open design unit file "XXXXX" in read mode解决办法  答:此错误消息表示尝试以读取模式打开指定的文件时出现问题。解决方法: 1、文件路径不对,或者文件不存在,找到对应文件放到指定文件下 2、工作目录设置错误,设置工作目录为测试文件所在目录,并且要包含有功能文件和测试文件【问题25】编译include文件时,提示编译的错误  答: 一般include所用的文件,不是一个完整的module代码,它只是一个代码片段。其他代码通过include的方式,将这段代码复制到此处。 既然不是一个完整的module,那么加到工程里编译就肯定会出错。所以这个代码是不用添加到工程里的,只要把它放在正确的路径上就可以了。 所以解决办法是:从工程中,找到此文件,然后remove掉。【问题26】仿真时,提示如:port "clock"not found in the connected module(8th connection) 答:该提示是说,例化代码时(上面提示前会提示哪一行出错),被例化的模块没有“clock”信号。上面是提示的意思,您要根据这个提示去检查,例如打开这个模块代码,看是否有clock信号,以及有没有可能拉写错误等。仔细检查了。

【问题27】我在仿真一段代码。原为两个端口,仿真没有问题,后面增加了两个端口, modelsim提示这两个端口找不到。但我在激励文件中也已经加了这两个端口,不知道是什么原因。

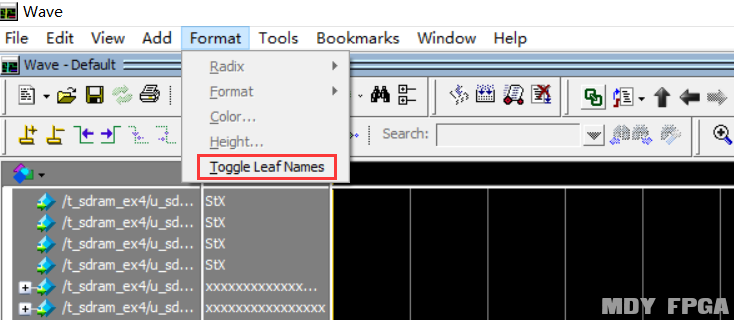

【问题28】每次仿真抓好信号,下次打开工程时,又要重新抓信号,好麻烦, 有没有好办法? 答:使用DO文件可以解决此问题。 具体请看 02 明德扬全网公开课 http://www.mdy-edu.com/wentijieda/20210409/1212.html?1617952925 请看第5部分,高级仿真技巧。【问题29】modelsim仿真中的信号符号名前面的前缀有没有什么地方设置可以取消啊,只显示信号符号  答:方法一:

but other modules do.

答:解决办法如下:

在源程序中添加时间精度,如:`timescale 1 ns/ 1 ps,时间根据自己的情况更改

或者可以使用在vsim指令后加-supress 3009屏蔽该告警。

请学习测试文件编写课程相关内容:03 测试文件的编写

(出处: 明德扬论坛)

【问题31】老师,功能级仿真可以出结果,门级仿真出不来结果,是怎么回事呢? 答:MDY不做门级仿真。如果要做,请按定位问题思路去解决。【问题32】  答:本模块里面又用了本模块作为例化,例如例如tb_tri_assignment这个模块,有一个例化, 例化的模块又是本模块tb_tri_assignment,导致不断循环例化。 【问题33】请问在library中没有我的测试文件test_datain, test_datain是我在桌面直接新建的.v文件,这要怎么解决呢?

答:把仿真工程路径设为测试文件所在路径;或者重新跟着仿真教程做一遍。

答:链接请复制网址打开:https://www.bilibili.com/video/BV11A41147YB?p=5

【问题35】老师请问这个怎么改正呢?  答:测试文件没有输入输出port

【问题36】请问,以前用questa sim创建了一个工程,现在想重新打开那个工程。怎么操作? 答:使用软件打开.mpf格式的文件即可。【问题37】请问如何在modelsim显示频域嘛?做了fft实验。可是是在时域的 答:modelsim只看时序的波形 不涉及频域。

【问题38】关于在仿真软件中计数器提前计数的问题 答:http://www.mdy-edu.com/wentijieda/20210409/1211.html?1617954132

【问题39】.VT和.V有什么区别了 答:没有什么区别,就是后缀不同。

1. 注意区分你安装的MODELSIM版本,是MODESLIM-ALTERA,还是MODELSIM。 2. 注意路径要设置正确,不要有中文或特殊字符。 3. 多尝试 【问题41】加载时,出现如下错误

答:大概率是软件破解或者是软件版本问题。建议重新安装modelsim, 并且安装如下版本:http://www.mdy-edu.com/wentijieda/20210409/1214.html 【问题42】编译后,出现黄色的勾勾,是什么来的?必须解决吗?  答:MODELSIM对源代码进行编译后产生的“警告信息”。 警告信息有可能对功能产生影响,也有可能没有影响。所以要阅读“警告信息”。在“Transcript”窗口中,有LOG信息,双击警告的信息就可以看详细了(与Error信号类似)。 【问题43】在仿真的时候,出现“半个时钟周期”信号是怎么回事?如下图。

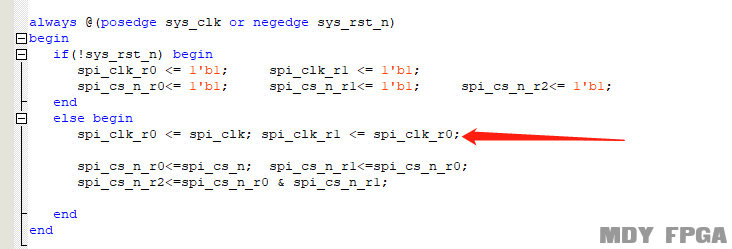

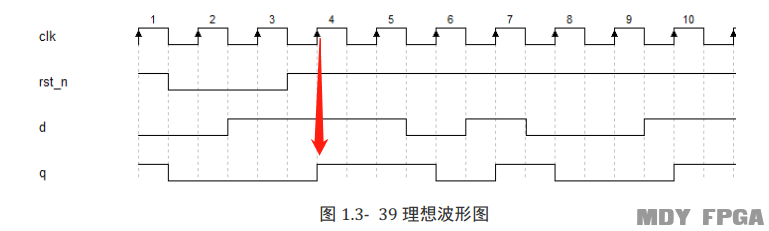

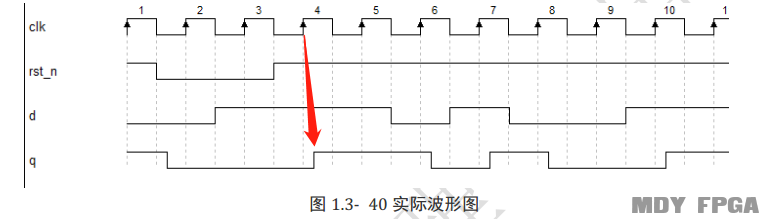

答:FPGA在做功能仿真的时候,通常是如下理想的波形:数据变化和时钟上升沿是对齐的。  上面是理想的波形。但实际上,FPGA是硬件电路来的,信号是在时钟上升沿的触发下变化的, 即先有时钟上升沿,再有信号的变化。信号的变化,是稍微延迟于时钟的。因此更实际一点的波形如下图。  我们编写测试文件的时候,是模拟数字电路的情况,因此在给激励的时候,就应该模拟上图那样给信号, 比较理想的情况,是信号稍微延迟于时钟上升沿一点点,例如延迟1个单位:#1。 (这个时候时钟波形就是“1个周期-1ns”,总之不是一个完整时钟周期) 但是很多情况下,有没有必要延迟上升沿一点点呢?延时多一点点(例如改为#5)也无所谓嘛, 这个时候波形就像是“1个周期-5ns”(也不是一个完整周期)。反正你看代码的时候, 只看时钟上升沿有效的时刻就可以了。 如果你有强迫症,那您就把那个#5改为#1, 甚至改为#0.01都行,越小,越像是一个完整的周期。 BY THE WAY,其实纠结于上面问题,最根本原因,是“凭感觉来做设计”, 因为觉得“看起来不是一个完整周期”(差5ns和差1ns其实都不是一个完整周期)。 其实只要做过仿真,对着代码和波形多对比,是很容易找到问题所在的。 |

【问题44】安装modelsim的时候,安装不成功(如卡在某界面;双击modelsim没有反应等)

答:1. 要安装之前,记得要关闭杀毒软件(最好就是卸载掉,现在WIN10系统都不需要杀毒软件啦)

2.如果第1步还是有问题,建议换其他版本的MODELSIM,例如questasim,用法是完成一样的。

下载地址:http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=430

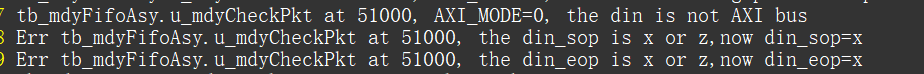

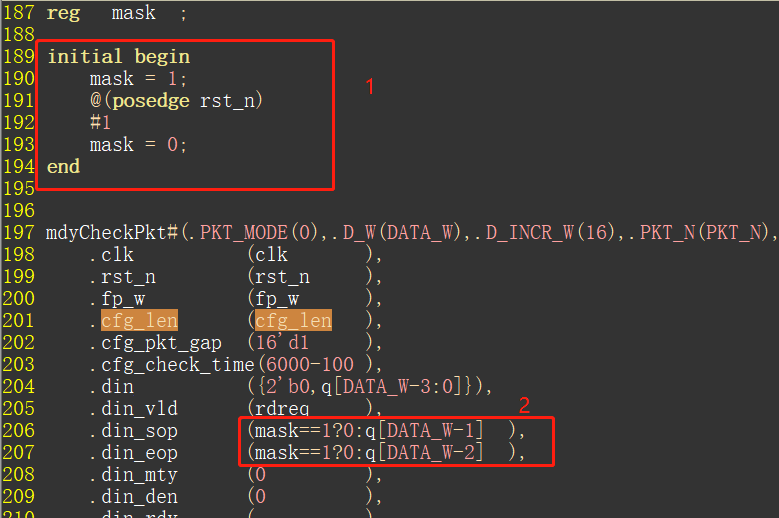

【问题45】MDY的仿真,test_log报告出现如下错误:the din_sop is x or z,new din_sop=x

答:上面提示中测试文件为tb_mdyFifoAsy的模块u_mdyCheckPkt报错,并且是该模块中的信号din_sop和din_eop有错。时间点是在51000这个时刻。

定位思路是:查看mdyCheckPkt的波形,检查在这个时刻下din_sop和din_eop是否为x或者z态。

如果是,就要解决它。问题的根源:MDY的mdyCheckPkt模块要求输入信号,din_sop和din_eop在复位撤消的时刻必须为0,不能为其他。

这就意味着例化mdyCheckPkt时这些信号必须连上,不能空着。如果这个sop和eop为某个IP核的输出,并且为x态是正常的,那么可以屏蔽此项的检查,

其思路是产生一个屏蔽信号mask,屏蔽时刻为1,非屏蔽时刻为0,如下图中的1所示。然后在例化时,din_sop在屏蔽时刻为0,其他时刻正常即可,如下图中的2。

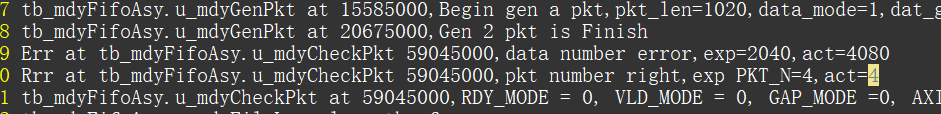

【问题46】MDY仿真中,出现如下错误:data number error, exp=2040,act=4080

答:上面提示中测试文件为tb_mdyFifoAsy的模块u_mdyCheckPkt报错,时间点是在51000这个时刻。

exp表示预期的意思,act表示实际的意思。即预期收到2040个数据,实际为4080个数据。

思路:首先要检测一下UUT的输出,看输出是否正确,即2040个才是正确的,还是4080个才是正确的。

如果是前者,说明测试文件的预期是对的,那说明设计有错;如果是后者,说明测试文件有问题。

其次,测试文件中哪个地方跟预期数据个数有关?就是mdyCheckPkt中的cfg_len这个输入信号有关,

它表示了每个包文的长度,以16位为1组表示1个包文的长度。具体看mdyCheckPkt的说明。

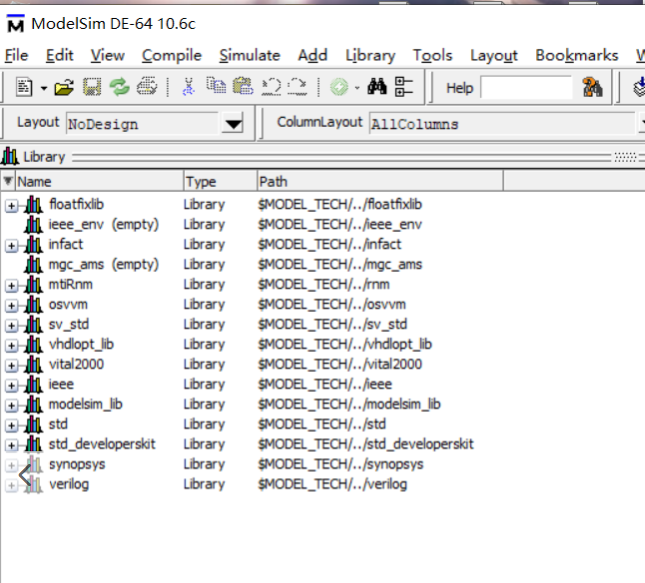

【问题47】 如何确定MODELSIM正确安装并且破解成功了?下图说明安装成功了吗?

答:只要能进入到上面的界面,就说明安装成功了。

【问题48】出现错误:license Issue: Lience request for msimpevsimvlog feature failed

license Issue: cannot checkout an uncounted license within a windows terminal services guest session

答:把LICENES.TXT删除以后,重新进行creck. bat的破解,另存为一个新的LICENES. TXT就行了。即重新破解。

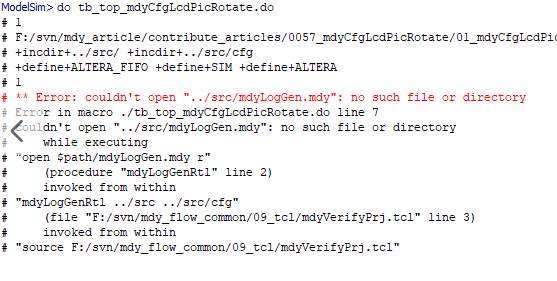

【问题49】 仿真时,提示:couldn't open "../src/mdyLogGen.mdy":no such file or directory

答:mdyLogGen.mdy是MDY专门用于串口调试的功能。

如果您不清楚,可以将此功能关闭,关闭方法,在DO文件的最上面,添加如下代码: set LOGGEN_EN 0

如果您确实要用到此功能,那么应该在sr目录下,添加一个mdyLogGen.mdy的文件,并且里面列名要观察的信号。

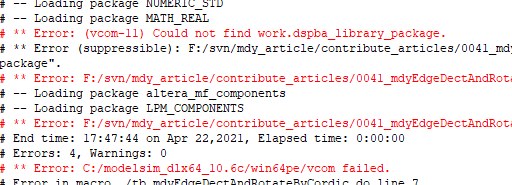

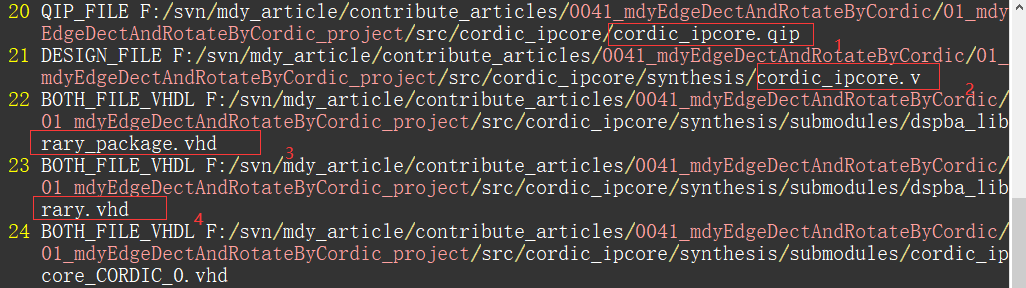

【问题50】Could not find work.dspba_library_package

答:dspba_library_package是VHDL的库文件。假如这个是IP核生成的文件(在IP核目录能搜索到dspba_library_package),

那么就应将该文件添加到仿真工程,或者MDY 的F文件列表中,如下图。

上图中,20行是IP核生成的QIP文件,是QUARTUS工程要用到的。21~24是IP核设计文件,是MODELSIM要用到的,要像上面那样添加进文件列表。

其中21例化了24,24调用了22和23。要特别注意,22 23 24均是VHDL文件,前面类型为BOTH_FILE_VHDL。由于是24调用了22和23,

那么就必须先编译22和23,再编译24,所以22~24的顺序不能乱,一乱就会提示上面的错误。

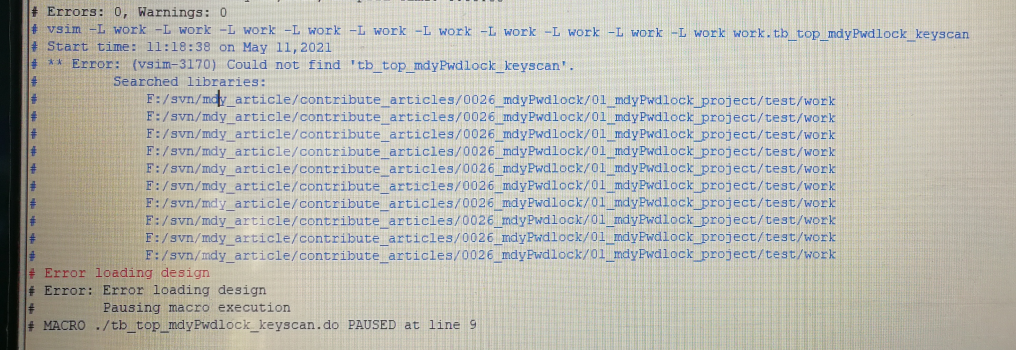

【问题51】在加载时,提示:Could not find "tb_top_mdyPwdlock_keyscan"

答:上面是提示,找不到模块“tb_top_mdyPwdlock_keyscan”。注意,这里是指的是模块名(module 旁边的那个名),而不是文件名。

定位问题思路:看看你的工程里,是不是包含有这个模块名,可能是将此模块添加进本工程,也有可能是模块名写错了,或者是模块名和文件名不同。请仔细核对。

【问题52】请问,在这个上升沿时,检测到en0,理论上应该为0吧?可是我仿真的时候,检测到为1,我仿真的上升沿,检测到en0为1,输出2

答:该问题的解答,请看如下贴子:关于在仿真软件中计数器提前计数的问题: http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=709

【问题53】Unable to checkout a license,使用了非免费版本的Modelsim软件,却没有获得软件使用许可证怎么办?

答:

方法1:使用免费版本的modelsim软件,如modelsim altera stater edition。

方法2:购买软件许可证。

方法3: 破解modelsim软件,破解方法见如下链接(altera收费版和se版本破解思路相同,破解工具通用):

modelsim-win64-10.1c 下载、安装、破解全攻略:http://bbs.elecfans.com/jishu_433057_1_1.html

(出处: 中国电子技术论坛)获得许可后最好重启Quartus II软件

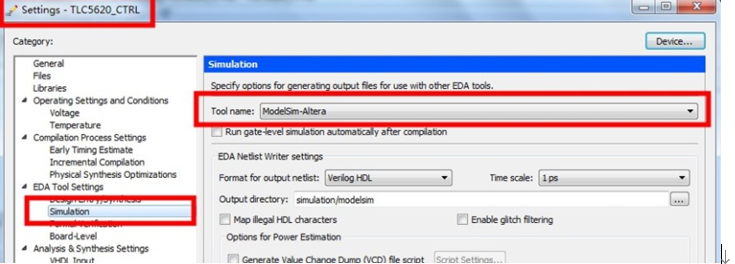

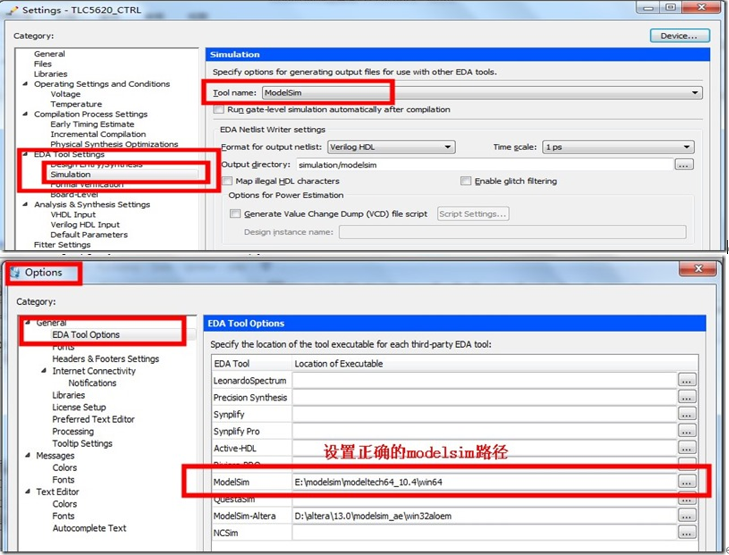

【问题54】 请问该工程设置的仿真工具名称与在Quartus II软件中指定的该软件路径不匹配。例如,本来设置的仿真工具是modelsim–altera,

结果在Quartus II软件的modelsim-altera路径下设定的是Tools下设置的是modelsim-se的路径,导致软件版本不匹配而报错。

设置的仿真工具为modelsim-altera

答:

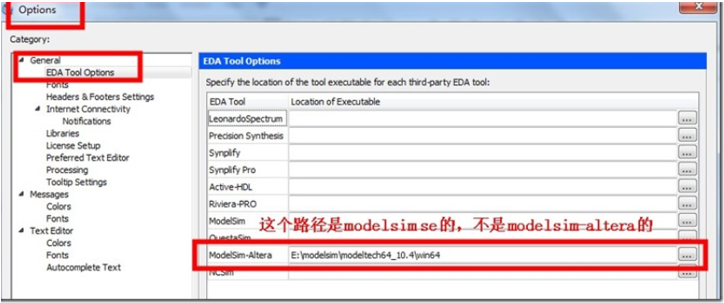

1、 如果你电脑装的是modelsim-se版本,请按照如下图所示的设置进行工程和工具路径设置:

2、 如果你的电脑装的是modelsim-altera版本,请按照如下图所示的设置进行工程和工具路径设置:

[问题55】modelsim altera每一步才100ps。如何把每一步改成20us啊?否则仿真太慢。

答:这个是仿真精度的问题。在所用的代码(包括ip核)通过timescale设置了精度为100ps。为了加快仿真速度,有如下方法。

1.在测试文件中通过timescale来设置精度,例如1ns,可以加快速度。注意,这并不一定有效,因为所使用的其他代码或者ip,精度更好,会用更好精度的。

2.在设计文件中,将时间长的数用参数定义,然后测试文件例化时,修改该参数。例如,有一个计数器要计数10000个,那么可以设定参数NUM=10000来代替,

在测试文件例化时,将参数NUM定义为100(参考参数例化内容)。这样就跑100就可以了。具体可以参考至简原理与应用用数码管案例,有一个实操视频

【问题56】请问 仿真出现了Error: (vsim-3009) [TSCALE] - Module 'muxtwo' does not have a timeunit/timeprecision specification in effect, but other modules do怎么办?

答:将.v文件的内容全部包含进来。

【问题57】使用modelsim时,命令行窗口打印如下,导致仿真无法进行去:

答:删除work目录下的_lock文件,可以删除整个work目录重新执行仿真脚本即可

【问题58】Error: (vsim-3170)如果出现以下错误,原因是仿真的模块名字和编译的文件名字不一致,可能有以下两种错误导致

答:(1)tb的module名和文件名不一致,假设你的tb文件名字是cordic_tb.v

而cordic_tb.v中的module名字和文件名不一致,则会导致报3170错误

(2)do文件中的work module名字写错

错误写法:

1.#VSIM

2.vsim +no_notifier +nospecify +notimingchecks -t 1ps work

3.-novopt cordic_tb.v

正确写法:

1.#VSIM

2.vsim +no_notifier +nospecify +notimingchecks -t 1ps work

3.-novopt cordic_tb

【问题59】仿真运行错误:在rtl_work仿真库下找不到测试文件。

解答:上面是提示,在上面所示的地址之下,没有找到tb_key这个模块。请按此线索查找。例如有没有这个模块,确定模块名和文件名是否对应上。由于本案例不是MDY的案例,不了解该案例,无法提供更多支持。

易老师13112063618(微信同号)

明德扬科技教育

明德扬科技教育