这里有一个视频项目要求将非标准的ITU-R BT.656视频格式的数据转换成VGA格式,直接用于显示器显示。如图1,输入的视频格式是非标准的ITU-R BT.656格式,图像分辨率是1280×1024,帧速是15帧/秒,每一个像素点是24bit;输出的视频格式是VGA格式,图像分辨率是1280× 1024,帧速是60帧/秒,每一个像素点还是24bit。

本项目使用SDRAM来存储视频数据。在设计中,要求能够将一幅完整的图像(1280×1024×24bit)存储在SDRAM中。并且要求读写突发长度是1280,即一行视频数据(1280×24bit)。SDRAM突发长度最高只能达到256(即SDRAM芯片的一列的长度),为此需要使用FPGA专门实现一个SDRAM控制器。在控制器的设计中通过采用切换bank操作、自动预冲、集中刷新等技术实现了这种超长突发长度的数据读写。同样通过适当地修改此控制器,可以实现任意突发长度的数据读写。

1 SDRAM基本特性

本设计中采用的SDRAM芯片的型号是MT48LC2M3282-7。SDRAM的主要操作包括初始化、读写和刷新操作。SDRAM的初始化操作过程如下:上电后等待100 μs;然后依次完成预冲,两次刷新操作;接下来就可以配置寄存器了。至此整个初始化工作结束,SDRAM进入正常工作状态。SDRAM进入正常工作状态后,就可以根据命令来工作。这些命令包括:预冲(Precharge)和自动预冲(AutoPrecharge)、激活(Active)、读 (read)、写(write)、自动刷新(Auto Refresh)和自刷新(Self Refresh)等。根据本设计的需要,这里详细介绍设计中相关的命令:自动预冲、激活、读写、自动刷新。自动预冲命令是SDRAM芯片在一次突发读/写结束后自动发出预冲命令,将读写的行关闭。它与预冲命令有着相同的功能,但是发起命令的方式不一样。预冲命令是SDRAM控制器发起的命令,它需要占据 SDRAM的总线,在这段时间不能读写数据。而自动预冲命令是SDRAM自动的行为,不需要占据SDRAM的总线。这个命令是在发起读写命令时设置的。

激活命令是对SDRAM的某一行激活,这样才能对这一行数据发起读写操作。读写命令是对某一激活的行进行突发读写操作。具体的突发读写的数据长度在初始化时配置寄存器时设置了。

刷新命令是对SDRAM内的数据完成再生的操作,因为SDRAM采用电容存储数据,而电容存在漏电的现象,因此需要隔一段时间对电容作一次刷新(即重新充电),一般来说要求64ms内将SDRAM的所有行都刷一遍。SDRAM有两种刷新命令:自动刷新和自刷新。自刷新是在芯片处于低功耗状态下时才使用的方式,芯片内部自动完成刷新操作。自动刷新是控制器发起的刷新操作,它必须在SDRAM没有激活行时才能进行刷新操作,而且需要占用一定的时间(大约 60~70ns)。控制器可以根据需要选择在何时刷新,即定时刷新,或集中刷新。定时刷新是隔一段时间就刷新一次;集中刷新是在某一段空闲时间内连续刷新若干次。这个只要保证在64 ms内将所有的行都刷一遍即可,具体的刷新方式可以根据自己的应用需要来设计。

2 SDRAM控制器的设计

2.1 SDRAM控制器的设计思路

SDRAM芯片完成一次读写操作由三个命令组成:激活、读/写、预冲。读写数据的突发长度往往是有限制的,在SDRAM芯片本身提供的突发长度最大只能达到一行的容量(256,即全页突发模式)。这样当一次读写突发长度结束后,如果需要发起下一次读写,就需要发预冲命令结束这一行,然后发激活命令开启下一行。这样才能开始写下一次数据。因此,如果想要连续的数据读写,就必须想办法节省激活和预冲命令。

激活命令通过切换Bank操作来完成。SDRAM有4个独立的bank,每一个bank可以同时允许有一行激活,彼此并不会相互干扰。这样的话,在同一时刻最多可以有4个行处于激活状态。这就为节约激活时间提供了解决方案:在突发读写一个bank下的某一行时,可以在突发长度结束之前提前激活另一个 bank下的某一行。这样当这个突发长度结束时就可以直接读写另一bank中被激活的行。预冲可以采用自动预冲方式来完成,不需要额外的预冲命令。

通过上述两种操作方式可以完全实现超长突发长度的数据读写,本设计将SDRAM设置成突发长度为8,突发长度结束后采用自动预冲方式完成此行的预冲操作,具体设想如下:

在写SDRAM时,先激活Bank0的第一行;发出带自动预冲模式的写操作;数据开始写入这一行内;一段时间后(在突发长度结束之前)将Bank1的第一行激活;在Bank0的写突发长度结束的同时,发出写Bank1的命令,这样接下来的数据就写入Bank1的第一行中;而由于在写SDRAM的Bank0 时设置成自动预冲模式,所以SDRAM会在Bank0的写操作结束后自动预冲,经过tRP(预冲时间)后,这一Bank自动回到idle状态。同样 Bank1处于写突发长度时将Bank2的第一行激活,在Bank1的写突发长度结束的同时发出写Bank2的命令……如此四个bank轮流工作,将数据均匀地分配到4个bank中。

对于这种超长的数据突发读写,完成一次读写操作所花费的时间比较多,例如读写时钟是108MHz时,一次突发长度是1280的写操作所花费的时间是11. 6 μs,即在这段时间内SDRAM的数据总线是不能被中断的。因此采用集中刷新是最好的解决办法。在突发读写结束后,会有一段比较长的空闲期(具体时间长度根据视频数据的视频中行消隐数据个数和读写时钟决定),在这段时问内可以集中连续发出多个刷新命令,只需要保证在64ms内总的刷新次数达到了要求即可。

2.2 SDRAM控制器的实现

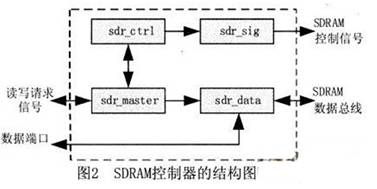

本设计中将SDRAM控制器分成4个子模块:sdr_master主控模块、sdr_ctrl命令模块、sdr_sig译码模块、sdr_data数据通路模块,见图2。sdr_master主控模块根据外部的读写请求向sdr_ctrl命令模块提供各种读写控制信号;sdr_ctrl命令模块内部的控制状态机会依此发出各种SDRAM读写控制命令;sdr_sig译码模块会把sdr_ctrl输出的控制命令译码成符合SDRAM接口的信号。此SDRAM 控制器的设计,最复杂的部分在于如何设计SDRAM的工作时序,即SDRAM何时激活,何时读/写,何时预冲,何时刷新。这些控制除了满足SDRAM的工作特性外,还要满足设计要求。因此,鉴于SDRAM控制的复杂性,一般都采用状态机来控制。本设计中sdr_ctrl命令模块包括两个状态机:初始化状态机完成SDRAM的初始化;控制状态机完成SDRAM的正常工作控制。下面分别详述这两个状态机的设计。

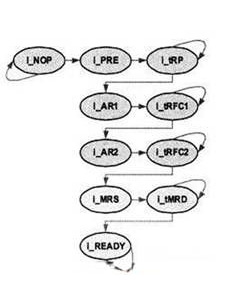

初始化状态机的结构见下图。系统在上电(复位)后,处于i NOP状态;当等待了100 μs后,状态跳转到i PRE,发出预冲命令;接着跳转到i tRP等待;经过tRP时间后,状态跳转到i_AR1,发第一次刷新命令,然后在i_tRFC1等待tRFC时间后发第二次刷新命令,再等待tRFC;接下来转到状态i MRS,发装载模式字命令,然后等待tMRD时间后初始化完成,进入i_ready状态。至此初始化完成,SDRAM芯片就可以正常工作了。

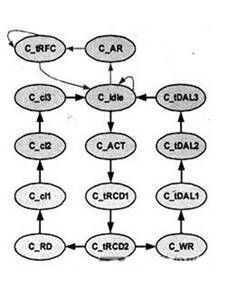

控制状态机的状态跳变如下图所示。此状态机是为了满足超长数据的连读或连写而特殊设计的。上电后处于c_idle状态,当初始化完成后,控制状态机才能开始正常工作。当外部要求进行读写操作时,会正式地启动状态机。此时状态机跳变到c_ACT状态,使SDRAM控制器发出激活命令;接下来两个状态 c_tRCD1、c_tRCD2是激活等待时间tRCD;然后状态机根据外部是读请求还是写请求,来决定下一个状态是发读命令还是写命令。下面以写数据为例进行说明,读数据的工作过程是一样的。

当要求写SDRAM时,控制状态机的状态由c_tRCD2跳变到c_WR状态,发出写命令。SDRAM控制器会在发写命令的同时将本次突发数据的第一个数据送到总线上,接着是三个周期的状态:c_tDAL1、c_DAL2、c_tDAL3,之后回到c_idle状态。这样完成了写数据的一次循环,刚好需要 8个周期。在回到c_idle状态后即可启动下一次写数据传输,这时状态机跳到c_ACT状态,发出激活另一个bank的某一行的命令,然后经过两个周期后,此时上一次写操作的数据突发长度刚好结束。下一个周期状态变成c_WR,发下一次的写命令,同时将这一次突发长度的第一个数据放到SDRAM数据总线上……如此循环,可以完成长度是1280的连续数据的写入。这个循环如何结束呢?当发了最后一个突发写命令后,状态机回到c_idle时,即可停止循环,不再进入激活状态。总之通过控制这个状态机可以完成长度是8的倍数的连续数据读写。控制状态机还有实现刷新操作的功能,当要求对SDRAM进行刷新操作时,控制状态机的状态会跳变到c_AR,SDRAM控制器会依此发出刷新命令。然后状态机跳变到c_tRFC状态等待刷新操作的结束。当刷新操作结束后,状态机将恢复到c_idle。这样就完成了一次刷新操作。如果需要多次刷新,就可以连续进行多次这样的循环。

2.3 SDRAM控制器的综合

本设计使用的SDRAM芯片是MT48LC2M3282,FPGA芯片是cyclone的EP1C6Q240C6。综合工具是QuartusII 6.0。综合的结果是逻辑单元使用了170个,占总资源的3%;工作频率最高可以达到240.10 MHz,满足项目要求。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8. 射频前端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

点击了解项目承接业务详情☝

需要了解相关信息可以联系:吴老师18022857217(微信同号)