FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点

FPGA芯片结构

FPGA芯片主要由三部分组成,分别是IOE(input output element,输入输出单元)、LAB(logic array block,逻辑阵列块,对于Xilinx称之为可配置逻辑块CLB)和Interconnect(内部连接线)。

IOE

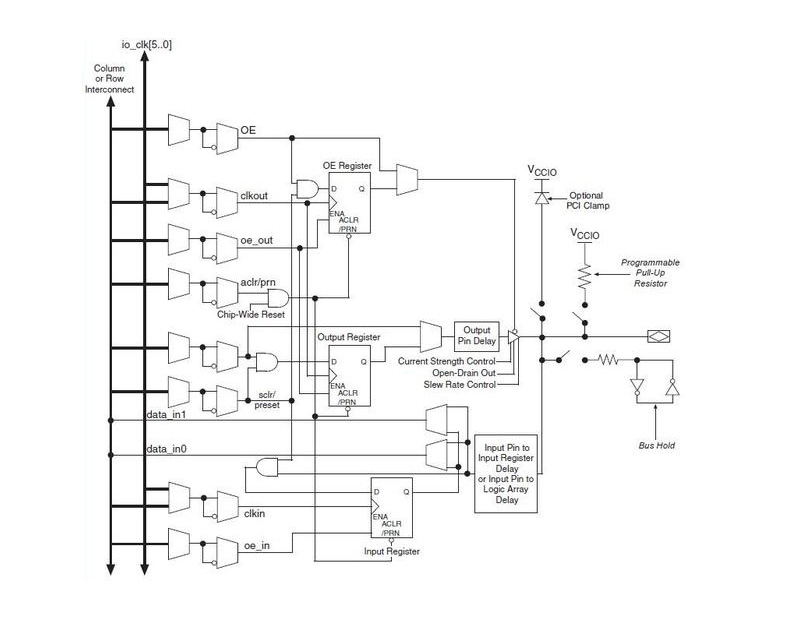

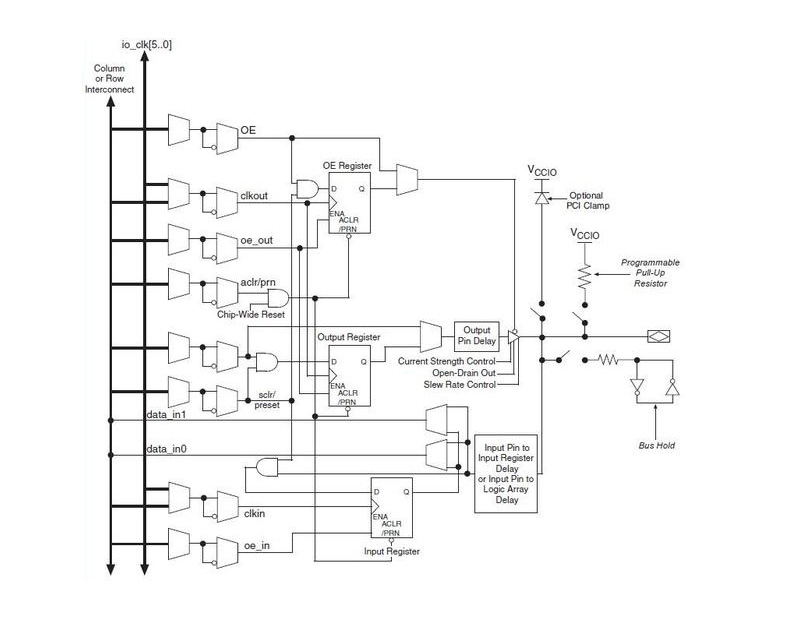

IOE是芯片与外部电路的物理接口,主要完成不同电气特性下输入/输出信号的驱动与匹配要求,比如从基本的LVTTL/LVCMOS接口到PCI/LVDS/RSDS甚至各种各样的差分接口,从5V兼容到3.3V/2.5V/1.8V/1.5V的电平接口,下面是ALTERA公司的Cyclone IV EP4CE115F29设备的IOE结构

EP4CE115F29设备的IOE结构图

LAB

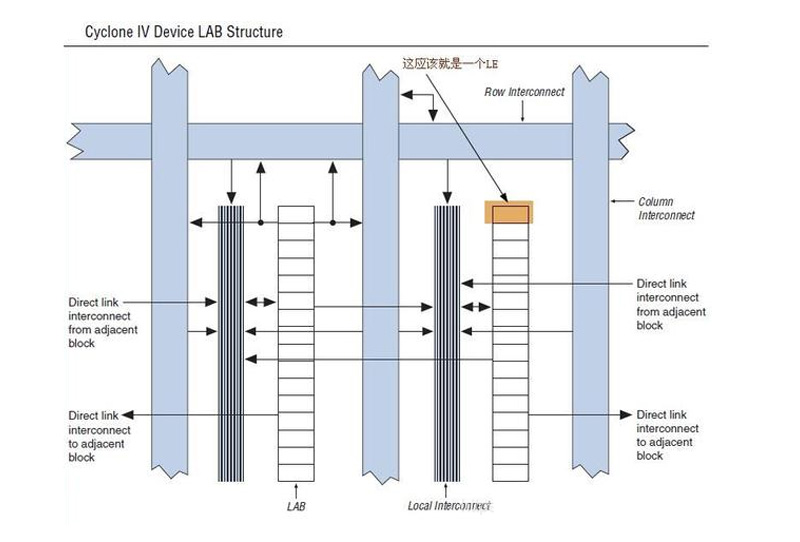

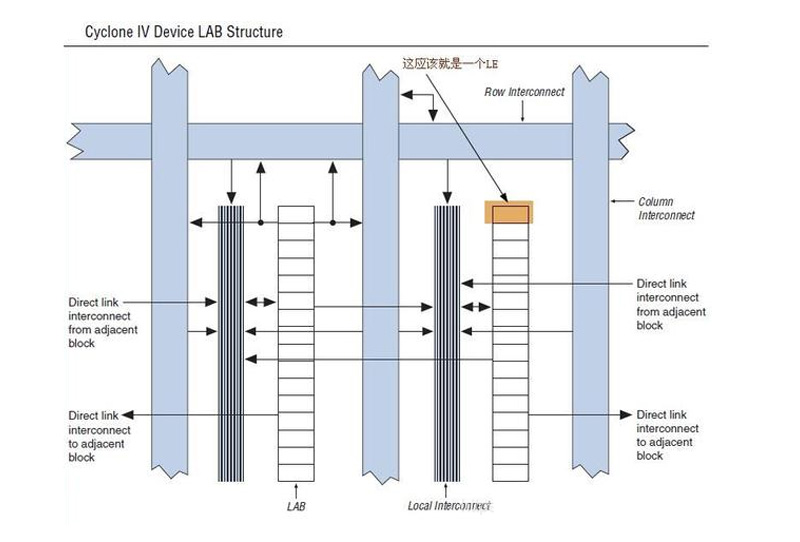

LAB是FPGA的基本逻辑单元,其实际的数量和特性依据所采用的器件的不同而不同,EP4CE115F29设备的每个LAB的布局包括16个LE、LAB控制信号、LE carry chains、Register chains和Local interconnect,其LAB结构图如下:

LAB结构图

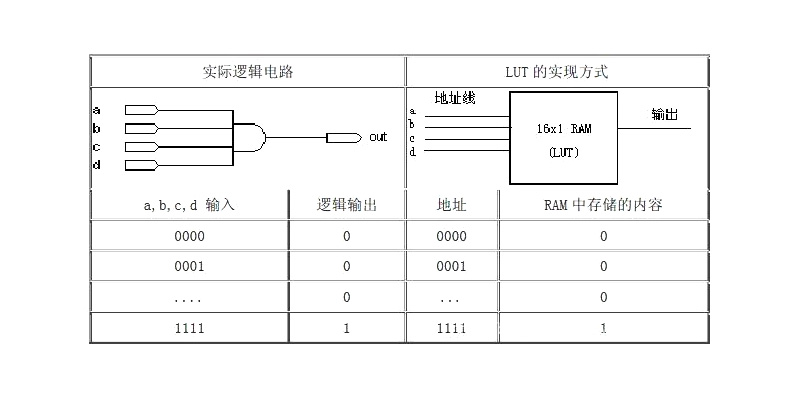

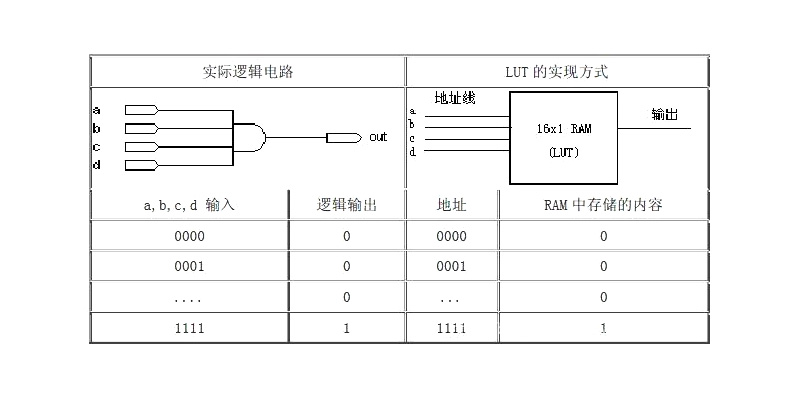

查找表LUT(Look-Up-Table)其本质是一个静态存储器SRAM,目前FPGA多采用4输入的LUT,每个LUT可以看作一个有4位地址线的16x1的RAM。当我们通过原理图或HDL语言描述了一个逻辑电路后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,在FPGA工作时,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

LUT的实现原理图

Interconnect

FPGA内部连接线很丰富,根据数据手册的描述,主要有图3中的Row interconnect、column interconnect、Direct link interconnect、和Local interconnect和Register chain interconnect(寄存器之间连接的连接线)。

内部连接线联通FPGA内部的所有单元,而连线的长度和工艺决定着信号再连接线上的驱动能力和传输速度。在实际开发中,设计者不需要直接选择连接线,布局布线器可自动地根据输入逻辑网表(这由综合生成)的拓扑结构和约束条件选择连接线来连通各个逻辑单元,所以,从本质上来说,布线资源的使用方法和设计的结果有密切和直接、直接的关系。

FPGA工作原理

FPGA的内部结构主要包含可配置的逻辑块(CLB)、输入输出块、布线资源和可编程开关。其中可配置的控制块是FPGA的主要资源指标,在芯片内部以二维阵列的形式排布。在CLB中包含查找表和D触发器,查找表(LUT)负责给芯片提供组合逻辑,D触发器负责提供时序逻辑,为设计数字电子系统提供资源。其中的查找表是一个16*1的RAM,具有RAM的物理结构,但是在作用上是类似ROM,负责存储Quartus II综合生成的逻辑电路的各种可能的运行结果,在FPGA工作的时候,依据端口输入的数据流或者是逻辑流,在RAM中取出对应的数字逻辑运算,配合D触发器可以完成数字电子系统需要的组合逻辑和时序逻辑。设计者在进行软件设计的时候,依据设计目标,将电路功能以代码的形式描述出来,Quartus II负责对代买进行编译和综合,得到设计电路的各种可能结果,下载到FPGA的时候,这些数据都存储在CLB的查找表中。系统开始工作时,在数据流或者是逻辑流的驱动下,在查找表中取出对应的数字逻辑,然后和D触发器配合完成数字电子系统的组合逻辑设计和时序逻辑设计。

温馨提示:明德扬2023推出了全新课程——

逻辑设计基本功修炼课,降低学习FPGA门槛的同时,增加了学习的趣味性

http://old.mdy-edu.com/chanpinzhongxin/peixunkecheng/2023/0215/1889.html

(点击→了解课程详情☝)

明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8. 射频前端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(点击→了解项目承接业务详情☝)

需要了解相关信息可以联系:江老师18022859964(微信同号)