编写测试文件的时候,要严格模拟真实的外设情况设计激励吗?

2023-04-13 人气: 作者:wuqi

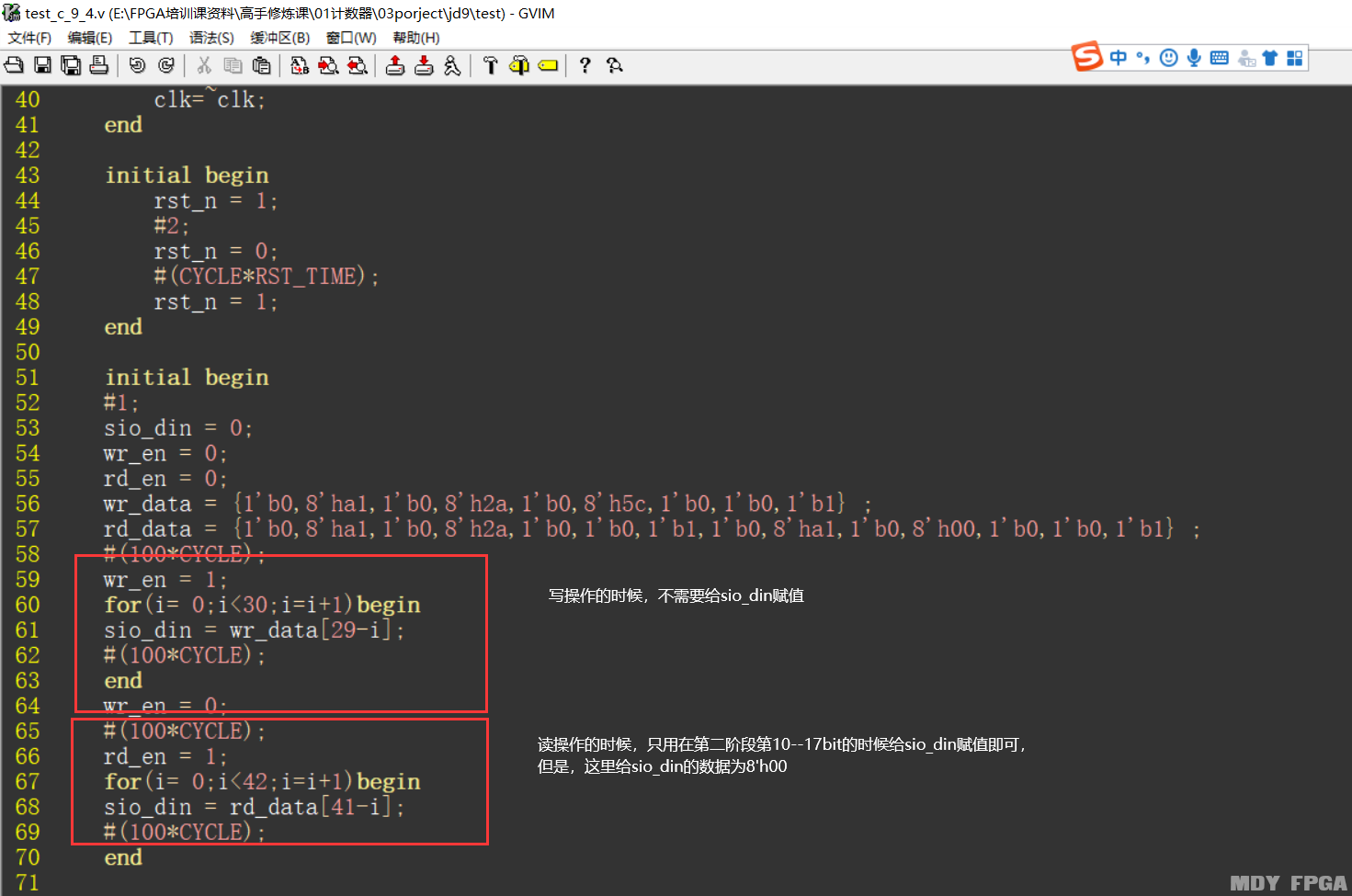

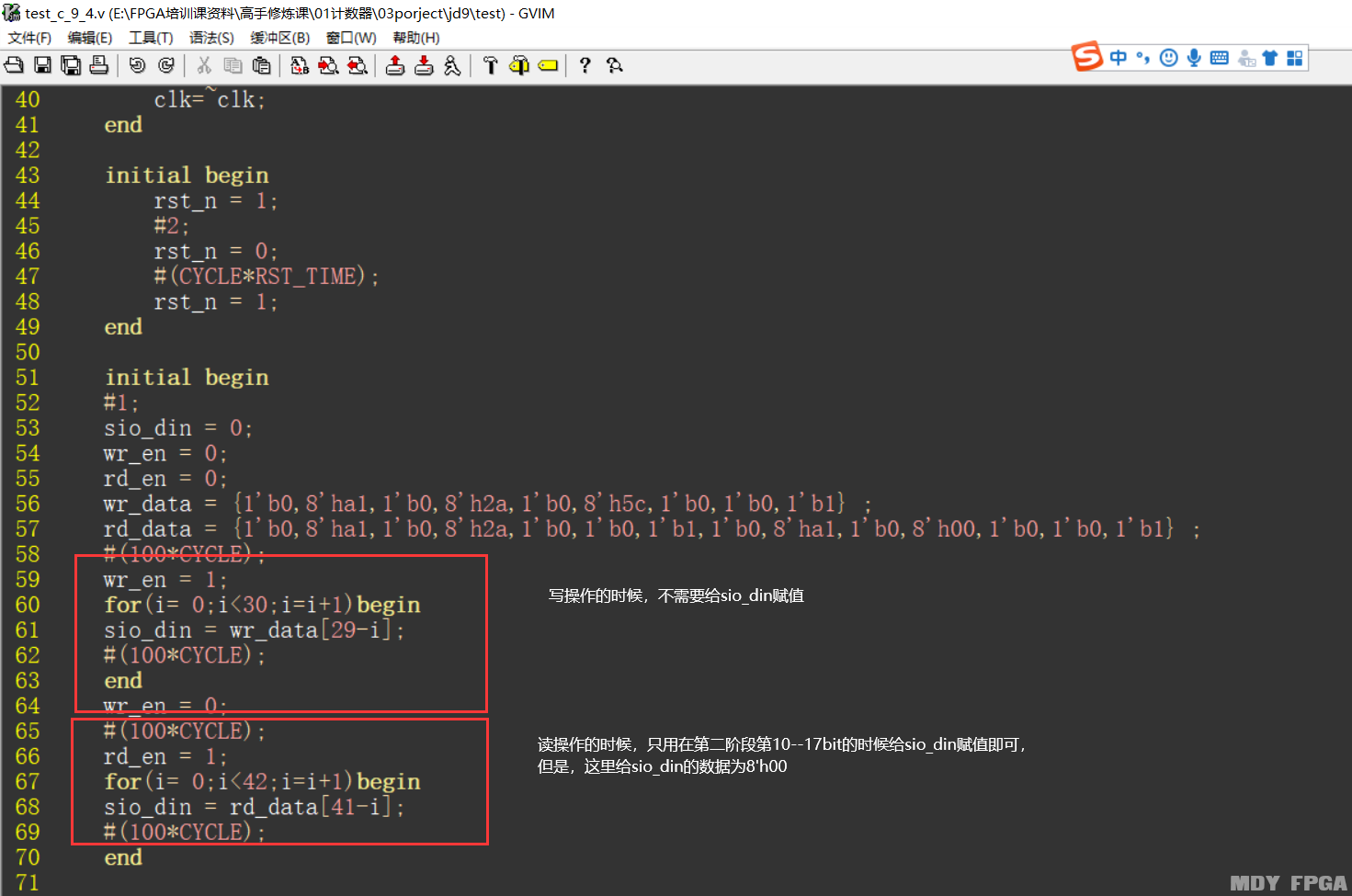

编写测试文件的时候,要严格模拟真实的外设情况设计激励吗?例如说,外设输出信号dout,按照时序要求是每1us变化一次,是不是意味着仿真时也要这样做?或者是下面图片的例子

答:通常来说,一般测试文件会模拟外设的情况,来设计这个激励。 但如果遇到设计复杂,评估没有必要的情况,也会简化仿真。

例如上图中的问题,按照时序图要求,sio_din不用“赋值”。但问题是,“不用赋值”和给“0”,到底有什么不同?我们更关心的是,设计代码不要在此期间get这个值就好了。

也就是说,这一段区域,是大家都不关心的,就没有必要去设计得复杂。

还有一个例子:dout每1us变化一次,这是真实情况。但我在编写文件时,每个时钟都给不同的值,然后确认在我需要的时候,能不能获得到当前值,这样更能保证设计要求。

其实,总结一点的是:我们不关心仿真文件激励做得“不够好”。我们更关心的是,在此时此种激励下,我们的设计代码对不对。这才是核心!

答:通常来说,一般测试文件会模拟外设的情况,来设计这个激励。 但如果遇到设计复杂,评估没有必要的情况,也会简化仿真。

例如上图中的问题,按照时序图要求,sio_din不用“赋值”。但问题是,“不用赋值”和给“0”,到底有什么不同?我们更关心的是,设计代码不要在此期间get这个值就好了。

也就是说,这一段区域,是大家都不关心的,就没有必要去设计得复杂。

还有一个例子:dout每1us变化一次,这是真实情况。但我在编写文件时,每个时钟都给不同的值,然后确认在我需要的时候,能不能获得到当前值,这样更能保证设计要求。

其实,总结一点的是:我们不关心仿真文件激励做得“不够好”。我们更关心的是,在此时此种激励下,我们的设计代码对不对。这才是核心!

上一篇:时钟为什么是红色的,没有变化?