计数器是FPGA最常用的功能器件,每个模块几乎都会用到,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。应用场合也是非常广泛,通过计数得到时间;计算多少数据;简单的状态机等。本次明德扬视频点拔课主要是讲述计数器使用的方法和规范,给出了自增和自减两个例子,这也是明德扬至简设计的规范设计,多年的实践证明,这种设计规范是可以用于任何场景的。

计数器的规范使用,可以极少地精简代码。至简设计的规范主要有以下几点:

1、初始值是多少

a、复位值

b、每轮计数的初始值

2. 加1条件是什么

3. 结束条件

a、即结束本轮计数的条件

b、一般又是加1条件,不要特地为结束而多统计一个数

c、记得要变回初始值

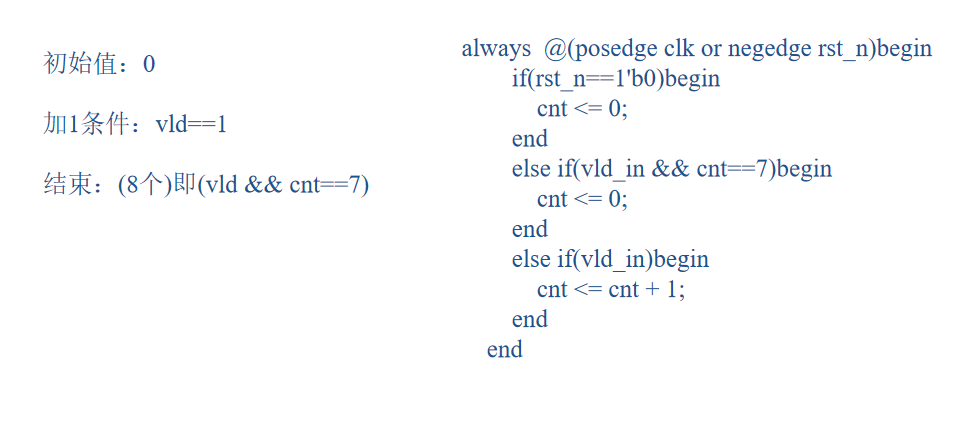

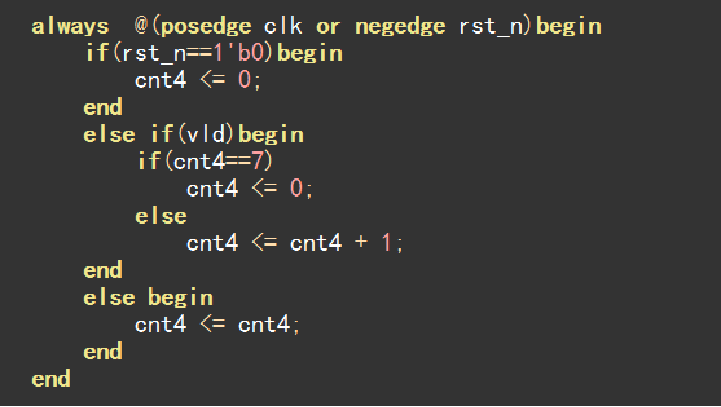

对vld=1进行统计,统计到8个后,重新再计数

注意:这里为什么只记数到COUNT_1S-1(就是4999_9999)呢?

因为计数器是从0开始计数的,从0变到1就已经计数一次了,因此计500_0000个数只需要从0计到4999_9999就行了

注意:counter的位宽

计数器的使用规范有以下几个法则:

1、用于统计计数的,建议用自增计数器

2、用于不定时计数的(即每轮计数多少个不定),建议用自减计数器

3、计数器一般从0开始计数,不要从非0开始。这样有助于检查计数器是否正确,也便于他人理解。

4、选好结束数,不要多计一个数来做结束。例如需要计10个数,则从0计数到9即可,结束数是9而不是10。

5、位宽应合理。位宽要能保证可以容纳得下计数器可以达到的最大的数,例如,计到6最少需要3位的位宽,而计到10就需要4位位宽了。

6、计数时,特别注意0是否要统计在内。

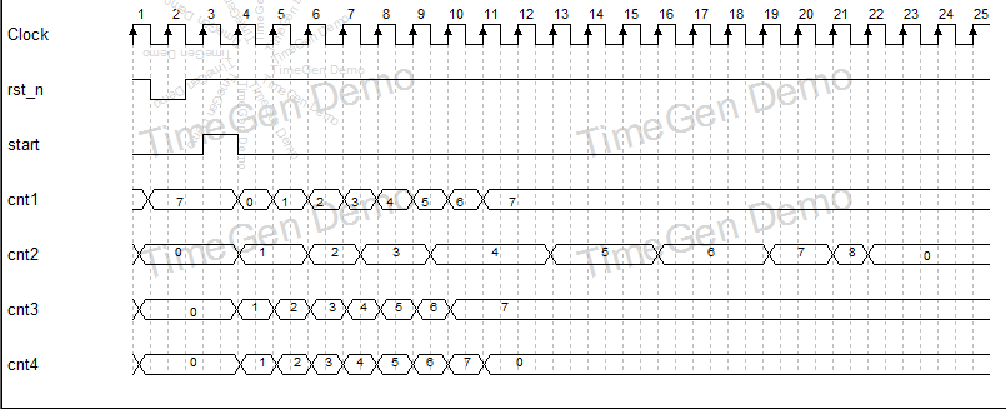

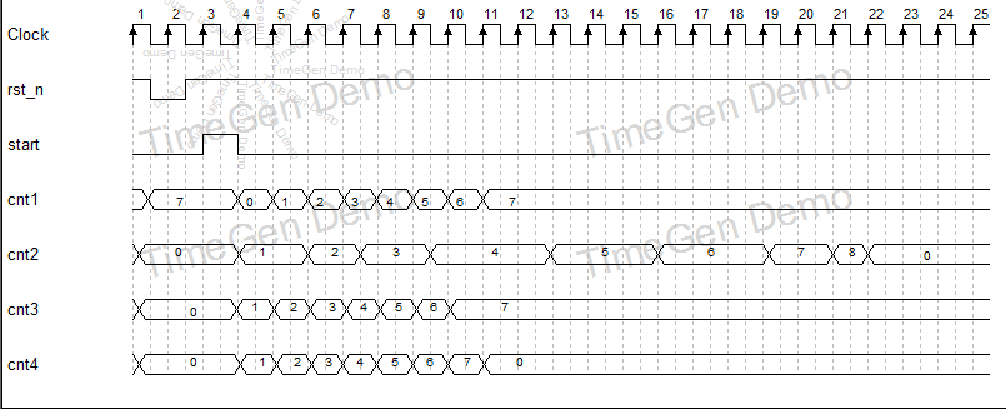

下面以四个计数器案例说明至简设计规范:

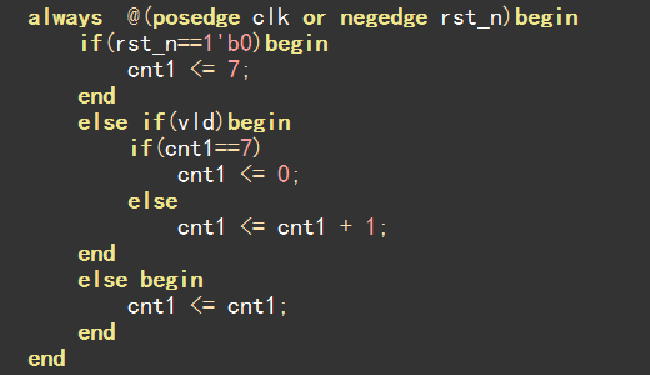

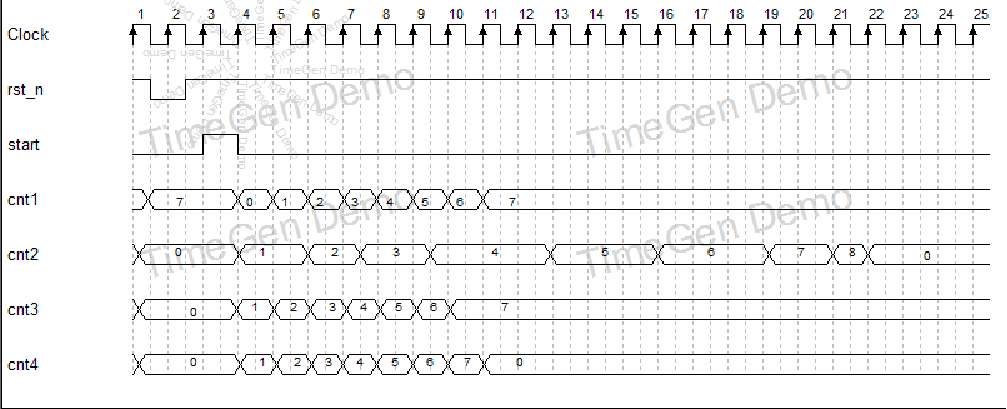

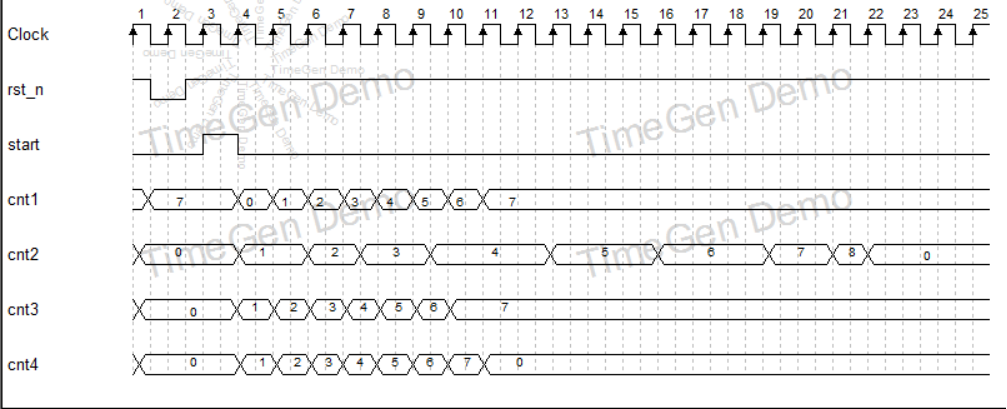

分析cnt1:

计数器复位后是7,也就是从7开始计数,7再变到0,这个很不符合我们的正常习惯,也不利于后面的检查和波形对比,应坚决避免此种情况出现。

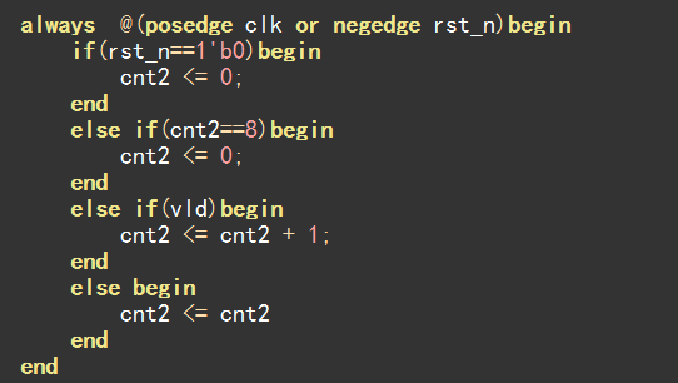

分析cnt2,cnt2要统计8个数据(即要计到7)

分析cnt2,cnt2要统计8个数据(即要计到7)

该实现方案中,计数由0~7已经实现了统计8个,但结束条件为8,多浪费了一个时钟。

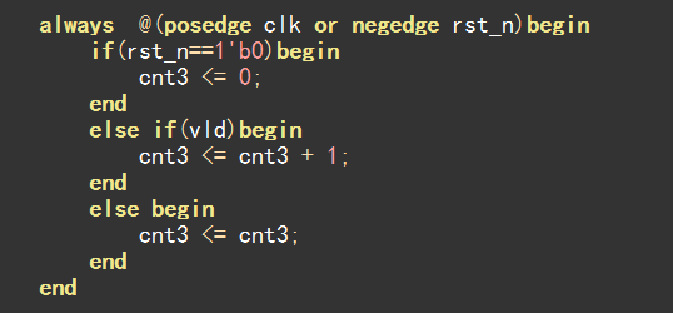

分析cnt3

计数器计数满后维持在7不会自动跳变为0;

这也是不应该出现的。计数器在计数满后应自动能变为0,这样才能实现循环

计数。

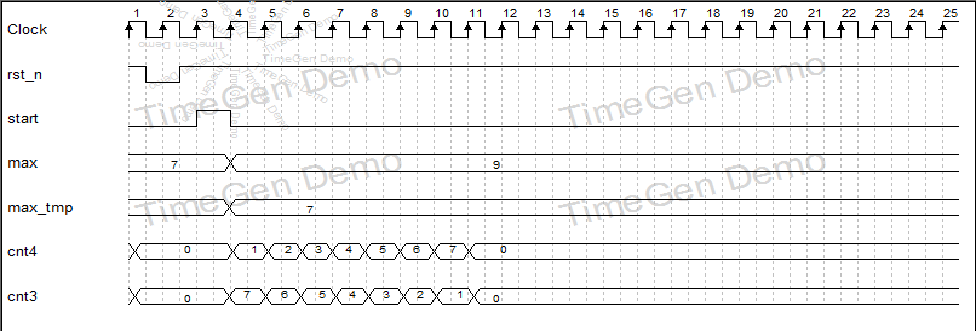

计数器cnt4,这个是正确的计数器的时序图。大家可以作为标准,与上面几个比较一下,看看有有什么不同,慢慢理解一下。重点注意结束数和开始数这些。

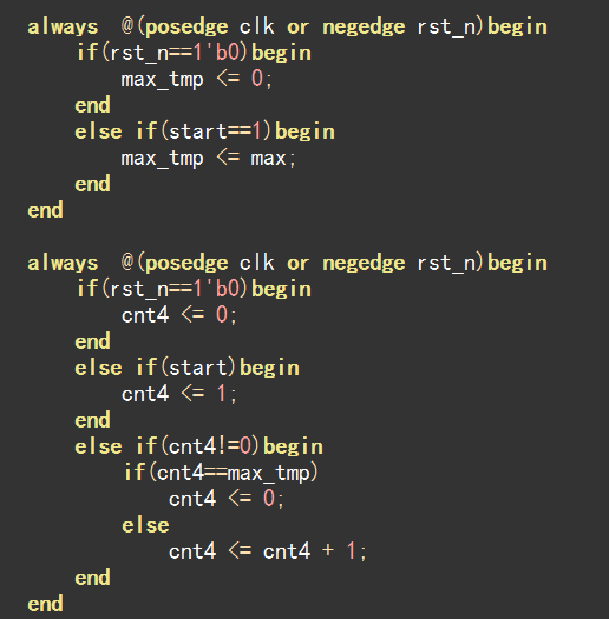

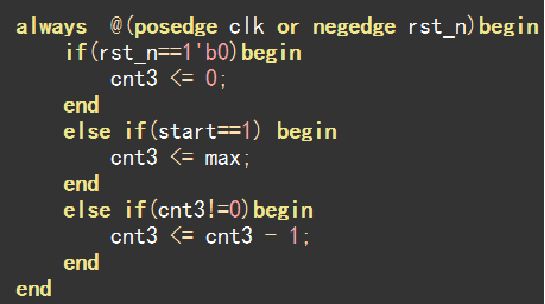

自减计数器的使用

cnt4要多用一个寄存器max_tmp进行保存

cnt3直接用max的值

用于不定时计数的(即每轮计数多少个不定),建议用自减计数器

明德扬本次课程主要讲述了计数器的使用的方法和规范,给出了自增和自减的两个例子,请一定要按这两个规范设计。多年实践证明,是可以用于任何场景下的。.本次课程后面配有十几个计数器练习如需视频以及练习题和答案,请联系客服人员李老师19928348709(微信同号)