已更新27个笔试面试题 还未完结,本次更新日期2017年10月12日,连载更新。 。 。

别人连载小说,我们连载FPGA/集成电路笔试面试题解答视频!

一点一滴的积累,坚持获得成绩!

明德扬潘老师历经多年精心整理历年各大公司(如海华、大彊、中兴、展讯等名企)笔试面试题,每道题都有已录制好的详细的解答视频 + 举一反三的解题技巧。届时我们将不断地更新和补充最新的笔试面试题(解答视频),欢迎大家加QQ2122516396联系老师领取。明德扬FPGA技术交流群:97925396

(面试题答案完整视频系列咨询官网客服即可)

1. Write a sequence of 3-bit grey code. Can you derive a general equation to convert binary to grey code? [AMD 2008]

【解答视频序号:08310001】

2. 怎样将一个single-bit信号从快时钟域送到慢时钟域,或慢送到快?Multi-bit信号呢?[AMD 2008]

【解答视频序号:08310002】

3. 设计一个计算连续Leading Zeros个数的电路。输入8-bit,输出4-bit。[AMD 2008]

00001000 0100

00100010 0010

10001000 0000

可以parameterize你的设计吗?其hardware是什么样子的?

【解答视频序号:09090001】

4. 出下面两个状态机的逻辑综合图,并说明两种写法的优缺点![凹凸 2008]

always @(posedge clk or negedge rst)

if(!rst)begin

state<=0;

out<=4'b0000;

end

else

case(state)

0:begin

state<=1;

out<=4'b0000;

end

1:begin

state<=0;

out<=4'b0001;

end

endcase

always @(posedge clk or negedge rst)

if(!rst)

state<=0;

else

case(state)

0:state<=1;

1:state<=0;

endcase

always@(state)

if(!state)

out=4'b0000;

else

out=4'b0001;

前者state 和out[0]分别综合成两个触发器,其中state触发器的输入为它本身的反向。out[0]的触发器为state的当前输入。后者只有state一个触发器,输出直接赋值给out[0],光靠这两段看不出它到底要考啥,估计可能是想考状态机1段,2段,3段式的优缺点。

第一个out要综合成四位的寄存器,占用资源;

第二个则比较节约了 呵呵

2段和1段相比,没有节省资源吧,还多用了寄存器了。

不过肯定是提高了程序代码的可读性和维护性我觉得这两段的输出加一步寄存会好一些,可以减少逻辑电路带来的毛刺 吴继华,王城编的《verilog设计和验证》有一章对这个讲得很详细你可以到论坛里面去找找,好像是有电子版

第一段代码速度上比较快,但所占资源多;第二段正好相反,只用了一个寄存器,但Timing会差点。所谓可读性,我觉得在这里没什么区别,关键还是硬件实现上的区别。

我的观点是:二段式的状态机将组合逻辑和时序逻辑分离开,便于综合工具进行分析。ls各位说的,只是基于这两个例子但是题目是关于状态机的写法的优缺点这是我的观点。

【解答视频序号:09090002】

5. 设计地址生成器。[nVidia 2008]

要求依次输出以下序列:

0,8,2,10,4,12,6,14,1,9,3,11,5,13,7,15,

16,24,18,26,.................................,31,

32,40,34,42,.................................,47,

48,56,50,58,.................................,63,

64,72,66,76,.................................,79

【解答视频序号:09090003】

6. 假设存在positive clock skew为10ns,问最高电路频率。[SIRF 2008]

能容忍的最大positive clock skew

能容忍的最大negative clock skew

positive clock skew:DFF2的clock比DFF1的来的晚

negative clock skew:DFF2的clock比DFF1的来的早

Tsetup=1ns Thold=1ns Tclk->q=1ns

【解答视频序号:09090004】

7. 阻塞赋值和非阻塞赋值的区别 [Trident]

always@(posedge clk) always@(posedge clk)

begin begin

b=a; b<=a;

c=b; c<=b;

end end

上面两段代码的硬件结构是怎么样的?

【解答视频序号:09090005】

8. 化简代码使硬件尽可能少 [Trident]

always@ (sel or a or b or c)

if(sel)

y = a + b;

else

y = a + c;

【解答视频序号:09090006】

9. 2进制的1101.101变成十进制是多少? [Trident]

【解答视频序号:09090007】

10. 下面哪种写法会产生latch?为什么? [SIRF 2008]

|

always @(*)begin if(d) a = b; end |

always @(*)begin if(d) a = b; else a = a; end |

always @ (b or d) case(d) 2’b00: a=b>>1; 2’b11: c=b>>1; default: begin a=b; c=b; end endcase |

|

always @(b or d)begin a=b; c=b; case(d) 2’b00: a=b>>1; 2’b11: c=b>>1; endcase end |

always@(b or d)begin case(d) //synopsys full_case 2’b00: a=b>>1; 2’b11: c=b>>1; endcase end |

|

【解答视频序号:09090008】

11. 从仿真的角度设计测试32(bit)*32(bit)的乘法器能否正常工作的过程?

【解答视频序号:09110001】

12. 从仿真的角度设计测试1024-depth的SRAM能否正常工作的步骤或过程,功能:有10位的读写指针,并且读操作与写操作可以同时进行,负责读和写的部分由一个控制器控制。

【解答视频序号:09110002】

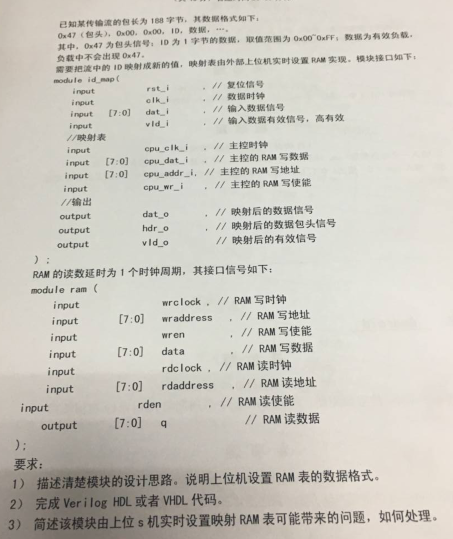

13. 报文替换ID的功能

【解答视频序号:09110003】

注意查看FPGA面试题《二》部分