|

如果同学们的问题我们帖子里面没有的请第一时间联系易老师微信同步:13112063618,我们对新问题进行补充!

明德扬最近做了抖音系列短视频,感兴趣可以关注明德扬抖音号:FPGA技巧分享(87481069842)至简书籍短视频(74803215644)

【问题9.1】 PCIE视频教程是否有讲简单的pio数据交互? 答:有此方面的内容。

答: 是的,都可以。

答:可能Windows自带的驱动也适配了卡,卸载驱动,然后用windriver生成驱动的安装。

答:不可以的。

答:可以的,正常安装即可

十、就业班项目-光纤项目

【问题10.1】光纤项目主要是培训内容是哪些接口? 本项目的工程也包括PCIE接口内容,但不会详细教授。

答:本项目是点对点通信,所以MDY使用GTX IP核后,封装了一层用户协议,这个用户协议是自定义的,参考了UDP协议的思想。

答:本项目的工程包括PCIE代码,但注意的是,虽然有PCIE代码,但文档资料以及教学内容都不包含此部分,即不教授PCIE的内容。 如果需要PCIE的学习内容,可以参考MDY的PCIE教程(注意,PCIE教程与光纤项目是完全独立的,内容没有任何相关性)。

答:光纤的IP核,有一个从外部时钟芯片过来的时钟,本项目中使用的是156.25M。通过该时钟,IP核产生给“用户侧”的时钟gtx_tx_clk,频率为156.25M。 同时,IP核会从LANE中恢复出接收时钟gtx_rx_clk,频率为156.25M。 注意,LANE那边是没有时钟线的。

答:该时钟是150Hhz。

答:该时钟是200M。

答:单独从光纤接口来说,光纤接口最多可以跑10G。但如果是4条光纤都跑10G的话,总带宽是40G,PCIE则只能跑20G,即进来的数量多,送给PC的少,这样是不行的。

答: 首先是项目需要2.5G的速率,所以光纤要跑2.5G。 其次,根据2.5G,从而推算出你的用户侧时钟和数据位宽,位宽*时钟频率=2.5G。例如,位宽为1,则意味着用户侧时钟2.5G,这不现实。 位宽为16位,则时钟频率是156.25M,这是比较正常的时钟;当然,你可以选位宽为32位,时钟频率则为78.125M,也是可以。

答:本项目的IP核,其内部是使用了aurora协议的,IP核已经实现了该协议的内容。 这里所说的“自定义协议”,是指IP核之外,由用户定义的用户层协议。例如接收侧,用户从IP核收到数据后,这里数据的定义是什么,则由用户确定的。

答:每路是2G左右

答:DDR是边存边读的,写满就丢弃。

【问题10.12】老师您好,高速光纤通信项目通过光纤接口进来的是什么数据,出去的又是什么数据呢? 答:项目背景是高速AD数据,出去的也是此数据。但其他我们不关心

答:请看问题11.7的答疑

答:课程网盘还没有这方面内容,串口控制是基础内容。您需要了解哪些问题,可以在交流群里沟通。

【问题10.15】问:使用同步码(charisk)有没有使用规则,或者有没有注意事项,要注意什么?

【问题10.17】光纤项目里的学员笔记,是用什么工具画的阿 答:VISIO画的

答:这个也有可能是硬件有问题,你使用ibert测试,排除硬件问题

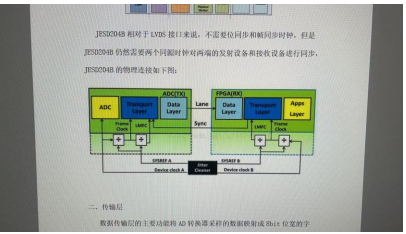

十一、就业班项目-精密仪器项目(JESD204B)

答:购买此课后,均加入MDY的专题课交流群。

本课程的交流群,将不会详细解答基础问题,例如VERILOG语法;自己修改的代码,如果出错,请自行定位。 对于协议、架构等,如有问题,MDY都会详细解答。

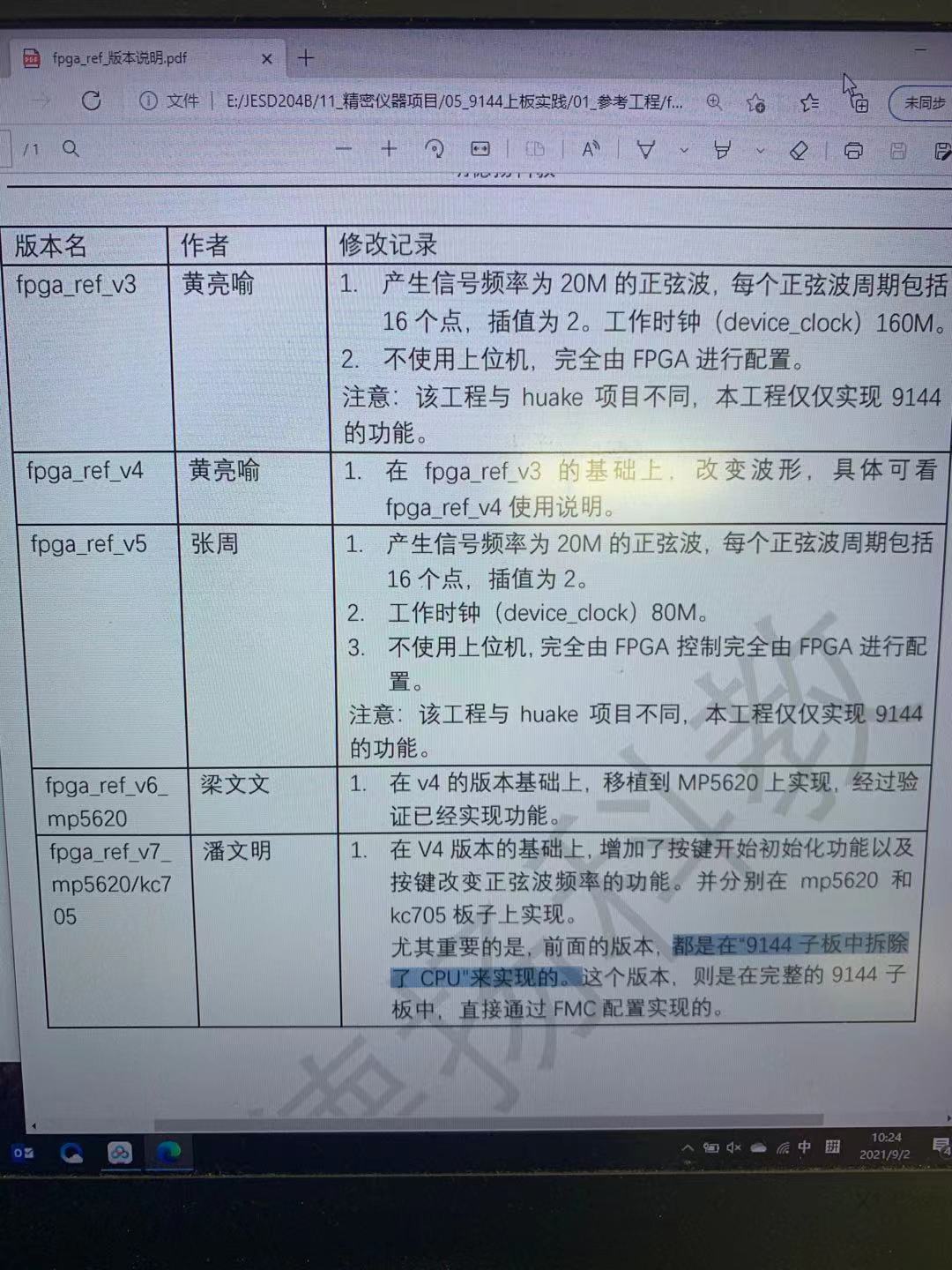

答:要使用AD9144成功,可以依次检查以下AD9144的几个寄存器。 地址OX470:该寄存器用于表示LANE有没有检测到K28.5同步字。如果说FPGA管脚配置错误、时钟有问题、LANE速率有问题 (例如双方配置的LANE速率不同,一端为2G,另一端为2.5G;或者信号质量不高,传输有误码等),则读到的值将不正确。 地址OX471:检查是否所有的LANE都已经同步。如果地址0X470正确,本寄存器不正确,则可能是速率、时钟有问题。 地址OX472:检查checksum,即校验和是否正确。如果说FPGA和AD9144的参数不同,或者是传递有错误,则此寄存器值不正确。 地址OX473: 检查ILAS。如果说此正确,基本上都正确了。

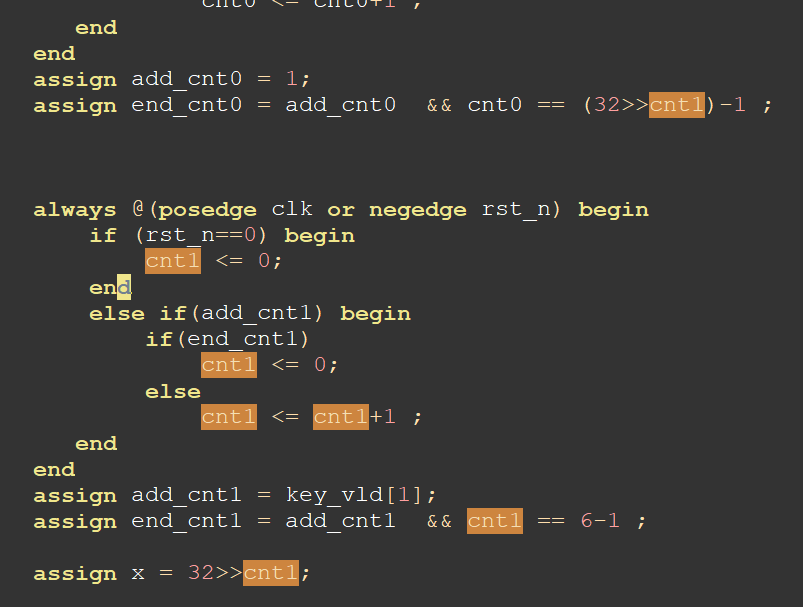

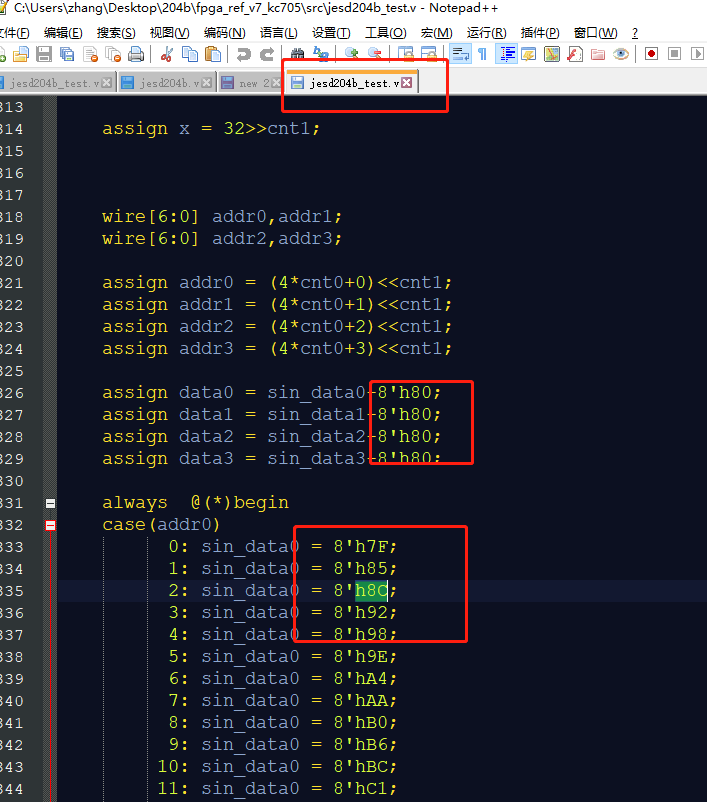

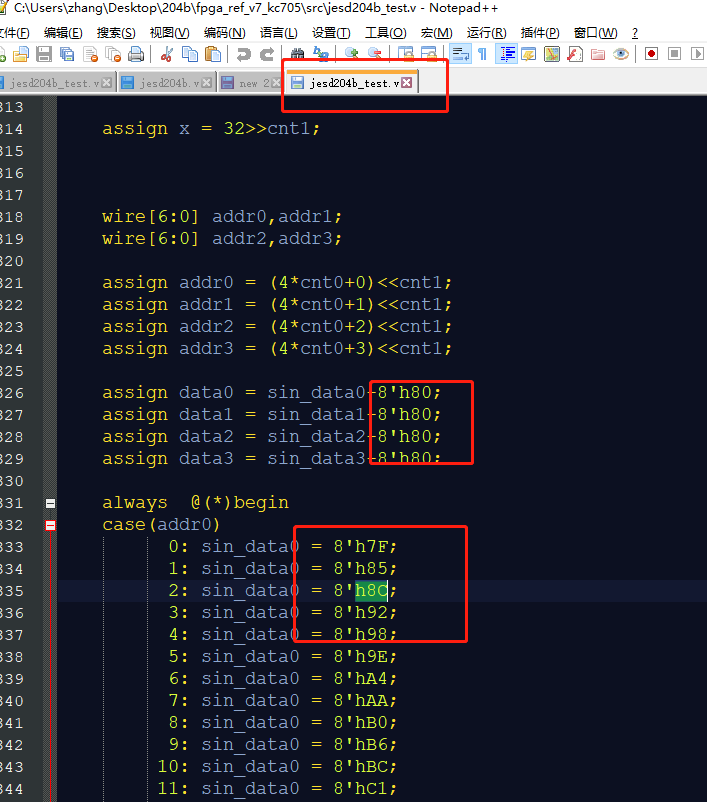

答: 本工程有一个功能,通过按下按键,可以改变信号的频率。工程一共支持6种频率,cnt1值为0~5,分别用来表示6种频率。 上面代码中的cnt0控制频率的,其是通过控制同一值重复的次数来达到控制频率的目的,例如假设某信号值为01234为100M信号频率, 让每个点重复一次,即0011223344,信号频率就变为50M。 cnt0的值根据cnt1来改变,例如当cnt1为0时,cnt0的值为0~31,当cnt1为1时,cnt0的值为0~15,当cnt2为2时,cnt0的值为0~7。

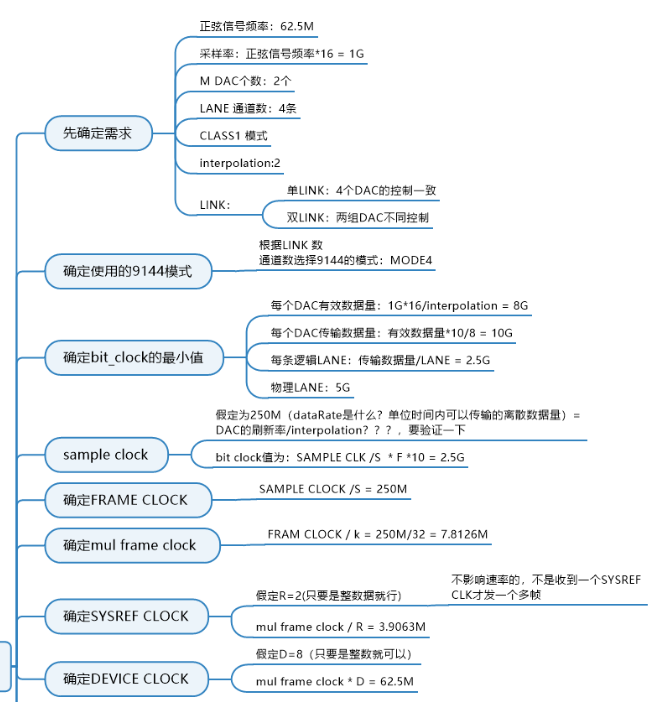

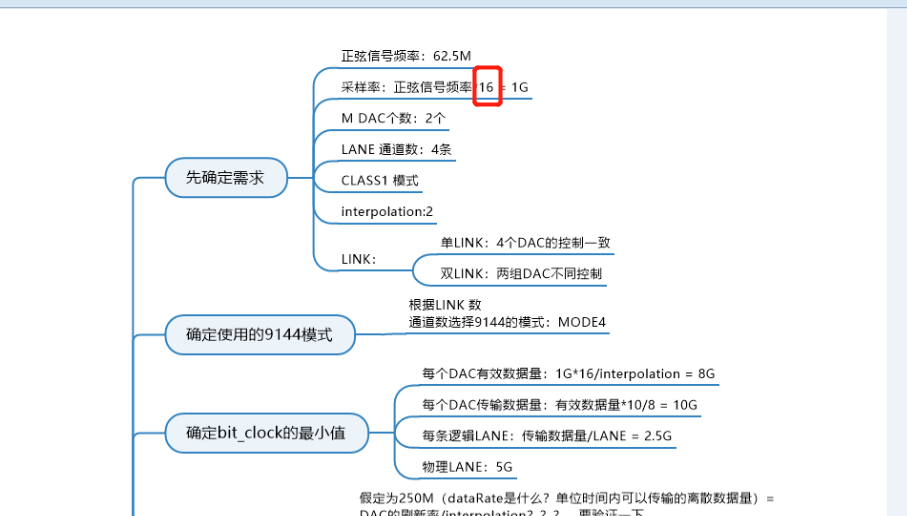

答: 如果要改变波形的频率,需要涉及到整个系统不同参数的调整,包括用于通信的lane的个数、时钟频率、IP核的寄存器配置和AD9144的寄存器配置等等。 具体可以参考视频中,具体应该按下图的步骤来分析:

上图中,依次是确定需求,即您希望的信号频率、采样率DAC个数分别是多少,然后据此确定需要多少条LANE;进而确定AD9144的配置;lane的 速率;sample时钟等等。本课程有对应的视频讲解,可以详细理解。请理解视频中介绍的思想,从而应用到您自己的项目中。 实用建议:建议您在我们提供的案例基础上,每次改动一点点,看到正确效果后,再做下一下,最终完成最终的目标。

【问题11.7】案例中,插值为2的意义?为什么要插值? 答:插值,顾名思义,就是在两个数据中间自动插入数据。例如要产生一个波形012345,不插值的情况下,FPGA必须要发送数据012345这几个 数据给AD9144;而在插值为2时,FPGA只需要发送0246数据,然后AD9144自动补充135。本案例中,为什么要使用插值为2,是假设的一种需求情况。

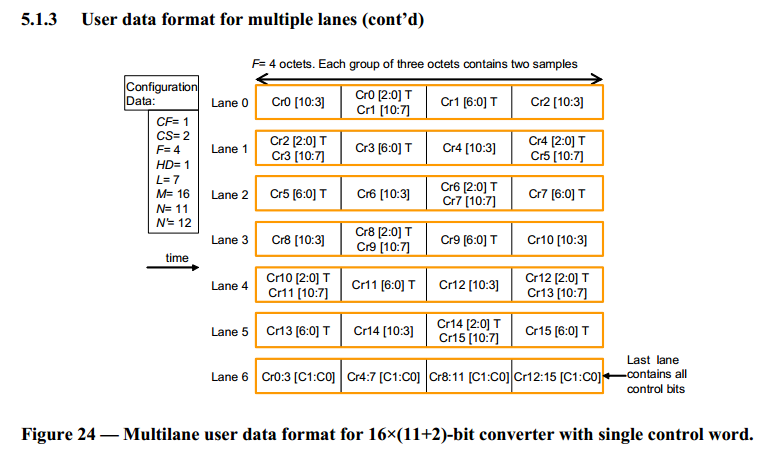

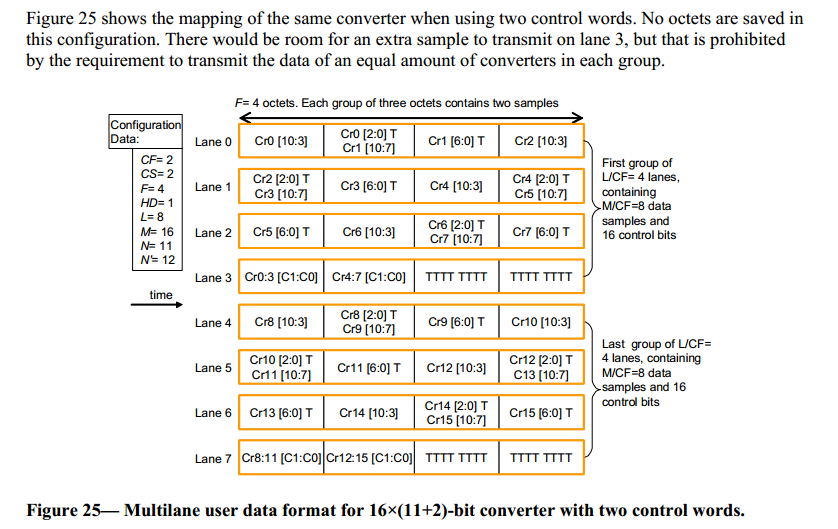

答:CS是指一个SAMPLE中的控制位比特数,上面两种情况,每个SAMPLE都加了2位的控制比特,即图中的C1和C0。 注意,图中的“Cr0:3[C1:C0]”,是指Cr0的[C1:C0]+Cr1的[C1:C0]+Cr2的[C1:C0]+Cr3的[C1:C0]。 CF是指一个FRAME CLK中的控制字个数,单位为字节。注意,这里的CF的限定条件是一个“FRAME CLK”。一个FRAME CLK,即上图中的一列数据。 从第一个图可以看出,第一列控制字是Cr0:3[C1:C0],共8比特,所以为CF=1。 从第二个图可以看出,第一列控制字是Cr0:3[C1:C0]和Cr8:11[C1:C0],一列共有16比特,所以CF=2

答:这里的16,是我们假设一个正弦波由16个采样点组成,所以由信号频率*16=采样频率。 当然,这里的16假设值,当您的正弦波是由32或者64,或者更大数组成时,当然就不同。我们这里是先确定需求。

答:都是需要配置完才能正常工作的。

答:1. 关于各个参数,如CS F M N等参数,在讲解确定需求的视频中,已经逐个分析出来。总的来说,是看AD9144文档,看MODE后,根据MODE所推荐的参数来配置。 2. 得到上面参数后,请阅读一下FPGA IP核的寄存器手册,很简单的,基本上是各个参数配上去就行了。 3. 配置代码,可以看代码解释视频,后面补充了。

答:寄存器中,“parameter range 1-256”,是指F这个参数的范围是1-256。但后面有描述,此寄存值的值 = F-1,所以才填为0。 这里描述有些歧义,但可以用这种方法排除:假设寄存器是1-256,那该寄存器是8位的,无法表示256,矛盾。

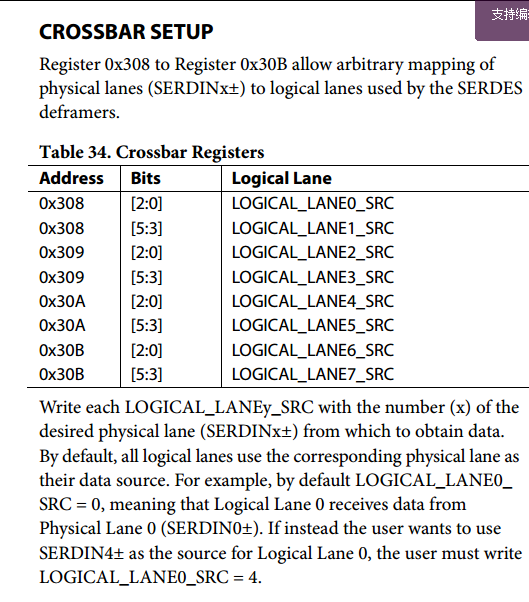

答:下面是这几个寄存器的相关描述。

首先,明确概念,SERDIN0~7指的是AD9144芯片上定义的管脚,是物理的,可以去看管脚图。LANE0~7,是指内部表示的LANE编号。 估计是为了灵活性,LANE0~7不是与SDRDIN0~7不是一个一个对应的,其对应关系是可以配置的,上面几个寄存器就是起这种作用。 例如,LANE0可以与SERDIN0对应,这个时候的0X308[2:0]=0,也可以和SERDIN4对应起来,这个时候0X308[2:0]=4。 其次,理解了上面关系后。你可以根据实际情况来配置,例如,本案例中的AD9144子板,它的SERDIN0~3是没有用的,只使用了SERDIN4~7,这是 固定死的。然后内部的配置,您可以使用LANE4~7来对应SERDIN4~7,也可以使用LANE0~3来对应SERDIN4~7,这由您来决定,都是可以实现的。 最后,再强调一下工程思维:芯片提供了很多功能,您用也可以,不用也可以,您会怎么做?你就选择最简单的来做,甚至就是忽视它存在,也就是使用默认值。

答:本课程只包括AD部分,并且是以AD9144为例来说明。注意不同AD和DA芯片,其使用方法都是不同的。本课程只讲述一般思路,需要学员举一反三使用。

答:在DA输出端如果16个点组成一个正弦波,插值为2的情况下,FPGA只需要传输8个点/正弦波。 如果FPGA传输16个点/正弦波,插值为2的情况下,DA输出端实际是32个点/正弦波。

答:LANE的速率,可以大于等于“需要的速率”,只要能保证传输即可。

答:专题课里有多个工程案例,实现的最高采样率是1Gbps。理论上,AD9144是可以实现2.8G的,但课程没有提供。

答:请去官网获取临时licensing,链接如下:https://www.xilinx.com/products/intellectual-property/ef-di-jesd204.html 选择:Evaluate ip选项,按提示操作即可。临时licensing,获取后,可以不联网,然后正常生成bit文件。 正式的licensing,需要购买,如果需要请向官方购买,MDY不提供正式licensing。至于临时和正式的区分,暂时未知,目前来说不影响学习用途。

答:可以使用。但注意,JESD204B的IP是临时licensing,具体请看问题11.19。

答:不一定,满足范围即可。在设置IP核时,有提示范围的。

答:官网licence的中心网址:https://www.xilinx.com/support/licensing_solution_center.html 这个license是跟机器绑定,需要客户自行到官网申请,MDY提供不了文件。

答:这个可以看txdata的视频讲解。

答:我们课程是只有发送的,没有接收的,不过接收方向的可以参考。

答:PHY只是接口传输作用,如果没有接口的话,那自然可以不用。目前没看到有这种使用场景。

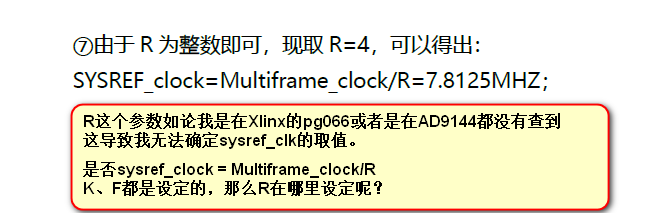

答:R值只要是整数都是可以的。所以这个时钟也可以等于Multiframe时钟,也是可以的。不用设置寄存器。

请问这里的拆除具体指的是什么?难道v3v4v5不能直接把9144fmc插到k7上就能用?要另外做什么硬件准备吗?

答:按照V7去做硬件即可。前面拆除是因为我们做项目时,就拿到一个拆除的硬件。

答:是可以这样理解,没有output delay的。

答:本课程定位为非基础课程,SPI时序属于基础设计。如果想了解SPI时序理论,可以百度相关内容,资料很丰富的。 如果想了解MDY的SPI是如何实现的,可以参考如下资料:http://old.mdy-edu.com/jishushipin/2019/1212/596.html, SPI内容在最后讲述。

答:本项目不需要时序约束,您描述的问题点也不清晰。

答:配台高级示波器,或者使用IBRT测试,具体的方法请百度。

答: 2. 由于都是一个FPGA发数据,按照JESD204B排列数据分配给各条LANE,这样就可以了。

答:该课程使用了IP核来实现

|

【问题11.33】是否包含有高速AD/DA的项目?最高速率是多少?有多少路?

答:激光工程项目中,包含有高速ADC AD9684,速率是500M,目前是支持一路的实现。

精密仪器项目中,包含有高速的DAC AD9144,目前实现的最高速率是1G,支持2路输出。

【问题11.34】精密仪器项目中,AD9144的AD测量范围,DA输出的范围,以及采样率分别是多少?

答:AD9144是一款DAC芯片,所以没有AD测量范围。DA采样率我们实现的是1G,实质可达1.8G。DA输出范围以及更多信息,请参考以下数据手册。

![]() AD9144-FMC-EBZ RevB Schematic.pdf (79.85 KB, 下载次数: 0)

AD9144-FMC-EBZ RevB Schematic.pdf (79.85 KB, 下载次数: 0) ![]() AD9144.pdf (2.79 MB, 下载次数: 0)

AD9144.pdf (2.79 MB, 下载次数: 0)

2020-11-4 10:55 上传

点击文件名下载附件

【问题11.35】JESD204B课程中,是那种并口高速adc用的那种协议么?

答:不是高速并行口,而是高速串行口,即SERDES接口来实现,单根线的速率可达到10G。

【问题11.36】就业班企业项目里视频拼接MIPI项目有用到IP核吗?需要额外交IP核费用吗?

答:MIPI项目是用的lattice芯片,lattice的此IP是免费的,学习此项目无需额外缴费。

【问题11.37】申请JESD的临时License提示不符合出口规定,有没有什么其它办法?

答:换了个企业邮箱账号就行了

【问题11.38】一,首先我得读9156寄存器,二,我的读9154{我自己的dac}三,用 dpg..现在dpg软件驶不了,麻烦解答一下

答:我们提供的例程,已集成在工程里面的,全部代码是FPGA代码。

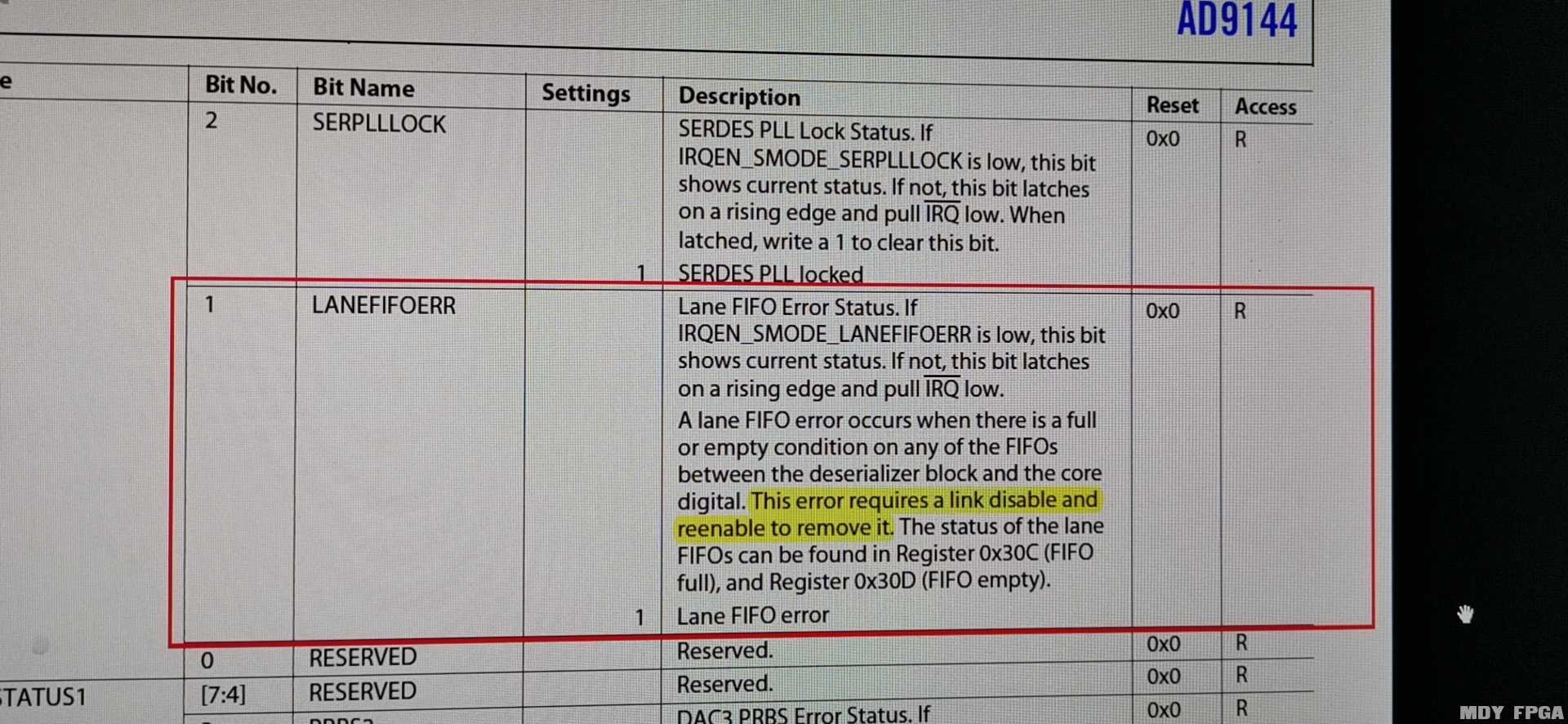

【问题11.39】请问9144用的是mose0,配置完后,CGS可以过,可以读到寄存器470是FF,8个lane都收到了k28.5,但是寄存器023的bit1一直在01之间不停的跳动,代表FIFO的读写一直有错误,查看30c和30d也能看到错误标记,

此时发送sysref的话,ILAS也能过,但是470,471,472,473都在不停的跳动,sync标记也是忽高忽低,此时链路不稳定,给tx核送数据,在频谱仪上能看到9144的输出,但是因为链路不稳定,输出会不停的闪烁,理论上讲,

链路稳定的话,470.471.472.473都应该回读FF才对,我想请教一下,是什么导致了9144配置完后fifo的读写标记一直报错呢?也就是寄存器023的bit 1

答:如果是自己做的硬件板,则有可能是硬件的稳定性问题。请检查硬件电路。

【问题11.40】请教一个问题,204b时序不行。12.5g,312.5M的核时钟。一个dac时序违例不严重能工作,另一个不行,怎么处理

答:解决时序违例,其思路是减少组合电路逻辑。如果确实无法减小,那就只能降低时钟频率了。您使用的315.5M是工作时钟的话,那确实是太高了,建议可以将工作时钟降为156.25M

【问题11.41】请问按键是有4位., 但代码中只使用了0位和1位, 这按键有没有顺序要求, 先按哪个再按哪个? 然后这个这个按键信号作为使能信号, 是只持续一个时钟, 还是需要一直为高?

答:先按启动有效的按键,再按改变频率的按键,具体请看使用说明。

【问题11.42】请问在给JESD204C IP核配置的时候,读取0x020 RESET寄存器的值,读到的值是0x081,说明这个IP一直处于复位状态,无法从复位状态退出,可能是什么问题呢?

答:检查一下所有的时钟和复位信号,一般都是跟这些信号有关

【问题11.43】请问FPGA中的204B IP核,其配置是在哪里定义?

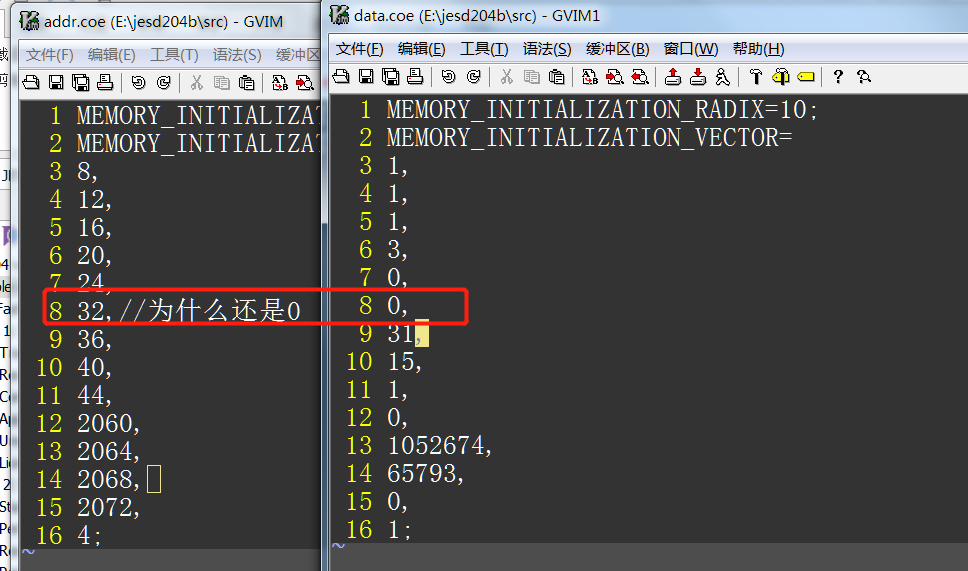

答:JESD204B的IP核配置,其地址在addr.coe文件中定义;其寄存器值在data.coe文件中定义。

【问题11.44】device clock是什么意思?

答:可以认为是AD9516给FPGA的一个多帧时钟,用于同步多帧的,可以认为D个多帧就发一个上升沿,这样就好同步了。具体有一个视频,可以看JESD204B协议04_实践_协议各个时钟的关系。

【问题11.45】:课程提供的上位机软件是直接和dac连接用于检测dac里寄存器的值吗?还是dac通过传数据到fpga通过fpga连接呢?

答:做法1:上位机将寄存器配置值写到FPGA,FPGA再写到DAC里。

做法2:FPGA内部有配置表,上电后自动配置DAC的寄存器。 以上两种方法都有。

【问题11.46】:如果是通过fpga连接的,是走的uart还是ethernet呢?

答:走的是网口。

【问题11.47】:vc707可不可以兼容我们的程序?

答:只要有HPC接口的,均支持

【问题11.48】:是不是地址8的ILA support设为1就代表在CGS之后开启ILAS的功能?

答:该地址设为1,表示启动ILA功能,设为0表示不启用。

【问题11.49】:地址20的ILA multiframe是选择ILAS一共发送几组8位数据?我们设为3就代表发送4组8位数据?

答:这里不是以8位数据为音位,而是multiframe为单位。所以设为3,表示发送4个多帧数据。

【问题11.50】:地址2060和2072的ILA config data 3 和 6 功能似乎是Sets the values to be transmitted in the ILA sequence for all lanes. 这两个寄存器是用于设置ILAS发送的数据吗?

两个寄存器都是0那发送的ILAS是全0,还是某个默认值?我看到网上有说是k28.0到k28.4顺序发送的,但我看我的一个TI的dac好像默认是0x1C也就是K28.0

答:这里是设置需要的L、BID、LID和DID等参数。从字面上理解,发送方向就会把这些数据当成ILA数据发给对端。按真实要求配置即可。设了什么值,就会打包成对应数据发送给对端。至于如何打包,我这还没有研究。

【问题11.51】:multiframe包含几个frame?

答:这个每个工程不同,是可以灵活设计的参数,并且是与时钟频率、其他参数相关联的。

【问题11.52】:BID这些参数具体就要从DAC那边找到对应的然后两边匹配就可以了,是吗?

答:BID DID 这些,两边匹配即可。

【问题11.53】麻烦问一下这个sin_data数据是怎么来的?自己造的数据吗?

答:sin_data是正弦波的数据,该正弦波数据用matlab产生,模块这里是转化成verilog语言后的。

【问题11.54】减得那个8'h80是什么意思呢?为什么要减那个8'h80呢?

答:如图红色波形所示,该正弦波数据用8bit位宽表示,0~8'hff是它的幅度值范围,中间的幅度值为8'h7f。 而在工程需求里,接口要求输出的正弦波数据为补码形式,那么正弦波的补码波形如图蓝色波形所示,

补码表示的最高点数值为8'h7f,最低点数值8'h80。对于数值8'h80+1=8'h01,8'h80-1=8'h7f,那么将正弦波数据sin_data-8'h80得到的就是如图蓝色的波形数据,也是一个补码的数据。

【问题11.55】问题:请问jesd204 phy能选择具体某一个quad吗?具体如何选?

答:JESD204 PHY是可以选择QUAD的,在IP核界面里可以选择使用哪个,具体可以教程里的视频

【问题11.56】JESD204B课程是ADC采样,还是DAC采样?(模数转换是ADC,数模转换是DAC)

答:是DAC采样

【问题11.57】Jesd204B那个项目里的以太网通信是不是没有调用MAC ip核,自己写的

答:是的。该代码没有调用IP核,纯RTL实现,模块名为gmii

【问题11.58】fmcAD9144模块从jp2送入AD9516的时钟信号需要多大幅值的?1.8V够吗?

答:一般JP2的时钟幅值为1.5V。1.8V也是可以的

【问题11.59】问:我JESD204B ADC接受的数据全是0咋回事?

答:

1. 确认接收到了数据?

2. 基于1后,再确认是 0

【问题11.60】问:这个sysref信号必须由外部提供吗?我们板子没有这个信号,能不能用device clk这个信号分频得到?

答;这里的核心思想是:

1.时钟要稳定;

2. 两边都是完全同频同步的时钟

【问题11.61】问:老师我想问一下jesd项目里的9516和9144的配置视频里讲的是通过ACE工具和上位机软件配置的,那vivado程序中又有配置模块,这是怎么回事?

答:前期工程是由上位机配置的,后面提供的工程 由内部模块配置的