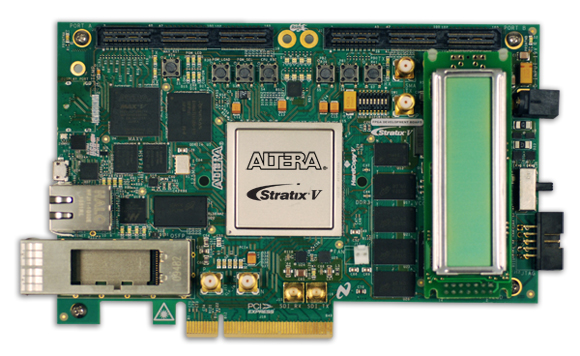

Stratix V GX FPGA 开发板

介绍:Stratix ® V GX FPGA 开发套件提供了一个完整的设计环境,其中包括您立即开始开发 FPGA 设计所需的所有硬件和软件。

您可以使用此开发套件执行以下操作:

- 1.使用符合 PCIe 短卡外形规格的开发板以高达 Gen3 的数据速率开发和测试 PCI Express ® (PCIe ® ) 设计

- 2.为 DDR3、QDR II+ 或 RLDRAM II 存储器开发和测试存储器子系统

- 3.使用高速夹层卡 (HSMC) 连接器连接到合作伙伴提供的超过 35 种不同 HSMC 之一,支持协议,例如 Serial RapidIO ®、10 Gbps 以太网、SONET、CPRI、OBSAI 等

开发套件内容:

-

1.特色设备:

-

Stratix V GX FPGA:5SGXEA7K2F40C2N

-

-

-

2.配置、状态和设置元素

-

JTAG

-

板载 USB-Blaster TM II 电缆

-

通过 MAX ® V 器件和闪存实现快速无源并行 (FPP) 配置

-

一个重置配置按钮

-

一个 CPU 复位按钮

-

两个配置按钮

-

-

3.时钟

-

-

50 MHz、125 MHz、100 MHz 和 148.5 MHz 可编程振荡器

-

SMA 输入 (LVPECL)

-

-

4.一般用户输入和输出

-

10/100/1000Mbps 以太网 PHY (SGMII),带 RJ-45(铜)连接器

-

16x2 字符 LCD

-

一个 8 位双列直插 (DIP) 开关

-

十六个用户 LED

-

三个用户按钮

-

-

5.存储设备

-

DDR3 SDRAM(1,152 MB,x72 位宽)

-

QDR II+ SRAM(4.5 MB,2 Mb x18 位宽)

-

占用空间与 QDR II 4 Mb x18 位宽兼容

-

RLDRAM II(具有 18 位数据总线的 72 MB CIO RLDRAM II)

-

-

6.组件和接口

- JTAG

- 板载 USB-Blaster TM II 电缆

- 通过 MAX ® V 器件和闪存实现快速无源并行 (FPP) 配置

- 一个重置配置按钮

- 一个 CPU 复位按钮

- 两个配置按钮

- 50 MHz、125 MHz、100 MHz 和 148.5 MHz 可编程振荡器

- SMA 输入 (LVPECL)

- 10/100/1000Mbps 以太网 PHY (SGMII),带 RJ-45(铜)连接器

- 16x2 字符 LCD

- 一个 8 位双列直插 (DIP) 开关

- 十六个用户 LED

- 三个用户按钮

- DDR3 SDRAM(1,152 MB,x72 位宽)

- QDR II+ SRAM(4.5 MB,2 Mb x18 位宽)

- 占用空间与 QDR II 4 Mb x18 位宽兼容

- RLDRAM II(具有 18 位数据总线的 72 MB CIO RLDRAM II)

-

-

- PCIe x8 边缘连接器

- 两个 HSMC 连接器

- SMB 用于串行数字接口 (SDI) 输入和输出

- QSFP光笼

- 10/100/1000Mbps 以太网 PHY (SGMII),带 RJ-45(铜)连接器

-

7.力量

- 笔记本电脑直流输入

- PCIe 边缘连接器

- Nios ® II 处理器网络服务器和远程系统更新

- 8.环回和调试 HSMC 卡

- 9.电源适配器和电缆

-

10.Stratix V GX FPGA 开发套件软件内容

- 完整的文档

-

用户指南

参考手册/电路板原理图和布局设计文件